半导体设计公司新思科技 (Synopsys) 17 日宣布,将与晶圆代工龙头台积电合作推出针对高效能运算 (High Performance Compute) 平台的创新技术,而这些新技术是由新思科技与台积电合作的 7 纳米制程 Galaxy 设计平台的工具所提供。

2016-10-18 10:55:37 1097

1097 新思科技接口和基础 IP 组合已获多家全球领先企业采用,可为 ADAS 系统级芯片提供高可靠性保障 摘要: 面向台积公司N5A工艺的新思科技IP产品在汽车温度等级2级下符合 AEC-Q100 认证

2023-10-23 15:54:07 1964

1964 智融的估值尚未最终确定。 芯原股份目前持有芯来智融2.99%股权,通过本次交易拟取得芯来智融全部股权或控股权。本次交易的具体交易方式、交易方案等内容以后续披露的重组预案及公告信息为准。 消息称台积电加速 1.4nm 先进工艺

2025-08-29 11:28:48 1921

1921 台积电0.18工艺电源电压分别是多少?是1.8v跟3.3v吗?

2021-06-25 06:32:37

采用0.13um的混合工艺 模拟设计中用到的MOS的栅长选择就是0.13um吗? / C5 @, o6 U8 I% q! X而如果采用0.18um的混合工艺 模拟设计中用到的MOS的栅长选择就是0.18um吗?

2012-01-12 16:33:54

量;某知名社交电商平台使用后减少了50%以上跨语言调用接口代码量;某图像处理软件所有C++代码复用通过AKI来实现。使用AKI后这些项目不仅减少了项目代码量,还显著优化了代码复用与迁移流程。

目前

2025-01-02 17:08:58

各类常用工艺库台积电,中芯国际,华润上华

2015-12-17 19:52:34

Kochpatcharin表示:“台积公司与新思科技等开放创新平台(OIP)合作伙伴紧密合作,助力我们的客户在执行定制及模拟模块的工艺制程设计迁移时,提高生产效率并加快设计收敛。现在,通过全新的新思科技AI驱动型模拟设

2023-04-03 16:03:26

的必经前提步骤,而先进的制成工艺可以更好的提高中央处理器的性能,并降低处理器的功耗,另外还可以节省处理器的生产成本。 “芯片门”让台积电备受瞩目 2015年12月份由台积电举办的第十五届供应链管理论

2016-01-25 09:38:11

DevEco Studio支持打开两个远程模拟器,演示跨设备迁移吗?

2022-06-07 10:02:55

ADRV9375-W/PCBZ:模拟设备公司宽带2600MHz匹配板详解在现代无线通信中,宽带信号处理和高性能射频前端是实现高效数据传输的关键。ADRV9375-W/PCBZ 是由 模拟设备公司

2024-10-06 16:44:02

台积电率先量产40纳米工艺

台积电公司日前表示,40纳米泛用型(40G)及40纳米低耗电(40LP)工艺正式进入量产,成为专业集成电路制造服务领域唯一量产40纳米工艺的公司

2008-11-22 18:27:07 1112

1112 Exar选择微捷码Titan ADX来加速模拟设计

芯片设计解决方案供应商微捷码(Magma(r))设计自动化有限公司(纳斯达克代码:LAVA)日前宣布,Exar公司已

2009-12-10 09:48:02 1028

1028 台积电又跳过22nm工艺 改而直上20nm

为了在竞争激烈的半导体代工行业中提供最先进的制造技术,台积电已经决定跳过22nm工艺的研

2010-04-15 09:52:16 1210

1210 知名芯片设计厂商ARM公司日前与台积电公司签订了一份为期多年的新协议,根据该协议,双方将就使用台积电的FinFET工艺制造下一代64bit ARM处理器产品方面进行合作。

2012-07-24 13:52:57 1172

1172 ,采用台积公司先进的16纳米FinFET (16FinFET)工艺打造拥有最快上市、最高性能优势的FPGA器件。

2013-05-29 18:21:14 1246

1246 为专注于解决先进节点设计的日益复杂性,全球电子设计创新领先企业Cadence设计系统公司(NASDAQ:CDNS) 今天宣布,台积电已与Cadence在Virtuoso定制和模拟设计平台扩大合作以设计和验证其尖端IP。

2013-07-10 13:07:23 1201

1201 台积公司透过遍及全球的营运据点服务全世界半导体市场。台积公司立基台湾,目前拥有三座最先进的十二吋晶圆厂、五座八吋晶圆厂以及一座六吋晶圆厂。本文介绍了台积电股票代码、台积电是一家怎样的公司以及台积电核心价值。

2018-01-08 09:23:25 78181

78181 不过,台积电带动的半导体产业群聚效益相当显著,今年已有来自全球各地的多家重量级半导体设备厂加速在台布局,包括美商应材、科林研发、德商默克、日商艾尔斯(RS Technologies)及荷商艾司摩尔(ASML)等,凸显这些大厂都看好台积电技术优势,全力助攻台积电发展先进制程。

2018-07-25 15:56:00 4141

4141

本手册描述如何使用VieloSo模拟设计环境来模拟模拟设计。VieloSo模拟设计环境被记录在一系列在线手册中。下面的文件给你更多的信息。 FieloSo高级分析工具用户指南提供有关蒙特卡洛、优化和统计分析的信息。

2018-09-20 08:00:00 0

0 在此联盟之中,台积电将提供晶圆共乘(CyberShuttle)服务给东京大学工程学院的系统设计实验室(Systems Design Lab, d.lab),该实验室亦将采用台积公司的开放创新平台虚拟设计环境(VDE)进行晶片设计。

2019-11-29 09:54:54 3111

3111 台积电从原来的晶圆制造代工角色,逐步跨界至封测代工领域(InFO、CoWoS及SoIC等封装技术),试图完整实体半导体的制作流程。

2020-02-25 17:18:14 4256

4256

“台积电5nm产品已投入批量生产,明年量产4nm产品,计划2022年实现3nm量产,所有的IC都需要半导体先进的封装技术,而绿色制造、打造绿色企业是我们的永久使命,” 台积电(南京)有限公司总经理罗镇球在2020世界半导体大会上介绍了台积电先进工艺的演进之路,并表达了企业愿景。

2020-09-10 13:48:44 2294

2294 重点 ● TSMC认证基于新思科技3DIC Compiler统一平台的CoWoS和InFO设计流程 ● 3DIC Compiler可提高先进封装设计生产率 ● 集成Ansys芯片封装协同分析解决方案

2020-10-14 11:11:21 2813

2813 12 月 29 日消息,据国外媒体报道,台积电近几年在芯片制程工艺方面走在行业前列,7nm 及 5nm 工艺都是率先量产,良品率也相当可观,先进的工艺也使他们获得了苹果、AMD 等公司的芯片代工订单

2020-12-29 15:03:19 2056

2056 很显然,这一波儿的竞争Intel是要落后AMD的,而后者起来的其中一个原因是台积电先进的工艺制程,而Intel正在酝酿新的调整,并以此追上。

2021-01-10 11:20:20 3336

3336 新思科技与三星基于Fusion Design Platform开展合作,充分释放三星在最先进节点工艺的优势 经过认证的流程为开发者提供了一整套针对时序和提取的业界领先数字实现和签核解决方案 新思科

2021-01-13 16:01:18 2414

2414 在台积电昨日最新举办的法人说明会上,多位台积电高管分享台积电2021年资本支出计划,透露台积电N3、3D封装等先进工艺研发情况,并公布台积电2020年第四季度营收情况。

2021-01-15 10:33:39 2814

2814 1 月 15 日消息,据国外媒体报道,在苹果转向 5nm,华为无法继续采用台积电的先进工艺代工芯片之后,台积电 7nm 的产能,也就有了给予其他厂商更多的可能,去年下半年 AMD 获得的产能

2021-01-15 11:27:28 3373

3373 领先的移动和汽车SoC半导体IP提供商Arasan Chip Systems今天宣布,用于台积公司22nm工艺技术的eMMC PHY IP立即可用 加利福尼亚州圣何塞2021年1月21日 /美通社

2021-01-21 10:18:23 3344

3344 台积电的2020年财报令人瞩目,总营收创历史新高。作为全球芯片代工的龙头,台积电把持着全球最先进的处理器制造工艺,其中包括代生产了苹果的A系列芯片,华为海思麒麟高端系列的芯片等等,对于整个芯片制作流程也都是十分熟悉的。那么,与其把蛋糕分几杯羹,为什么台积电不自己独享一份呢?

2021-04-02 14:55:27 9142

9142 什么是HarmonyOS“跨设备迁移”? HarmonyOS“跨设备迁移”是指将承载业务的Page在同一用户的不同设备间迁移,以便支持用户业务无缝切换的诉求。“跨设备迁移”实现了业务跨设备流转功能

2021-06-25 17:32:14 6531

6531 新思科技3DIC Compiler是统一的多裸晶芯片设计实现平台,无缝集成了基于台积公司3DFabric技术的设计方法,提供完整的“探索到签核”的设计平台

2021-11-01 16:29:14 703

703 通过与台积公司在早期的持续合作,我们为采用台积公司先进的N3制程技术的设计提供了高度差异化的解决方案,让客户更有信心成功设计出复杂的SoC。

2021-11-02 09:24:25 687

687 的设计方法, 为客户提供完整的“初步规划到签核”的设计平台 此次合作将台积公司的技术进展与3DIC Compiler的融合架构、先进设计内分析架构和签核工具相结合,满足了开发者对性能、功耗和晶体管数量密度的要求 新思科技(Synopsys)近日宣布扩大与台积公司的战略技术合作

2021-11-05 15:17:19 6382

6382 新思科技平台提供强化功能,以支持台积公司N3和N4制程的新要求 新思科技Fusion设计平台能够提供更快的时序收敛,并确保从综合到时序和物理签核的全流程相关性 ,可显著提高生产力 新思科

2021-11-16 11:06:32 2326

2326 双方共同推出的工艺设计套件和经认证参考流程可加速高性能汽车、边缘人工智能和5G SoC的开发 全球半导体制造领先企业GlobalFoundries(GF)联合新思科技(Synopsys)近日宣布

2021-11-17 14:38:41 2386

2386 根据外媒的消息报道称,台积电公司目前正在加大先进封装投资力度,目前已将旗下CoWoS 封装业务的部分流程外包分给了OSAT,此前台积电还公布了最新强化版的CoWoS封装工艺。

2021-11-25 17:38:58 2472

2472 解决方案能够实现全面的数据可视化和AI自动优化设计,助力提高先进节点的芯片设计生产力。该解决方案将为所有开发者提供实时、统一、360度视图,以加快决策过程,通过更深入地了解运行、设计、项目之间的趋势来加强芯片的开发协作。

2022-06-02 16:09:44 3237

3237 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,其数字和定制 / 模拟设计流程已获得 TSMC N3E 和 N4P 工艺认证,支持最新的设计规则手册(DRM)。

2022-06-17 17:33:05 6035

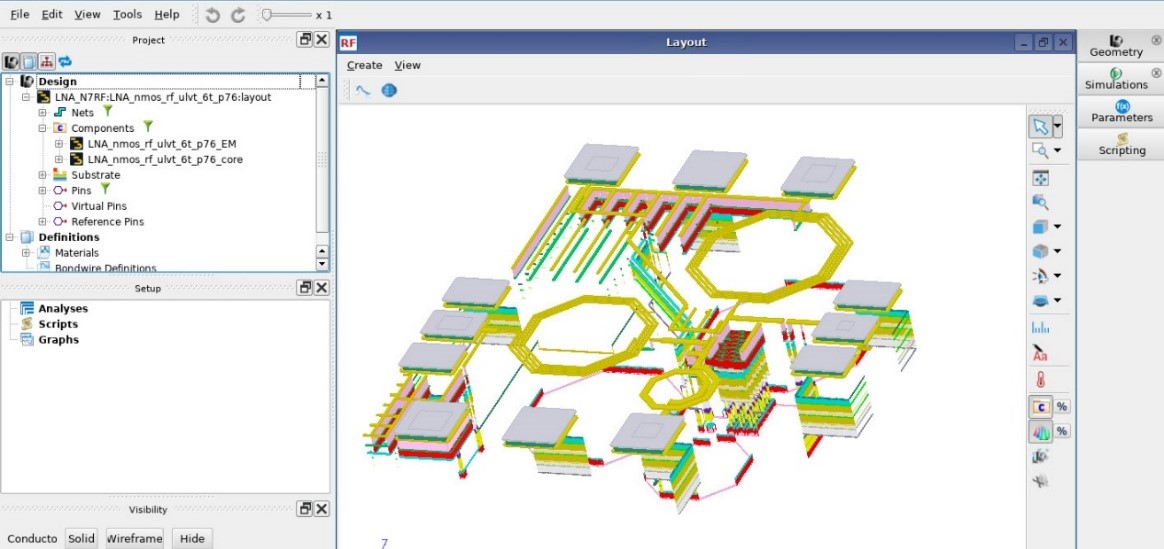

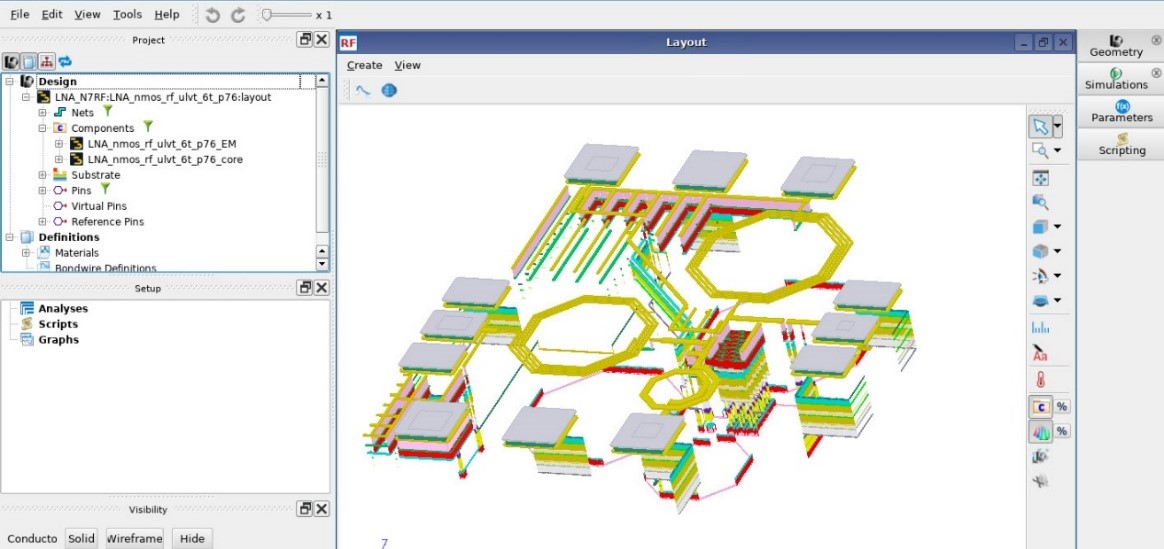

6035 新思科技(Synopsys)近日推出面向台积公司N6RF工艺的全新射频设计流程,以满足日益复杂的射频集成电路设计需求。

2022-06-24 14:30:13 1700

1700 来源:是德科技 PathWave RFPro 与新思科技定制化编译器相辅相成,可提供无线晶片设计工作流程所需的整合式电磁模拟工具 是德科技(Keysight Technologies Inc.

2022-06-27 14:41:38 1276

1276

新思科技数字和定制设计流程获得台积公司的N3E和N4P工艺认证,并已推出面向该工艺的广泛IP核组合。

2022-07-12 11:10:51 1780

1780 此前,有媒体报道称台积电将于2023年提高先进工艺技术的价格。据报道,根据不同的工艺,价格上涨幅度一般在6%-9%左右。据报道,台积电将在与客户协商后将上调幅度修改为3%,成熟流程将上调6%。

2022-09-29 11:11:39 1242

1242 中国上海,2022 年 10 月 27 日 —— 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,Cadence 数字和定制/模拟设计流程已获得台积电最新 N4P 和 N3E

2022-10-27 11:01:37 2274

2274 ,纳斯达克股票代码:SNPS )近日宣布,得益于与台积公司的长期合作,新思科技针对台积公司N3E工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的

2022-11-08 13:37:19 1951

1951 工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的基础IP、接口IP组合已经在台积公司N3E工艺上实现了多项成功流片,助力合

2022-11-10 11:15:22 1158

1158 为满足5G/6G SoC对性能和功耗的严苛需求,新思科技(Synopsys,Inc.,纳斯达克股票代码:SNPS)、Ansys和是德科技近日宣布,推出针对台积公司16纳米精简型工艺技术(16FFC

2022-11-16 16:24:19 1294

1294 工艺技术的2D/2.5D/3D多裸晶芯片系统。基于与台积公司在3DFabric™技术和3Dblox™标准中的合作,新思科技提供了一系列全面的、系统级的、经过产品验证的解决方案,助力共同客户能够满足复杂的多裸晶芯片系统对于功耗和性能的严苛要求。

2022-11-16 16:25:43 1653

1653 新思科技(Synopsys, Inc.)近日宣布,推出全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N3工艺技术的2D/2.5D/3D多裸晶芯片系统。基于与台积公司在

2022-12-01 14:10:19 990

990 )设计流程是双方合作中的亮点之一 新思科技(Synopsys)近日宣布,连续第12年被评选为“台积公司OIP开放创新平台年度合作伙伴”(OIP,Open Innovation Platform)并斩获六个奖项,充分彰显了双方长期合作在 多裸晶芯片系统、 加速高质量接口IP、射频设计、云解决方案

2022-12-14 18:45:02 1338

1338 摘要: 新思科技连续12年被评为“台积公司OIP年度合作伙伴” 该合作推动了多裸晶芯片系统的发展和先进节点设计 奖项涵盖数字和定制设计、IP、以及基于云的解决方案 推出毫米波(mmWave)射频

2022-12-15 10:48:45 542

542

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布推出基于 Cadence Virtuoso Design Platform 的节点到节点设计迁移流程,能兼容所有的台积电先进节点

2023-05-06 15:02:15 1934

1934 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,Cadence 数字和定制/模拟设计流程已通过 TSMC N3E 和 N2 先进工艺的设计规则手册(DRM)认证。两家公司还发

2023-05-09 10:09:23 2046

2046 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布与台积电携手,针对台积电 N16 工艺 79GHz 毫米波设计参考流程,优化 Cadence Virtuoso 平台

2023-05-09 15:04:43 2317

2317 为了不断满足新一代系统单晶片(SoC) 的严格设计目标,新思科技在台积电最先进的 N2 製程中提供数位与客製化设计 EDA 流程。相较於N3E 製程,台积公司N2 製程採用奈米片(nanosheet

2023-05-11 19:02:35 3061

3061 针对台积公司16FFC的79GHz毫米波射频设计流程加速自动驾驶系统中射频集成电路的开发。 新思科技、Ansys和是德科技近日宣布,推出针对台积公司16纳米精简型工艺技术(16FFC)的全新

2023-05-17 05:45:01 878

878

股票代码:SNPS)近日宣布,携手台积公司和Ansys持续加强多裸晶芯片系统设计与制造方面的合作,助力加速异构芯片集成以实现下一阶段的系统可扩展性和功能。得益于与台积公司在3DFabric™技术和3Dblox™标准中的合作,新思科技能够为台积公司先进的7纳米、5纳米和3纳米工艺技

2023-05-17 15:43:06 450

450 3DFabric™技术和3Dblox™标准中的合作,新思科技能够为台积公司先进的7纳米、5纳米和3纳米工艺技术上的多裸晶芯片系统设计,提供业界领先的全方位EDA和IP解决方案。台积公司先进工艺技术集成

2023-05-18 16:04:08 1365

1365 三家全球领先公司紧密协作,以应对 基于台积公司先进技术的设计在芯片、封装和系统等方面的挑战。 新思科技近日宣布,携手台积公司和Ansys持续加强多裸晶芯片系统设计与制造方面的合作,助力加速异构芯片

2023-05-22 22:25:02 874

874

新思科技一直与台积公司保持合作,利用台积公司先进的FinFET工艺提供高质量的IP。近日,新思科技宣布在台积公司的N3E工艺上成功完成了Universal Chiplet Interconnect

2023-05-25 06:05:02 1446

1446 面向三星8LPU、SF5 (A)、SF4 (A)和SF3工艺的新思科技接口和基础IP,加速先进SoC设计的成功之路 摘要: 新思科技接口IP适用于USB、PCI Express、112G以太网

2023-06-30 13:40:14 728

728 内容提要 1 轻松实现节点到节点的设计和 layout 迁移 2 将定制/模拟设计迁移速度提升 2 倍 3 Cadence Virtuoso Studio 针对所有 Samsung Foundry

2023-07-04 10:10:01 1516

1516 的“耳目”。 新思科技一直走在芯片监控解决方案的前沿,而这些解决方案是新思科技芯片生命周期管理(SLM)系列的一部分。最近, 新思科技在台积公司N5和N3E工艺上完成了PVT监控IP测试芯片的流片 。这是一个里程碑式的成功。从此,那些准备在这些先进节点

2023-07-11 17:40:01 1827

1827 技的解决方案可在英特尔代工服务提供的制程工艺上实现安全且先进的微电子技术开发 新思科技(Synopsys)近日宣布,其搭载了Synopsys.ai全栈式AI驱动型EDA解决方案的数字和定制设计流程已经通过英特尔代工服务(IFS)的Intel 16制程工艺认证,以助力简化功耗和空间受限型应用

2023-08-07 18:45:03 1186

1186 基于台积公司N3E工艺技术的新思科技IP能够为希望降低集成风险并加快首次流片成功的芯片制造商建立竞争优势

2023-08-24 17:37:47 1737

1737 新思科技经认证的多裸晶芯片系统设计参考流程和安全的Die-to-Die IP解决方案,加速了三星SF 5/4/3工艺和I-Cube及X-Cube技术的设计和流片成功。 新思科技3DIC

2023-09-14 09:38:28 1995

1995 流程,能兼容所有的 TSMC(台积电)先进节点,包括最新的 N3E 和 N2 工艺技术。 这款生成式设计迁移流程由 Cadence 和 TSMC 共同开发,旨在实现定制和模拟 IC 设计在 TSMC

2023-09-27 10:10:04 1633

1633 《半导体芯科技》编译 来源:EENEWS EUROPE 新思科技(Synopsys)表示,其客户已在台积电2nm工艺上流片了多款芯片,同时对模拟和数字设计流程进行了认证。 新思科技表示,台积电2nm

2023-10-08 16:49:24 930

930 的生产力 基于 AI 驱动的 Virtuoso Studio 的定制/模拟流程支持电路优化,功能经过增强,可将设计迁移吞吐量提升 3 倍 双方的共同客户正在积极使用 N2 PDK 来开发 AI、大规模计算

2023-10-10 16:05:04 1331

1331 。 Synopsys.ai™ EDA解决方案中的模拟设计迁移流程可实现台积公司跨工艺节点的快速设计迁移。 新思科技接口IP和基础IP的广泛产品组合正在开发中,将助力缩短设计周期并降低集成风险。 加利福尼亚州桑尼维尔, 2023 年 10 月 18 日 – 新思科技(Synopsys, I

2023-10-19 11:44:22 918

918 新思科技近日宣布,其数字和定制/模拟设计流程已通过台积公司N2工艺技术认证,能够帮助采用先进工艺节点的SoC实现更快、更高质量的交付。新思科技这两类芯片设计流程的发展势头强劲,其中数字设计流程已实现

2023-10-24 16:42:06 1394

1394 新思科技(Synopsys, Inc.)近日宣布,面向台积公司N5A工艺推出业界领先的广泛车规级接口IP和基础IP产品组合,携手台积公司推动下一代“软件定义汽车”发展,满足汽车系统级芯片(SoC)的长期可靠性和高性能计算需求。

2023-10-24 17:24:56 1692

1692 摘要: 全新参考流程针对台积公司 N4PRF 工艺打造,提供开放、高效的射频设计解决方案。 业界领先的电磁仿真工具将提升WiFi-7系统的性能和功耗效率。 集成的设计流程提升了开发者的生产率,提高了

2023-10-30 16:13:05 902

902 计 新思科技携手Ansys 和 Keysight 共同推出全新射频设计参考流程,能够为现代射频集成电路设计提供完整解决方案 新思科技(Synopsys)近日宣布,其模拟设计迁移流程已应用于台积公司N4P、N3E 和 N2 在内的多项先进工艺。作为新思科技定制设计系列产品

2023-11-09 10:59:40 1588

1588 (RF)设计和接口IP五项大奖。新思科技与台积公司长期稳固合作,持续提供经过验证的解决方案,包括由Synopsys.ai全栈式AI驱动型EDA解决方案支持的认证设计流程,帮助共同客户加快创新型人工智能

2023-11-14 10:31:46 1202

1202 多个奖项高度认可新思科技在推动先进工艺硅片成功和技术创新领导方面所做出的卓越贡献 摘要 : 新思科技全新数字与模拟设计流程认证针对台积公司N2和N3P工艺可提供经验证的功耗、性能和面积(PPA)结果

2023-11-14 14:18:45 743

743 全新参考流程针对台积公司 N4PRF 工艺打造,提供开放、高效的射频设计解决方案。

2023-11-27 16:54:02 1430

1430 台积电近期宣布加速其先进封装计划,并上调了产能目标。这是因为英伟达和AMD等客户订单的持续增长。

2024-01-24 15:58:49 1061

1061 芯片制造商与EDA解决方案和广泛的IP组合紧密合作, 能够提升产品性能并加快上市时间 摘要: 新思科技数字和模拟EDA流程经过认证和优化,针对Intel 18A工艺实现功耗、性能和面积目标

2024-03-05 10:16:59 1014

1014 新思科技数字和模拟 EDA 流程经过认证和优化,针对Intel 18A工艺实现功耗、性能和面积目标

2024-03-05 17:23:44 1134

1134 近日,新思科技与英特尔宣布深化合作,共同加速先进芯片设计的步伐。据悉,新思科技的人工智能驱动的数字和模拟设计流程已经成功通过英特尔代工的Intel 18A工艺认证,这一突破性的进展标志着双方在芯片设计领域的合作迈上了新台阶。

2024-03-06 10:33:59 1293

1293 近日,是德科技、新思科技和Ansys携手,共同推出了一个革命性的集成射频(RF)设计迁移流程。这一流程旨在助力台积电从N16制程无缝升级到N6RF+技术,以满足当前无线集成电路在功耗、性能和面积(PPA)上的严苛挑战。

2024-05-11 10:42:17 788

788 套件赋能可投产的数字和模拟设计流程能够针对台积公司N3/N3P和N2工艺,助力实现芯片设计成功,并加速模拟设计迁移。 新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证,可加速全芯片物理签核。 新思科技3DIC Compiler和光子集成电路(PIC)解决方案与台

2024-05-11 11:03:49 695

695

新思科技EDA事业部战略与产品管理副总裁Sanjay Bali表示:“新思科技在可投产的EDA流程和支持3Dblox标准的3DIC Compiler光子集成方面的先进成果,结合我们广泛的IP产品组合,使得我们与台积公司能够助力开发者基于台积公司先进工艺加速下一代芯片设计创新。

2024-05-11 16:25:42 1015

1015 新思科技近日与台积公司宣布,在先进工艺节点设计领域开展了广泛的EDA和IP合作。双方的合作成果已经成功应用于一系列人工智能、高性能计算和移动设计领域,取得了显著成效。

2024-05-13 11:04:48 931

931 由Synopsys.ai EDA套件赋能可投产的数字和模拟设计流程能够针对台积公司N3/N3P和N2工艺,助力实现芯片设计成功,并加速模拟设计迁移。

2024-05-14 10:36:48 1197

1197

台积电作为晶圆代工领域的领头羊,正加速其产能扩张步伐,以应对日益增长的人工智能市场需求。据摩根士丹利最新发布的投资报告“高资本支出与持续性的成长”显示,台积电在2nm及3nm先进制程以及CoWoS先进封装技术上的产能正快速提升,这进一步巩固了其在全球半导体市场的领先地位。

2024-09-27 16:45:25 1247

1247 半导体技术领域的发展速度十分惊人,新思科技与台积公司(TSMC)始终处于行业领先地位,不断突破技术边界,推动芯片设计的创新与效率提升。我们与台积公司的长期合作催生了众多行业进步,从更精细的工艺节点到更高层次的系统集成,创造了无限可能。

2024-10-31 14:28:17 1022

1022 近日,据台湾媒体报道,随着AI领域对先进制程与封装产能的需求日益旺盛,台积电计划从2025年1月起,针对其3nm、5nm以及先进的CoWoS封装工艺进行价格调整。 具体而言,台积电将对3nm和5nm

2024-12-31 14:40:59 1373

1373 为了满足市场上对先进封装技术的强劲需求,台积电正在加速推进其CoWoS(Chip-on-Wafer-on-Substrate)等先进封装技术的布局。近日,市场传言台积电将在南部科学工业园区(南科

2025-01-23 10:18:36 931

931 近日,台积电在美国举行了首季董事会,并对外透露了其在美国的扩产计划。台积电董事长魏哲家在会上表示,公司将正式启动第三厂的建厂行动,这标志着台积电在美国的布局将进一步加强。 据了解,台积电在先进

2025-02-14 09:58:01 933

933 :CDNS)近日宣布进一步深化与台积公司的长期合作,利用经过认证的设计流程、经过硅验证的 IP 和持续的技术协作,加速 3D-IC 和先进节点技术的芯片开发进程。作为台积公司 N2P、N5 和 N3 工艺节点

2025-05-23 16:40:04 1709

1709 新思科技近日宣布持续深化与台积公司的合作,为台积公司的先进工艺和先进封装技术提供可靠的EDA和IP解决方案,加速AI芯片设计和多芯片设计创新。

2025-05-27 17:00:55 1038

1038 积公司的模拟设计迁移(ADM)方法学为基础,集成了新思科技AI驱动的射频迁移解决方案与是德科技的射频解决方案,可简化无源器件和设计组件的重新设计工作,使其符合台积公司更先进的射频工艺规则。

2025-06-27 17:36:15 1347

1347 还就面向TSMC-COUPE平台的AI辅助设计流程开展了合作。新思科技与台积公司共同赋能客户有效开展芯片设计,涵盖AI加速、高速通信和先进计算等一系列应用。

2025-10-21 10:11:05 434

434 新思科技作为重要的合作伙伴,再次获台积公司认可。在2025年台积公司开放创新平台(Open Innovation Platform,简称OIP)生态系统论坛上,我们荣膺六项年度合作伙伴大奖。这些奖项

2025-10-24 16:31:58 1124

1124 新思科技近期宣布,其LPDDR6 IP已在台积公司 N2P 工艺成功流片,并完成初步功能验证。这一成果不仅巩固并强化了新思科技在先进工艺节点 IP 领域的领先地位,同时也为客户提供可信赖的、经硅片验证的IP选择,可满足移动通讯、边缘 AI 及高性能计算等更高存储带宽需求的应用场景。

2025-10-30 14:33:48 1873

1873

电子发烧友App

电子发烧友App

评论