新思科技联合Ansys、是德科技共同开发的高质量、紧密集成的RFIC设计产品,旨在通过全新射频设计流程优化N6无线系统的功率和性能。

新思科技(Synopsys)近日推出面向台积公司N6RF工艺的全新射频设计流程,以满足日益复杂的射频集成电路设计需求。台积公司N6RF工艺采用了业界领先的射频CMOS技术,可提供显著的性能和功效提升。新思科技携手Ansys、是德科技(Keysight)共同开发了该全新射频设计流程,旨在助力共同客户优化5G芯片设计,并提高开发效率以加速上市时间。

我们与新思科技的最新合作着眼于下一代无线系统的挑战,赋能开发者为日益紧密相连的世界提供更强连接、更大带宽、更低延迟和更广覆盖范围。借助新思科技联手Ansys、是德科技开发的高质量、紧密集成的解决方案,台积公司针对N6RF工艺的全新射频设计参考流程提供了一种现代、开放的方法,有助于提高复杂集成电路的开发效率。

Suk Lee设计基础设施管理事业部副总经理台积公司

提高下一代无线系统的带宽和连接性

基于万物互联世界的发展需求,用于收发器和射频前端组件等无线数据传输系统的射频集成电路变得日益复杂。这些下一代无线系统将在更多的互联设备上提供更大带宽、更低延迟和更广覆盖范围。为了确保射频集成电路能够满足这些要求,开发者必须能够准确测试射频性能、频谱、波长和带宽等参数。

全新射频设计参考流程通过业界领先的电路仿真和版图生产率,以及精确的电磁(EM)建模和电迁移/IR压降(EMIR)分析,加快了设计交付时间。该流程包括新思科技Custom Compiler™设计和版图解决方案、PrimeSim™电路仿真解决方案、StarRC™寄生参数提取签核解决方案和IC Validator™物理验证解决方案;Ansys VeloceRF™感应组件和传输线综合产品、RaptorX™和RaptorH™先进纳米电磁分析产品、Totem-SC®产品;以及是德科技用于电磁仿真的PathWave RFPro。

射频设计客户将显著受益于新思科技定制设计解决方案Customer Compiler和PathWave RFPro在台积公司的设计参考流程中的互操作性。通过将电磁协同仿真左移至设计流程之前,使射频电路的开发者能够优化面向5G和WiFi 6/6E应用的先进芯片和多技术模块的寄生参数效应。这样可以让仿真工作流程节省数天甚至数周时间,同时降低产品开发周期中成本高昂的重制(re-spin)风险。我们与新思科技、台积公司的合作为射频客户提供了其所需的设计工具和先进工艺技术,以确保实现高性能和首次流片成功。

Niels Fache副总裁兼PathWave软件解决方案总经理是德科技

很高兴能与新思科技、台积公司共同开发用于RFIC设计的先进参考流程。5G和6G设计需求的不断增长产生了极大的复杂性,以及纳米节点上的先进工艺效果,给RFIC开发者带来了巨大的挑战。在EM和EMIR分析中精确模拟仿真先进的工艺效果,对于创建从DC到几十GHz的一次性流片成功至关重要。Ansys的VeloceRF、RaptorX、Exalto和Totem-SC等工具与新思科技Custom Complier platform实现了无缝协作,能够提供业界领先的能力来处理最具挑战性的设计,并为所有先进工艺效果建模。这可为射频设计模块的设计、优化和验证提供了一个直观且易于使用的流程。

Yorgos Koutsoyannopoulos研发副总裁Ansys

新思科技致力于持续提供强大的射频设计解决方案,通过集成电磁合成、提取、设计、版图、签核技术和仿真工作流程实现了5G设计的关键差异化优势。基于新思科技与台积公司的深度合作关系,以及与Ansys、是德科技的紧密联系,客户采用台积公司面向5G应用的先进N6RF技术后,将可以通过新思科技定制设计系列产品的先进功能来提高生产效率,并成功实现芯片设计。

Aveek Sarkar工程副总裁新思科技

-

集成电路

+关注

关注

5464文章

12681浏览量

375670 -

射频

+关注

关注

106文章

6108浏览量

173835 -

新思科技

+关注

关注

5文章

979浏览量

52986

发布评论请先 登录

忆联正式推出面向PCIe 5.0的自研M.2 SLT测试系统

贸泽推出全新电子书 提供无线射频设计和应用的工程设计指南

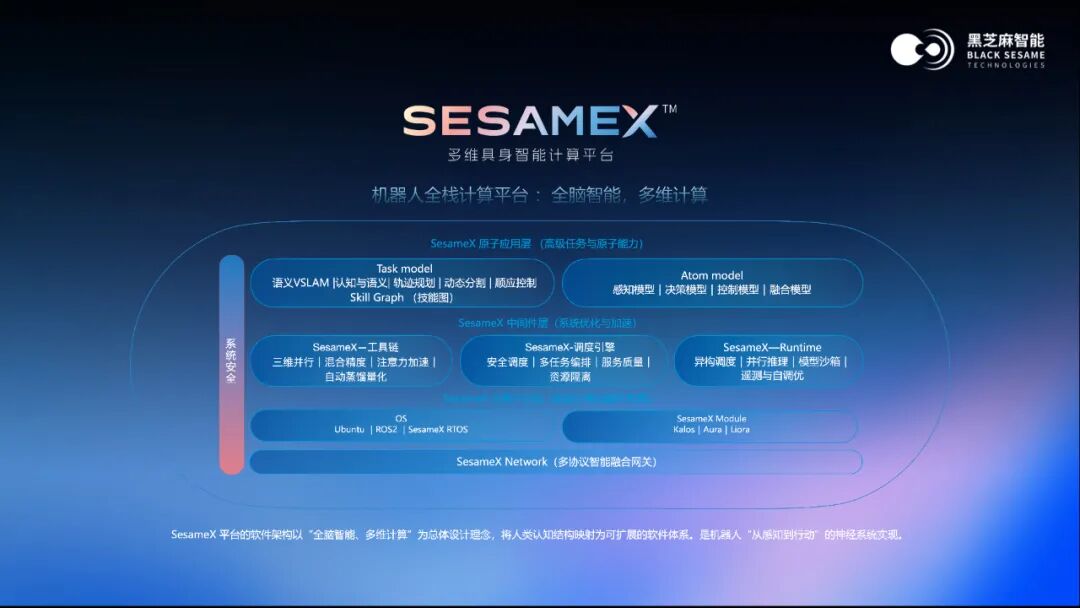

黑芝麻智能推出面向机器人产业的SesameX多维智能计算平台

NVIDIA推出面向语言、机器人和生物学的全新开源AI技术

曙光存储推出面向金融的可信AI存储

新思科技旗下Ansys仿真和分析解决方案产品组合已通过台积公司认证

Cadence AI芯片与3D-IC设计流程支持台积公司N2和A16工艺技术

Cadence基于台积电N4工艺交付16GT/s UCIe Gen1 IP

新思科技推出面向台积公司N6RF工艺全新射频设计流程

新思科技推出面向台积公司N6RF工艺全新射频设计流程

评论