来源:是德科技

PathWave RFPro 与新思科技定制化编译器相辅相成,可提供无线晶片设计工作流程所需的整合式电磁模拟工具

是德科技(Keysight Technologies Inc.) 是推动全球企业、服务供应商和政府机构网路连接与安全创新的技术领导厂商,该公司日前宣布其 Keysight PathWave RFPro 与新思科技(Synopsys)定制化编译器设计环境已完成整合,以便支持台积电(TSMC)最新的 6 纳米 RF(N6RF)设计参考流程。

对于集成电路(IC)设计人员来说,EDA 工具和设计方法至关重要。最新的 TSMC N6RF 设计参考流程,为设计人员提供重要指引,使其能够利用台积电先进的 N6RF 互补式金氧半导体(CMOS)技术,准确地执行电路设计和模拟,以支持下一代 5G 和无线应用。

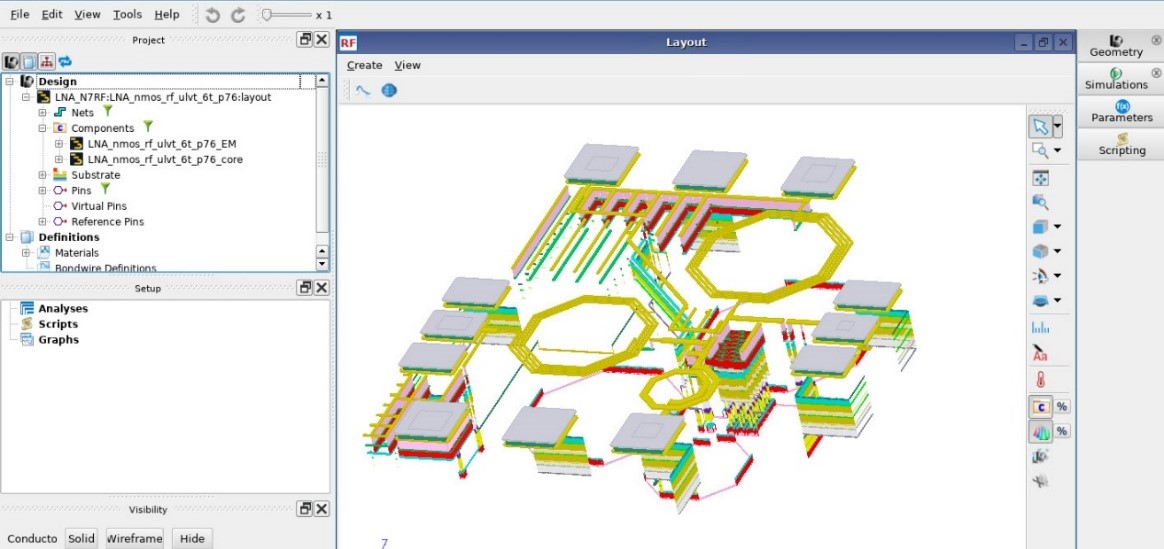

PathWave RFPro 主设定视窗可显示使用 TSMC N6RF 技术设计的低杂讯放大器

是德科技和新思科技共同在 Synopsys 编译器中开发定制化设计范例,方便工程师在 Keysight PathWave RFPro 中执行集成的电磁(EM)分析和定制的射频元件建模。客户可结合使用 PathWave RFPro 与定制化编译器并纳入其端对端工作流程中,以确保 EM 模拟和电路布局的互通性。

是德科技 PathWave 软体解决方案事业群副总裁暨总经理 Niels Faché 表示:“Keysight PathWave RFPro EM 模拟软体与新思科技定制化编译器的紧密整合,可为客户提供经验证的解决方案,让他们能够使用 TSMC N6RF 设计参考流程,快速、准确地设计无线晶片。 企业需借助整合式电磁模拟,来验证并改善现今多制程射频设计中的寄生效应。 藉由迭代执行电磁电路协同模拟,设计工程师可确保一次设计就成功。台积电、新思科技和是德科技合作无间,缔造了这项互通性成就。”

为了让 IC 设计人员更顺利部署此参考流程,是德科技与新思科技共同撰写了详细的应用说明。台积电已推出并提供 TSMC N6RF 设计参考流程及 N6RF 技术封装制程。

新思科技工程事业群副总裁 Aveek Sakar 表示:“此参考流程是我们与是德科技长期合作的心血结晶,它将 Synopsys 定制化编译器和 Keysight RFPro 紧密整合在一起。 新的参考流程让设计人员能够利用台积电最新、最先进的 RF CMOS 技术*,尽快展开射频设计和模拟作业。”

台积电设计建构管理处副总裁 Suk Lee 表示:“我们与是德科技和新思科技的合作,让客户能够利用我们领先业界的 RF CMOS 技术,部署先进的 IC 设计和模拟流程。 对于是德科技和新思科技共同开发的射频设计参考流程,我们感到非常满意,并期待未来我们能继续合作,以协助射频 IC 设计客户满足复杂的需求,并快速将其独特产品推出问市。”

如需是德科技工具和解决方案的详细资讯,请浏览 Keysight EDA 软体:40 年设计成功案例。

如需是德科技与新思科技合作成果的详细资讯,请参阅《是德科技与新思科技密切合作,提供整合式 5G 设计定制化设计流程》。

* RF CMOS 技术是一种金属氧化物半导体(MOS)集成电路(IC)技术,可将射频、类比和数位电子,整合到混合信号 CMOS(互补式 MOS)射频电路晶片。

审核编辑:符乾江

-

eda

+关注

关注

72文章

3148浏览量

183824 -

设计流程

+关注

关注

0文章

16浏览量

8264

发布评论请先 登录

是德科技与新思科技共同合作,支持台积电N6RF设计参考流程

是德科技与新思科技共同合作,支持台积电N6RF设计参考流程

评论