内容提要

|

1 |

轻松实现节点到节点的设计和 layout 迁移 |

|

2 |

将定制/模拟设计迁移速度提升 2 倍 |

|

3 |

Cadence Virtuoso Studio 针对所有 Samsung Foundry 先进节点经过优化 |

中国上海, 2023 年 7 月 4 日——楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布,搭载最新生成式 AI 技术的 CadenceVirtuosoStudio 现已支持经过认证的节点到节点设计迁移流程。该流程与 Samsung Foundry 的先进节点兼容。Cadence 和 Samsung 共同开发了这个新的生成式设计迁移流程,可简化和自动化迁移过程,为双方的共同用户实现高达 2 倍的生产力提升,帮助他们更快将产品推向市场。

Virtuoso Schematic Editor 是 Virtuoso Studio 的一部分,可以自动将源原理图的实例、参数、引脚和连线从一种工艺技术映射到另一种工艺技术。使用 Virtuoso ADE 仿真环境和基于 AI 的电路优化技术,可对映射的原理图进行优化和验证,确保更新后的原理图能够满足所有必要的设计规范。

Virtuoso Layout Suite 是 Virtuoso Studio 的一部分,它支持在既定的工艺技术上重复使用现有的 layout,通过自定义布局和自动化布线,在新的工艺技术上快速重建迁移后的 layout。该套件可自动识别和提取现有 layout 中的器件组,并将其迁移到新模板中。在目标 layout 中,对应的器件布局和布线方式与原来相似,无需花费几周的时间手动重新创建 layout,同时也利用了新目标工艺的尺寸缩减优势。

“设计人员的工期越来越短,因此找到创造性的方法来提高效率成为当务之急,”Samsung Electronics 代工厂设计技术团队副总裁 Sangyun Kim 说,“我们与 Cadence 持续合作,让客户可以同时使用 Cadence Virtuoso Studio 流程和 Samsung 先进节点技术加快节点到节点的迁移。”

“通过此次与 Samsung 的最新合作,双方的共同客户可以使用我们搭载生成式 AI 技术的新版 Virtuoso Studio,利用自动化功能简单快速地从一种制程技术迁移到另一种,”Cadence 公司高级副总裁兼定制 IC 和 PCB 事业部总经理 Tom Beckley 说,“Samsung 的先进工艺技术和 Cadence 流程双剑合璧,助力设计人员提高生产力,更快地将高质量的设计推向市场。”

Cadence Virtuoso Studio 支持 Cadence 智能系统设计(Intelligent System Design)战略,助力实现系统级芯片(SoC)的卓越设计。

如需进一步了解 Virtuoso Studio 请访问

www.cadence.com/go/virtuosostudiosf

(您可复制至浏览器或点击阅读原文打开)

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

Cadence

+关注

关注

68文章

1031浏览量

147403

原文标题:Cadence Virtuoso Studio流程获得Samsung Foundry认证,支持先进工艺技术的模拟IP自动迁移

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Cadence Virtuoso Dashboard功能简介

国产高性能ONFI IP解决方案全解析

Cadence Conformal AI Studio三大核心引擎重塑IC验证

Cadence Conformal AI Studio荣获2025亚洲金选奖年度最佳EDA奖

热压键合工艺的技术原理和流程详解

AI如何重塑模拟和数字芯片工艺节点迁移

ADI Power Studio工作流程与工具概述

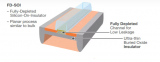

SOI工艺技术介绍

Cadence Virtuoso Studio流程获得Samsung Foundry认证,支持先进工艺技术的模拟IP自动迁移

Cadence Virtuoso Studio流程获得Samsung Foundry认证,支持先进工艺技术的模拟IP自动迁移

评论