键合玻璃载板(Glass Carrier/Substrate)是一种用于半导体封装工艺的临时性硬质支撑材料,通过键合技术与硅晶圆或芯片临时固定在一起,在特定工序(如减薄、RDL布线)完成后通过紫外光

2026-01-05 09:23:37 536

536 扇出型晶圆级封装(FOWLP)的概念最早由德国英飞凌提出,自2016 年以来,业界一直致力于FOWLP 技术的发展。

2026-01-04 14:40:30 174

174

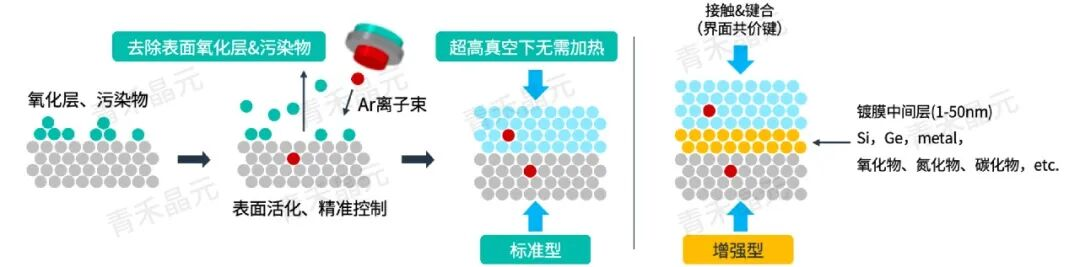

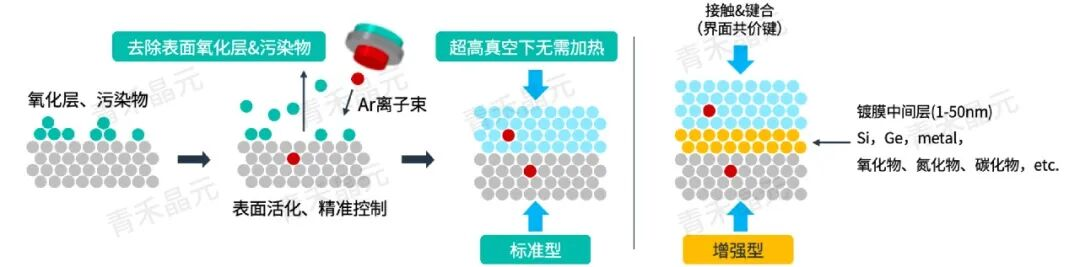

关键词: 常温键合;第三代半导体;异质集成;半导体设备;青禾晶元;半导体技术突破;碳化硅(SiC);氮化镓(GaN);超高真空键合;先进封装;摩尔定律 随着5G/6G通信、新能源汽车与人工智能对芯片

2025-12-29 11:24:17 133

133

(SiGe BiCMOS)工艺领域,正式推出支持光电共封装(CPO)的新型代工技术。 这项技术依托多年堆叠式背照式(BSI)图像传感器量产经验,实现异构 3D-IC 集成,并获得 Cadence

2025-11-21 08:46:00 4242

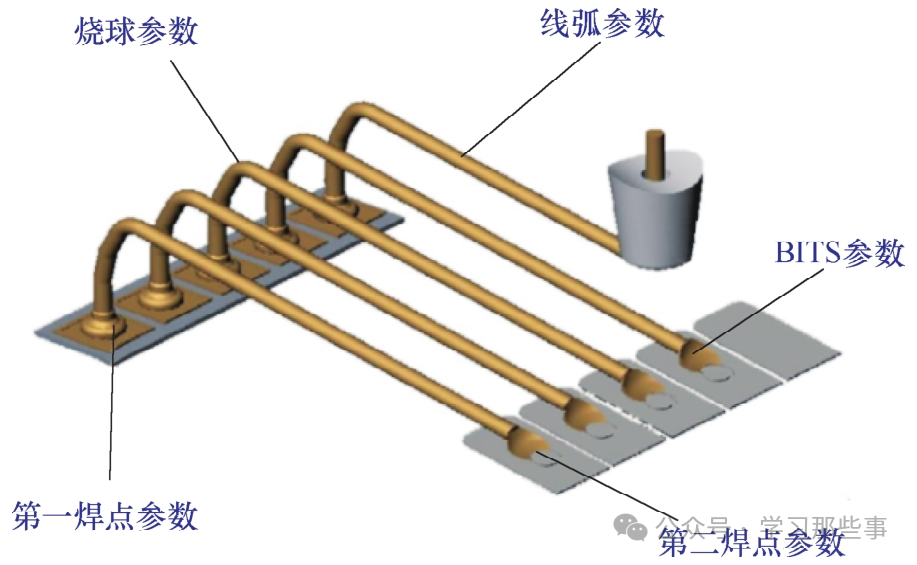

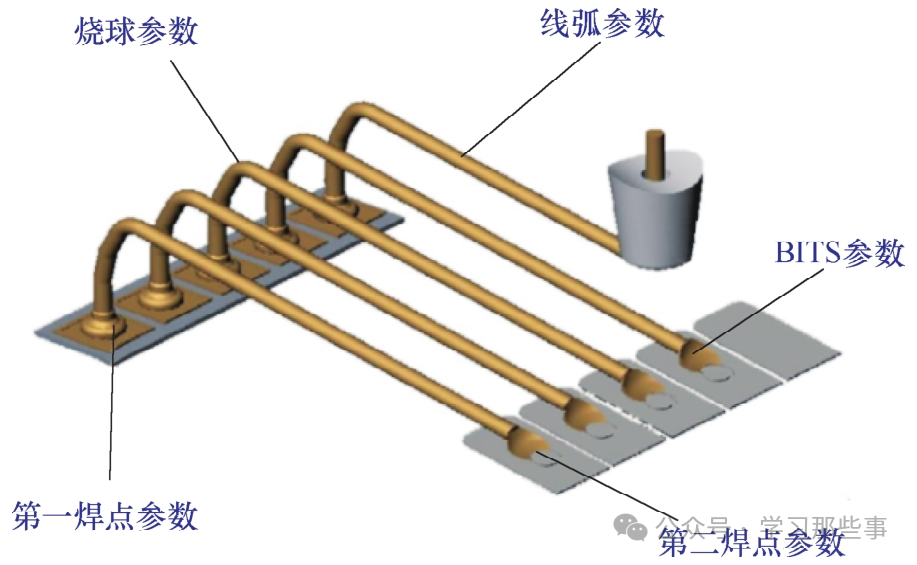

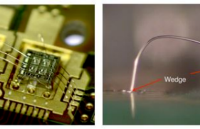

4242 在现代微电子封装领域,集成电路(IC)的可靠性与稳定性是决定产品品质的关键。其中,键合点的机械强度直接影响到芯片在后续加工、运输及使用过程中的性能表现。IC铝带作为一种重要的内引线材料,其与芯片焊盘

2025-11-09 17:41:45 1162

1162

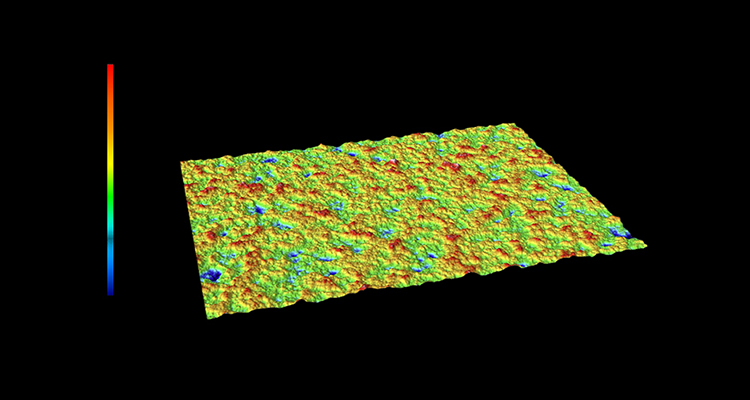

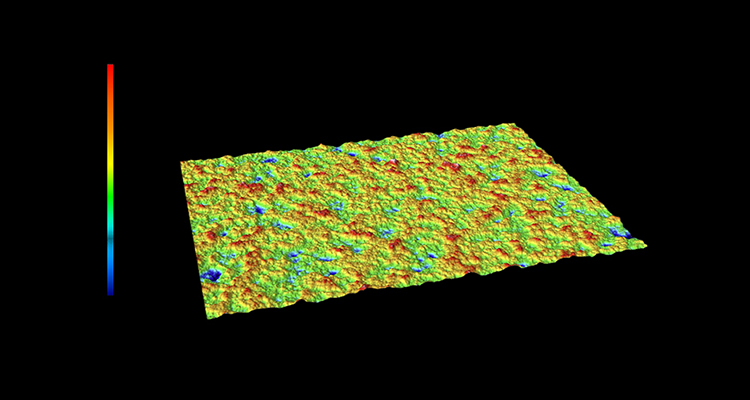

摘要:本文研究白光干涉仪在晶圆深腐蚀沟槽 3D 轮廓测量中的应用,分析其工作原理及适配深腐蚀沟槽特征的技术优势,通过实际案例验证测量精度,为晶圆深腐蚀工艺的质量控制与器件性能优化提供技术

2025-10-30 14:22:51 225

225

电子元器件封装中的引线键合工艺,是实现芯片与外部世界连接的关键技术。其中,金铝键合因其应用广泛、工艺简单和成本低廉等优势,成为集成电路产品中常见的键合形式。金铝键合失效这种现象虽不为人所熟知,却是

2025-10-24 12:20:57 444

444

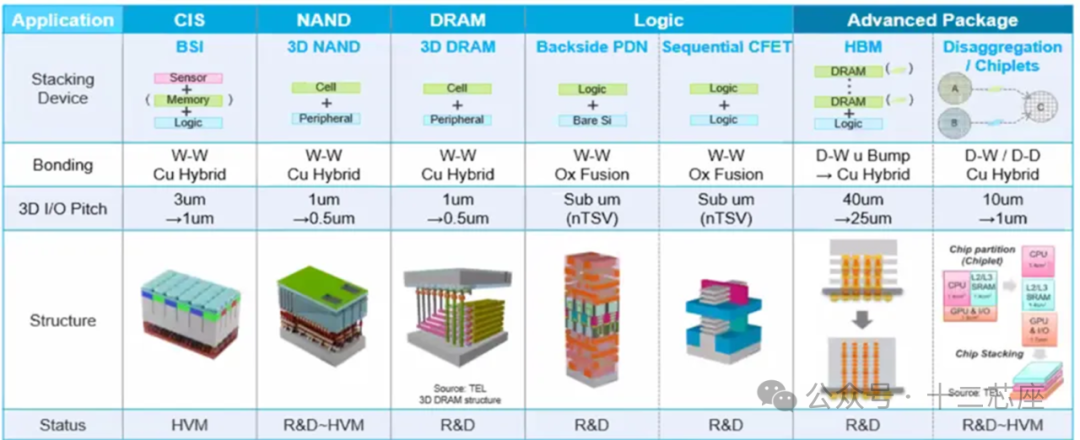

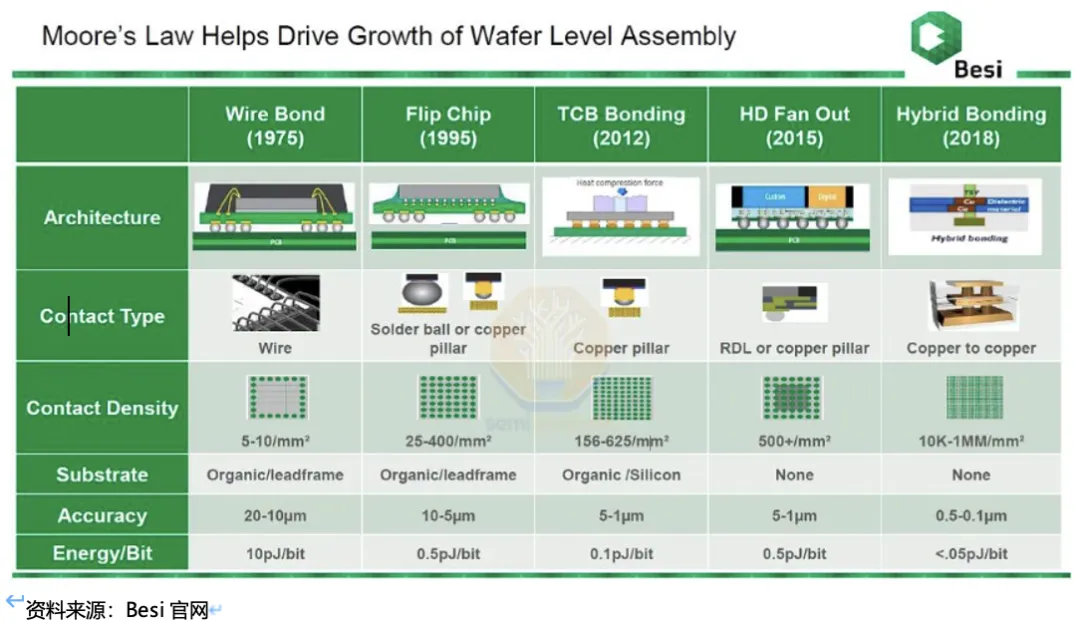

微电子技术的演进始终围绕微型化、高效性、集成度与低成本四大核心驱动力展开,封装技术亦随之从传统TSOP、CSP、WLP逐步迈向系统级集成的PoP、SiP及3D IC方向,最终目标是在最小面积内实现系统功能的最大化。

2025-10-21 17:38:28 1749

1749

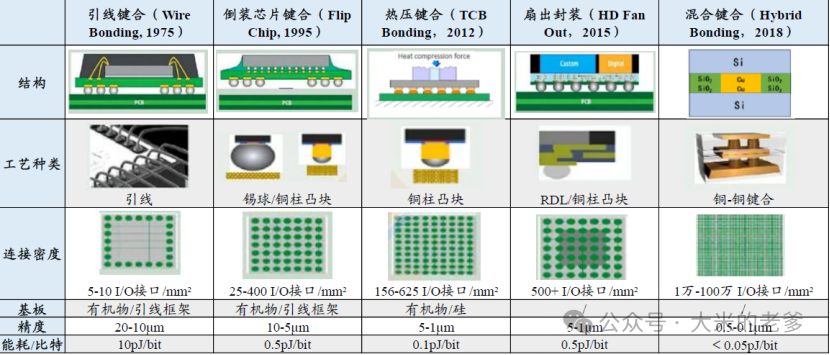

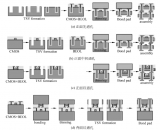

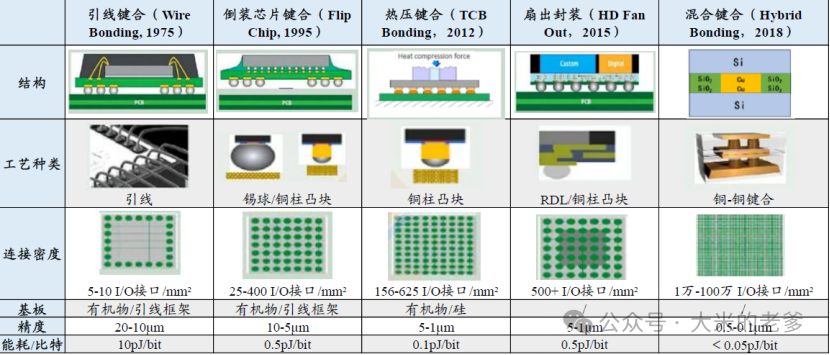

在半导体封装工艺中,芯片键合(Die Bonding)是指将晶圆芯片固定到封装基板上的关键步骤。键合工艺可分为传统方法和先进方法:传统方法包括芯片键合(Die Bonding)和引线键合(Wire

2025-10-21 17:36:16 2052

2052

在功率半导体封装领域,晶圆级芯片规模封装技术正引领着分立功率器件向更高集成度、更低损耗及更优热性能方向演进。

2025-10-21 17:24:13 3873

3873

摘要:本文研究白光干涉仪在肖特基二极管晶圆深沟槽 3D 轮廓测量中的应用,分析其工作原理及适配深沟槽结构的技术优势,通过实际案例验证其测量精度,为肖特基二极管晶圆深沟槽制造的质量控制与性能优化提供

2025-10-20 11:13:27 279

279

一、引言

12 英寸及以上的大尺寸玻璃晶圆在半导体制造、显示面板、微机电系统等领域扮演着关键角色 。总厚度偏差(TTV)的均匀性直接影响晶圆后续光刻、键合、封装等工艺的精度与良率 。然而,随着晶圆

2025-10-17 13:40:01 399

399

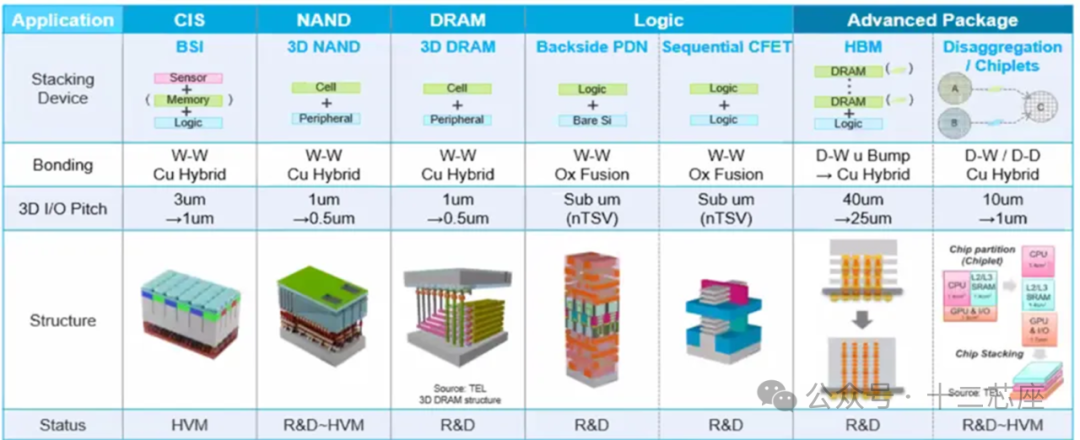

3D封装架构主要分为芯片对芯片集成、封装对封装集成和异构集成三大类,分别采用TSV、TCB和混合键合等先进工艺实现高密度互连。

2025-10-16 16:23:32 1548

1548

一、引言

随着半导体技术向小型化、高性能化发展,3D 集成封装技术凭借其能有效提高芯片集成度、缩短信号传输距离等优势,成为行业发展的重要方向 。玻璃晶圆因其良好的光学透明性、化学稳定性及机械强度

2025-10-14 15:24:56 316

316

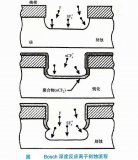

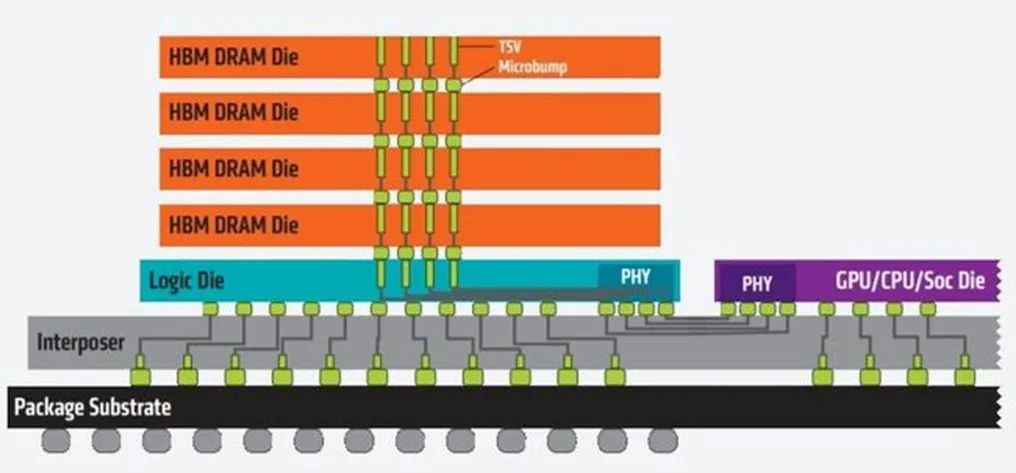

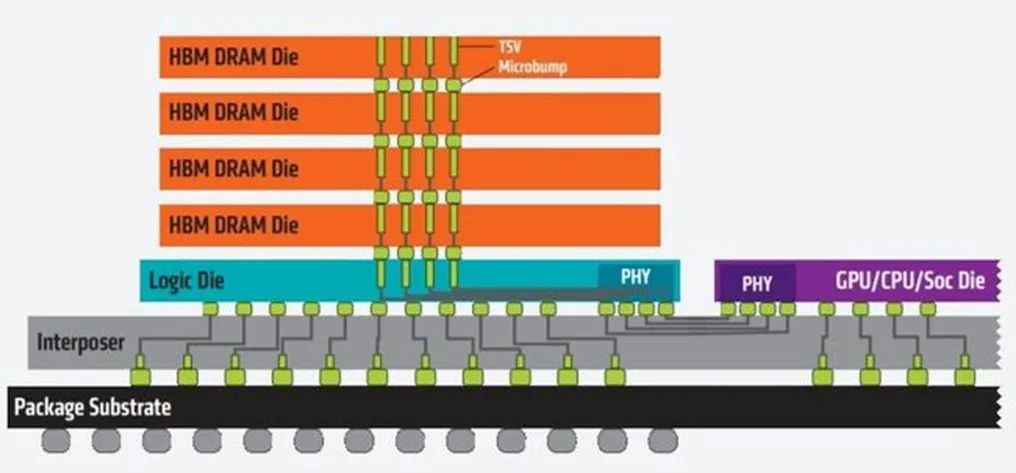

硅通孔(TSV)技术借助硅晶圆内部的垂直金属通孔,达成芯片间的直接电互连。相较于传统引线键合等互连方案,TSV 技术的核心优势在于显著缩短互连路径(较引线键合缩短 60%~90%)与提升互连密度

2025-10-14 08:30:00 6439

6439

上市周期,以满足 AI 和 HPC 客户的应用需求。Cadence 与台积公司在 AI 驱动的 EDA、3D-IC、IP 及光子学等领域展开了紧密合作,推出全球领先的半导体产品。

2025-10-13 13:37:59 2087

2087 我将从超薄玻璃晶圆 TTV 厚度测量面临的问题出发,结合其自身特性与测量要求,分析材料、设备和环境等方面的技术瓶颈,并针对性提出突破方向和措施。

超薄玻璃晶圆(

2025-09-28 14:33:22 337

337

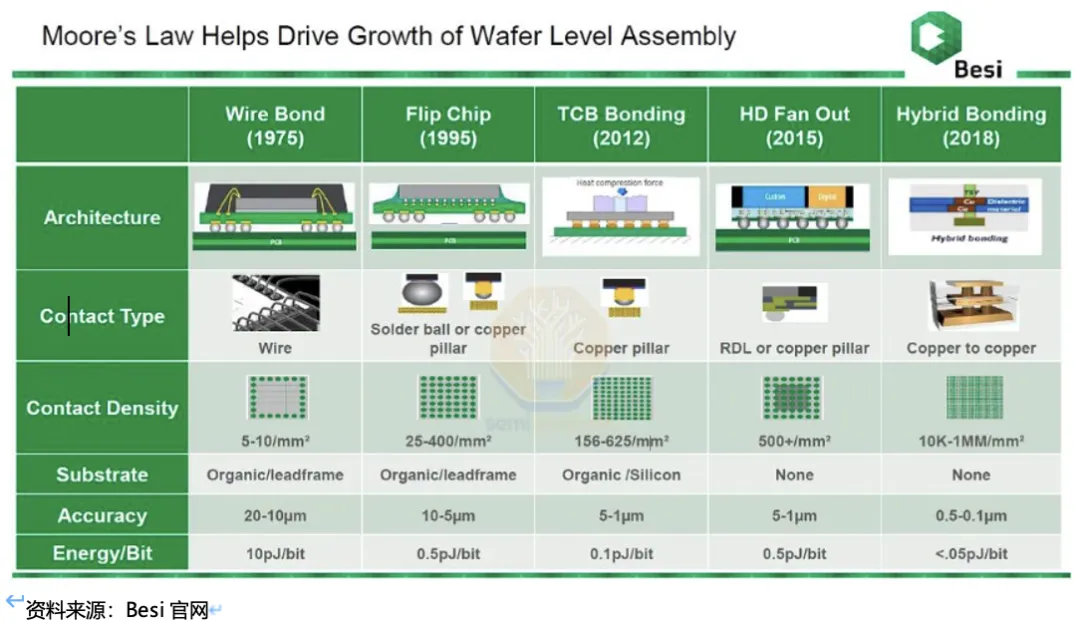

随着半导体产品高性能、轻薄化发展,封装技术作为连接芯片与外界环境的桥梁,其重要性日益凸显。在众多封装技术中,热压键合(Thermal Compression Bonding)工艺技术以其独特的优势

2025-09-25 17:33:09 908

908

在先进封装中, Hybrid bonding( 混合键合)不仅可以增加I/O密度,提高信号完整性,还可以实现低功耗、高带宽的异构集成。它是主要3D封装平台(如台积电的SoIC、三星的X-Cube

2025-09-17 16:05:36 1467

1467

全新EVG®40 D2W套刻精度计量系统实现每颗芯片100%测量,吞吐量达行业基准15倍 2025年9月8日,奥地利圣弗洛里安 ——全球领先的先进半导体工艺解决方案与技术提供商EV 集团(EVG

2025-09-11 15:22:57 708

708 。然而,当系统级集成需求把 3D 封装/3D IC 技术推向 WLCSP 时,传统方案——引线键合堆叠、PoP、TSV 硅通孔——因工艺窗口、CTE 失配及成本敏感性而显著受限。

2025-08-28 13:46:34 2892

2892

在晶圆加工流程中,早期检测宏观缺陷是提升良率与推动工艺改进的核心环节,这一需求正驱动检测技术与晶圆测试图分析领域的创新。宏观缺陷早期检测的重要性与挑战在晶圆层面,一个宏观缺陷可能影响多个芯片,甚至在

2025-08-19 13:48:23 1116

1116

随着半导体器件向更精密的封装方案持续演进,传统光学检测技术正逐渐触及物理与计算的双重边界。对2.5D/3D集成、混合键合及晶圆级工艺的依赖日益加深,使得缺陷检测的一致性与时效性面临严峻挑战——若无

2025-08-19 13:47:10 816

816

2.5D/3D封装技术作为当前前沿的先进封装工艺,实现方案丰富多样,会根据不同应用需求和技术发展动态调整,涵盖芯片减薄、芯片键合、引线键合、倒装键合、TSV、塑封、基板、引线框架、载带、晶圆级薄膜

2025-08-05 15:03:08 2805

2805

摘要

本文围绕半导体晶圆研磨工艺,深入剖析聚氨酯研磨垫磨损状态与晶圆 TTV 均匀性的退化关系,探究其退化机理,并提出相应的预警方法,为保障晶圆研磨质量、优化研磨工艺提供理论与技术支持。

引言

在

2025-08-05 10:16:02 685

685

₂融合)与中间层键合(如高分子、金属)两类,其温度控制、对准精度等参数直接影响芯片堆叠、光电集成等应用的性能与可靠性,本质是通过突破纳米级原子间距实现微观到宏观的稳固连接。

2025-08-01 09:25:59 1760

1760

我将围绕超薄晶圆切割液性能优化与 TTV 均匀性保障技术展开,从切割液对 TTV 影响、现有问题及优化技术等方面撰写论文。

超薄晶圆(

2025-07-30 10:29:56 326

326

一万亿晶体管”目标的关键跳板。当前先进封装虽提高了I/O密度,但愈发复杂的异构设计与Chiplet架构对I/O数量、延迟提出了更高要求,以满足AI、5G和高性能计算等应用。混合键合互连技术正成为关键突破口,它可显著降低能耗、扩大带宽、优化热管理,从而助力摩尔定律继续前行。 Cou

2025-07-28 16:32:54 381

381 晶圆清洗机中的晶圆夹持是确保晶圆在清洗过程中保持稳定、避免污染或损伤的关键环节。以下是晶圆夹持的设计原理、技术要点及实现方式: 1. 夹持方式分类 根据晶圆尺寸(如2英寸到12英寸)和工艺需求,夹持

2025-07-23 14:25:43 928

928 厚度不均匀 。切割深度动态补偿技术通过实时调整切割深度,为提升晶圆 TTV 厚度均匀性提供了有效手段,深入研究其提升机制与参数优化方法具有重要的现实意义。

二、

2025-07-17 09:28:18 404

404

超薄晶圆厚度极薄,切割时 TTV 均匀性控制难度大。我将从阐述研究背景入手,分析浅切多道切割在超薄晶圆 TTV 均匀性控制中的优势,再深入探讨具体控制技术,完成文章创作。

超薄晶圆(

2025-07-16 09:31:02 469

469

我将从超薄晶圆浅切多道切割技术的原理、TTV 均匀性控制的重要性出发,结合相关研究案例,阐述该技术的关键要点与应用前景。

超薄晶圆(

2025-07-15 09:36:03 486

486

电子发烧友网为你提供()Silicon PIN 二极管、封装和可键合芯片相关产品参数、数据手册,更有Silicon PIN 二极管、封装和可键合芯片的引脚图、接线图、封装手册、中文资料、英文资料

2025-07-14 18:32:06

一、引言

在半导体制造中,晶圆总厚度变化(TTV)均匀性是决定芯片性能与良品率的关键因素,而切割过程产生的应力会导致晶圆变形,进一步恶化 TTV 均匀性。浅切多道工艺作为一种先进的晶圆切割技术,在

2025-07-14 13:57:45 465

465

所谓混合键合(hybrid bonding),指的是将两片以上不相同的Wafer或Die通过金属互连的混合键合工艺,来实现三维集成,在Hybrid Bonding前,2D,2.5D及3D封装都是采用

2025-07-10 11:12:17 2714

2714

电子发烧友网为你提供()硅限幅器二极管、封装和可键合芯片相关产品参数、数据手册,更有硅限幅器二极管、封装和可键合芯片的引脚图、接线图、封装手册、中文资料、英文资料,硅限幅器二极管、封装和可键合芯片真值表,硅限幅器二极管、封装和可键合芯片管脚等资料,希望可以帮助到广大的电子工程师们。

2025-07-09 18:32:29

超薄晶圆因其厚度极薄,在切割时对振动更为敏感,易影响厚度均匀性。我将从分析振动对超薄晶圆切割的影响出发,探讨针对性的振动控制技术和厚度均匀性保障策略。

超薄晶圆(

2025-07-09 09:52:03 580

580

晶圆级封装中,锡膏是实现电气连接与机械固定的核心材料,广泛应用于凸点制作、植球工艺及芯片 - 基板互连等关键环节。主流采用 SAC 系、Sn-Cu 系、Sn-Bi 系等无铅锡膏,需满足高精度印刷、优异润湿性、高可靠性及低残留等严苛要求。

2025-07-02 11:16:52 1059

1059

电子发烧友网综合报道 半导体封装技术正经历从传统平面架构向三维立体集成的革命性跃迁,其中铜 - 铜混合键合技术以其在互连密度、能效优化与异构集成方面的突破,成为推动 3D 封装发展的核心

2025-06-29 22:05:13 1519

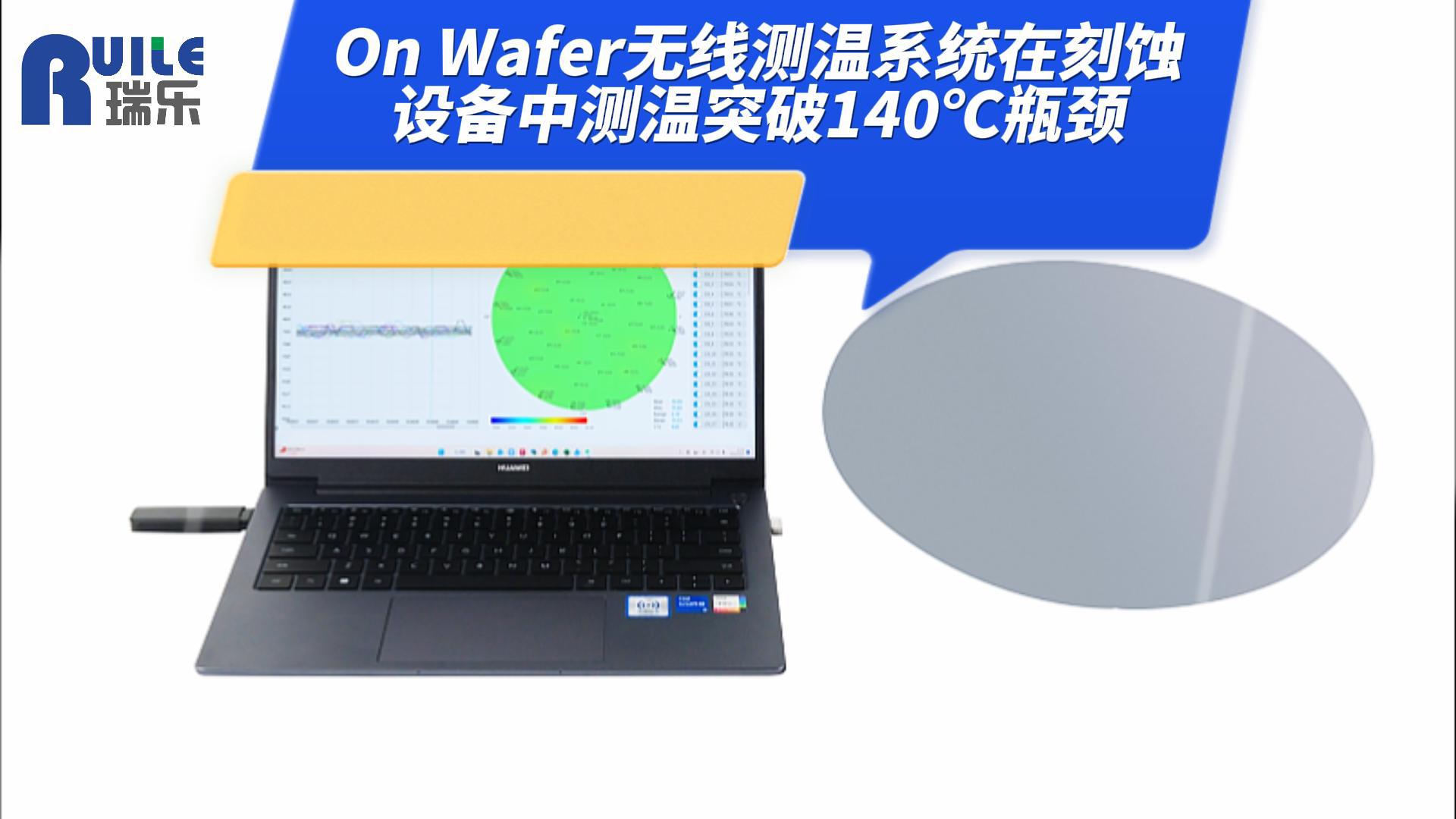

1519 的工艺参数。【应用范围】物理气相沉积 (PVD)、原子层沉积 (ALD)、化学气相沉积 (CVD)、退火炉、去胶设备、晶圆临时键合、涂胶

2025-06-27 10:16:41

晶圆级扇出封装(FO-WLP)通过环氧树脂模塑料(EMC)扩展芯片有效面积,突破了扇入型封装的I/O密度限制,但其技术复杂度呈指数级增长。

2025-06-05 16:25:57 2143

2143

在微电子行业飞速发展的背景下,封装技术已成为连接芯片创新与系统应用的核心纽带。其核心价值不仅体现于物理防护与电气/光学互联等基础功能,更在于应对多元化市场需求的适应性突破,本文着力介绍晶圆级扇入封装,分述如下。

2025-06-03 18:22:20 1054

1054

所谓混合键合(hybrid bonding),指的是将两片以上不相同的Wafer或Die通过金属互连的混合键合工艺,来实现三维集成,在Hybrid Bonding前,2D,2.5D及3D封装都是采用

2025-06-03 11:35:24 2031

2031

属直接键合的先进封装技术,其核心目标是实现芯片间高密度、低电阻的垂直互联。 在工艺过程中,需要经过对准和键合、后键合处理等几个流程。在对晶圆表面进行化学机械拋光(CMP)和清洗之后,通过光学或电子束对准系统实现亚微米级(通常

2025-06-03 09:02:18 2691

2691 通过退火优化和应力平衡技术控制。

3、弯曲度(Bow) 源于材料与工艺的对称性缺陷,对多层堆叠和封装尤为敏感,需在晶体生长和镀膜工艺中严格调控。

在先进制程中,三者共同决定了晶圆的几何完整性,是良率提升

2025-05-28 16:12:46

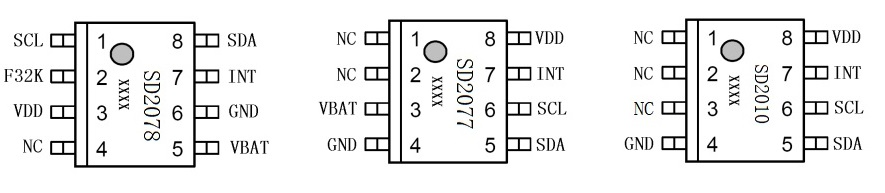

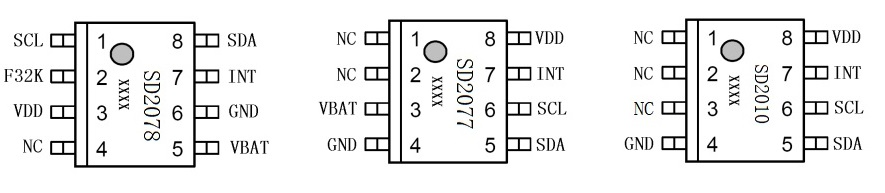

鸿合智远|兴威帆电子:内置晶振、小封装的实时时钟IC-SD

2025-05-28 10:01:36 670

670

WD4000系列Wafer晶圆厚度量测系统采用白光光谱共焦多传感器和白光干涉显微测量双向扫描技术,完成非接触式扫描并建立表面3D层析图像,实现Wafer厚度、翘曲度、平面度、线粗糙度、总体厚度变化

2025-05-27 13:54:33

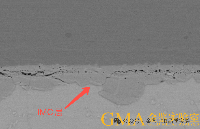

关键词:键合晶圆;TTV 质量;晶圆预处理;键合工艺;检测机制 一、引言 在半导体制造领域,键合晶圆技术广泛应用于三维集成、传感器制造等领域。然而,键合过程中诸多因素会导致晶圆总厚度偏差(TTV

2025-05-26 09:24:36 850

850

电池的集成。这一里程碑为封装内储能解决方案铺平了道路,助力实现更高效、紧凑且可靠的系统级封装(SiP)设计。 革新储能与先进封装 这一突破性创新标志着SiP技术的重大飞跃。通过在晶圆层面嵌入ITEN的高性能固态电池,ITEN与A*STAR IME成功展示了利用先进封装直接集成非易失

2025-05-22 13:08:59 560

560 使用直接晶圆到晶圆键合来垂直堆叠芯片,可以将信号延迟降到可忽略的水平,从而实现更小、更薄的封装,同时有助于提高内存/处理器的速度并降低功耗。目前,晶圆堆叠和芯片到晶圆混合键合的实施竞争异常激烈,这被

2025-05-22 11:24:18 1405

1405

常规IC封装需经过将晶圆与IC封装基板焊接,再将IC基板焊接至普通PCB的复杂过程。与之不同,WLP基于IC晶圆,借助PCB制造技术,在晶圆上构建类似IC封装基板的结构,塑封后可直接安装在普通PCB

2025-05-14 11:08:16 2420

2420

多芯片封装在现代半导体领域至关重要,主要分为平面多芯片封装和多芯片堆叠封装。多芯片堆叠封装又细分为多芯片3D堆叠引线键合封装、3D堆叠引线键合和倒装异质封装、3DTSV堆叠倒装封装等。

2025-05-14 10:39:54 1846

1846

我们看下一个先进封装的关键概念——晶圆级封装(Wafer Level Package,WLP)。

2025-05-14 10:32:30 1532

1532

英寸晶圆厚度约为670微米,8英寸晶圆厚度约为725微米,12英寸晶圆厚度约为775微米。尽管芯片功能层的制备仅涉及晶圆表面几微米范围,但完整厚度的晶圆更有利于保障复杂工艺的顺利进行。直至芯片前制程完成后,晶圆才会进入封装环节进行减薄处理。

2025-05-09 13:55:51 1975

1975 圆片级封装(WLP),也称为晶圆级封装,是一种直接在晶圆上完成大部分或全部封装测试程序,再进行切割制成单颗组件的先进封装技术 。WLP自2000年左右问世以来,已逐渐成为半导体封装领域的主流技术,深刻改变了传统封装的流程与模式。

2025-05-08 15:09:36 2067

2067

随着半导体工艺复杂度提升,可靠性要求与测试成本及时间之间的矛盾日益凸显。晶圆级可靠性(Wafer Level Reliability, WLR)技术通过直接在未封装晶圆上施加加速应力,实现快速

2025-05-07 20:34:21

Entegris 先进技术应用资深处长陈柏嘉在SEMICON China 2025期间举办的先进材料论坛,发表了题为《整合式微污染控制在半导体制程中的关键角色》的主题演讲。

2025-04-30 16:35:54 847

847 在微组装工艺中,化学镀镍钯金(ENEPIG)工艺因其优异的抗“金脆”和“黑焊盘”性能,成为高可靠性电子封装的关键技术。然而,其键合强度的长期可靠性仍需系统验证。本文科准测控小编将基于Alpha

2025-04-29 10:40:25 945

945

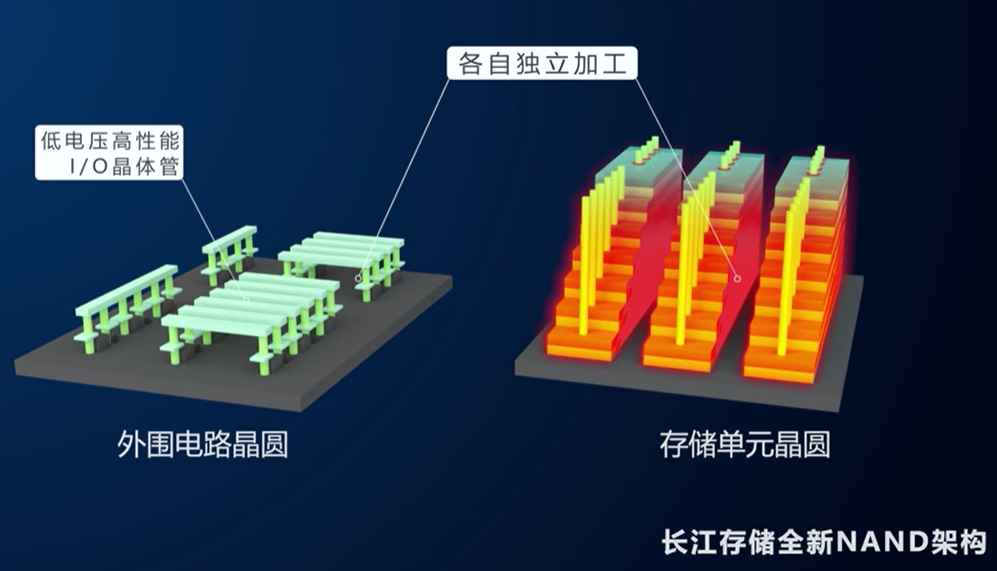

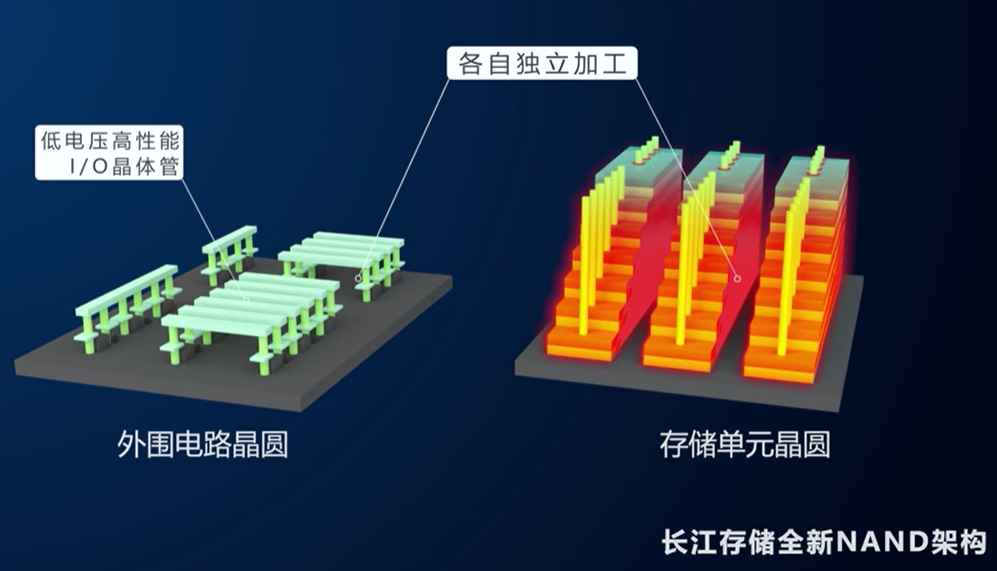

客户对HBM的要求为增加带宽、提高功率效率、提高集成度。混合键合就是可以满足此类需求的技术。 混合键合技术预计不仅可应用于HBM,还可应用于3D DRAM和NAND Flash。SK海力士副总裁姜志浩(音译)表示,“目前的做法是分别创建DRAM单元区域和外围区域,

2025-04-17 00:05:00 1060

1060 芯片封装作为半导体制造的核心环节,承担着物理保护、电气互连和散热等关键功能。其中,键合技术作为连接裸芯片与外部材料的桥梁,直接影响芯片的性能与可靠性。当前,芯片封装领域存在引线键合、倒装芯片、载带

2025-04-11 14:02:25 2627

2627

在摩尔定律逼近物理极限的当下,先进封装技术正成为半导体行业突破性能瓶颈的关键路径。以系统级封装(SiP)、晶圆级封装(WLP)、3D堆叠、Chiplet异构集成为代表的颠覆性方案,正重新定义芯片性能

2025-04-10 14:36:31 1188

1188

芯片封装是半导体制造的关键环节,承担着为芯片提供物理保护、电气互连和散热的功能,这其中的键合技术(Bonding)就是将晶圆芯片固定于基板上。

2025-04-10 10:15:38 2838

2838

近日,NVIDIA 宣布了 NVIDIA RTX 神经网络渲染技术的突破性增强功能。NVIDIA 与微软合作,将在 4 月的 Microsoft DirectX 预览版中增加神经网络着色技术,让开

2025-04-07 11:33:36 971

971 在芯片裸片制造完成后,芯片制造厂需要把其上不满了裸片的晶圆送到芯片封测厂进行切割和封装,并对芯片进行功能、性能和可靠性测试,最后在芯片封装壳上打印公司商标、芯片型号等。至此,芯片的生产过程才算全部

2025-04-04 16:01:02

此前,2025年3月26日至28日,作为中国半导体产业链的重要参与者,太极半导体(苏州)有限公司(以下简称:太极半导体)携最新封测技术亮相SEMICON China 2025,以“聚势启新章、共铸芯纪元”为主题,与全球伙伴共探行业新机遇。

2025-04-02 17:16:50 1343

1343 此前,3月26日至28日,全球半导体行业盛会SEMICON/FPD China 2025在上海隆重举办。开幕式上,长电科技董事、首席执行长,SEMI全球董事郑力发表主题演讲《开放协同,共建半导体产业新生态》。

2025-04-02 10:16:42 1183

1183 近日,为期三天的半导体盛会——SEMICON China 2025在上海新国际博览中心圆满落幕。广立微全面展示了其在EDA软件、测试设备及良率提升的综合创新能力,赢得了业内的高度关注与赞誉。

2025-04-01 10:46:18 1302

1302

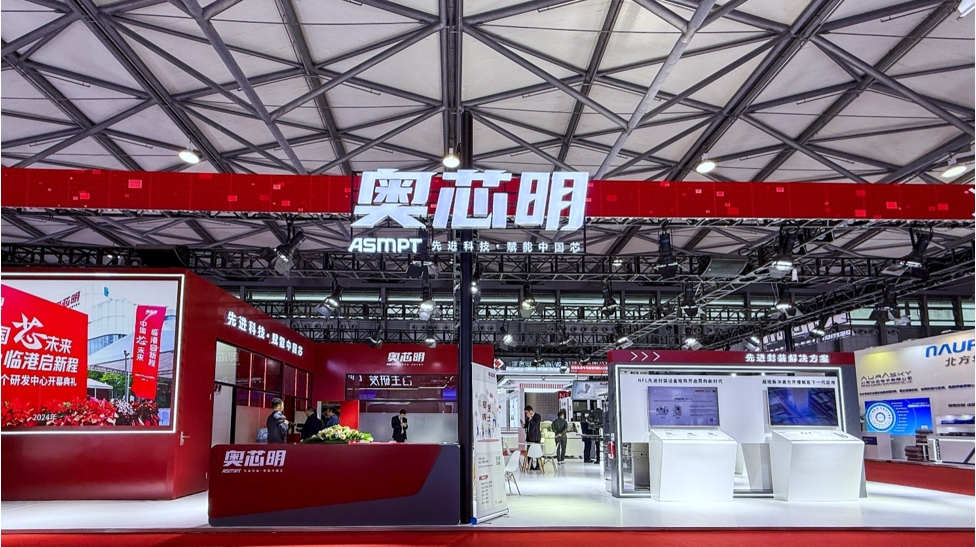

集成与电能管理四大技术板块精彩亮相。通过全系列封装设备矩阵及行业首发解决方案,奥芯明向全球展示了在封装领域的突破性进展和本土化成果,彰显了公司以创新提质、助力中国半导体产业高质量发展的坚定承诺与信心。 四大技术矩阵惊艳亮相 本届展

2025-03-31 15:34:53 889

889

全球规模最大、规格最高、最具影响力及最新技术热点全覆盖的半导体“嘉年华”—SEMICON China 2025于近日在上海正式拉开帷幕,同期举办20多场会议和活动,汇聚全球芯片设计、制造、封测、设备、材料、光伏、显示等全产业链芯力量。

2025-03-31 11:30:09 953

953 近日,全球瞩目的半导体“嘉年华”——SEMICON/FPD China 2025在上海开幕。长电科技董事、首席执行长,SEMI全球董事郑力出席开幕式并发表主题演讲“开放协同,共建半导体产业新生态”。

2025-03-31 10:25:37 1016

1016 随着轻型可穿戴设备和先进数字终端设备的需求不断增长,传统晶圆逐渐无法满足多层先进封装(2.5D/3D堆叠)的需求。它们体积较大、重量重、且在高温和大功率环境下表现欠佳,难以适应行业的快速发展。如今

2025-03-28 20:13:59 790

790 在SEMICON China 2025展会期间,中微半导体设备(上海)股份有限公司(以下简称“中微公司”,股票代码“688012.SH”)宣布其自主研发的12英寸晶圆边缘刻蚀设备Primo

2025-03-28 09:21:19 1192

1192 随着半导体工艺复杂度提升,可靠性要求与测试成本及时间之间的矛盾日益凸显。晶圆级可靠性(Wafer Level Reliability, WLR)技术通过直接在未封装晶圆上施加加速应力,实现快速、低成本的可靠性评估,成为工艺开发的关键工具。

2025-03-26 09:50:16 1548

1548

每年一度的SEMICON China将于2025年3月26-28日在上海新国际博览中心举办。同时,中国规模最大、最全面的年度半导体技术盛会——集成电路科学技术大会(CSTIC)2025也将于3月24-25日在上海国际会议中心召开。

2025-03-24 09:35:11 1340

1340 芯片封装是半导体制造的关键环节,承担着为芯片提供物理保护、电气互连和散热的功能,这其中的键合技术就是将裸芯片与外部材料连接起来的方法。键合可以通俗的理解为接合,对应的英语表达是Bonding,音译

2025-03-22 09:45:31 5448

5448

环球仪器与母公司台达电子将在3月26-28日于上海举行的SEMICON China 2025展会上,展示五大半导体自动化解决方案,提高生产效率。

2025-03-21 10:06:13 941

941 全新强力键合腔室设计,赋能更大尺寸晶圆高均匀性键合与量产良率提升 2025年3月18日,奥地利圣弗洛里安 —全球领先的半导体创新工艺解决方案和专业知识提供商,为前沿和未来的半导体设计和芯片集成

2025-03-20 09:07:58 889

889

SEMICON China 2025 将于3月26-28日在 上海新国际博览中心隆重登场。作为全球半导体行业的顶尖盛会,展会汇聚超过1000家全球知名企业,覆盖芯片设计、制造、封装测试、设备、材料等全产业链,展览面积达90000平方米,同期举办20多场高质量论坛和活动。

2025-03-13 11:37:45 1099

1099 金丝键合主要依靠热超声键合技术来达成。热超声键合融合了热压键合与超声键合两者的长处。通常情况下,热压键合所需温度在300℃以上,而在引入超声作用后,热超声键合所需温度可降至200℃以下。如此一来

2025-03-12 15:28:38 3656

3656

2025年3月11日,香港——中国半导体键合集成技术领域的领先企业青禾晶元半导体科技(集团)有限责任公司(简称“青禾晶元”)宣布,正式推出全球首台C2WW2W双模式混合键合设备SAB8210CWW上

2025-03-12 13:43:56 1036

1036

3月26-28日,2025 SEMICON China即将在上海新国际博览中心隆重开幕。届时,概伦电子将携应用驱动的半导体参数测试平台和解决方案亮相,现场还将全新发布先进宽带噪声分析仪9812HF,刷新半导体测试标准。诚邀您莅临概伦展台,共同见证半导体量测技术的突破创新。

2025-03-11 15:58:28 821

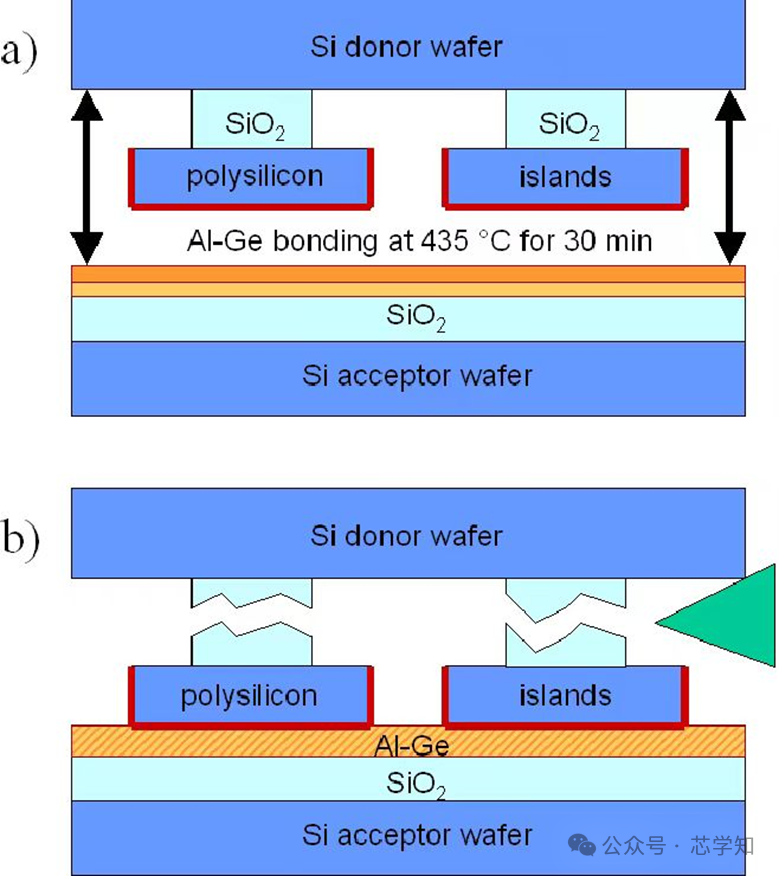

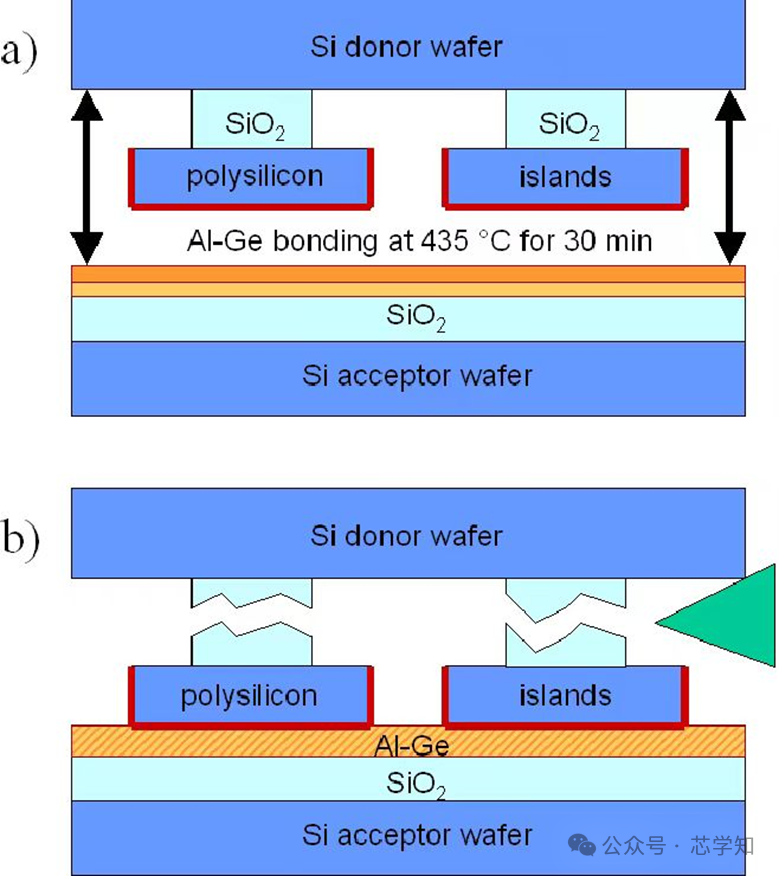

821 键合技术主要分为直接键合和带有中间层的键合。直接键合如硅硅键合,阳极键合等键合条件高,如高温、高压等。而带有中间层的键合,所需的温度更低,压力也更小。带金属的中间层键合技术主要包括共晶键合、焊料键合、热压键合和反应键合等。本文主要对共晶键合进行介绍。

2025-03-04 17:10:52 2627

2627

金属共晶键合是利用金属间的化学反应,在较低温度下通过低温相变而实现的键合,键合后的金属化合物熔点高于键合温度。该定义更侧重于从材料科学的角度定义。

2025-03-04 14:14:41 1921

1921

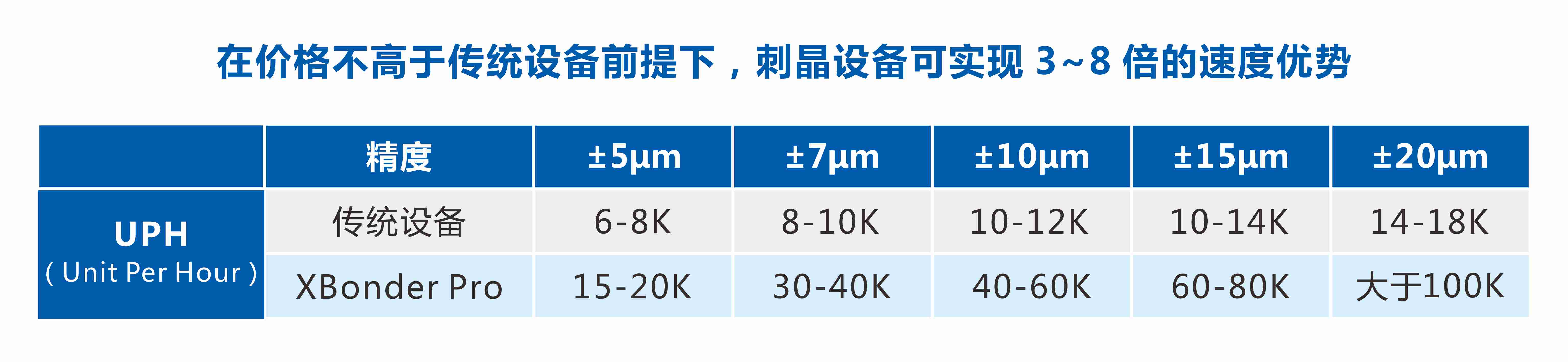

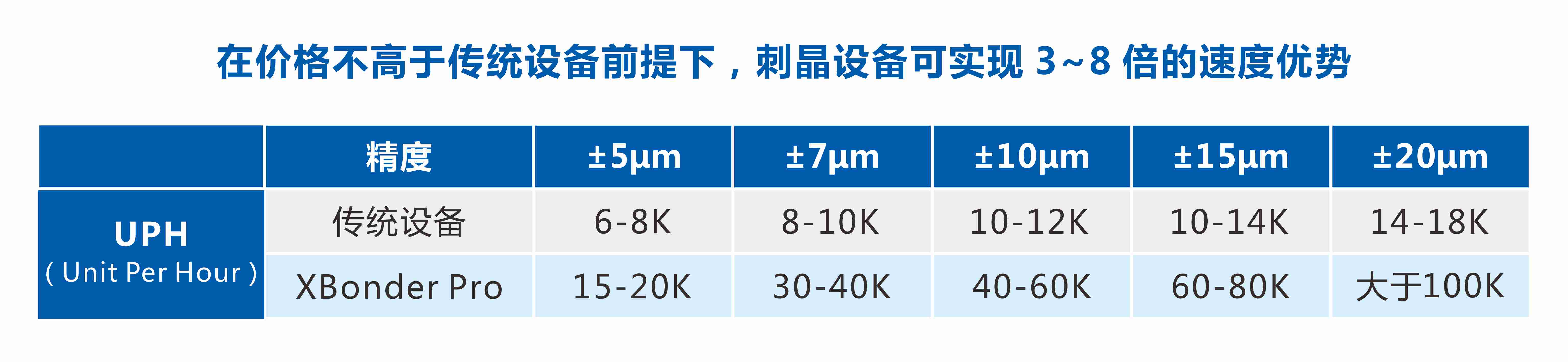

经过半年的测试,普莱信智能和某顶级封装厂就其巨量转移式板级封装设备(FOPLP)设备XBonder Pro达成战略合作协议,这将是巨量转移技术在IC封装领域第一次规模化的应用,将掀起晶圆级封装和板级

2025-03-04 11:28:05 1186

1186

随着半导体技术的飞速发展,晶圆级封装(WLP)作为先进封装技术的重要组成部分,正逐渐成为集成电路封装的主流趋势。在晶圆级封装过程中,Bump工艺扮演着至关重要的角色。Bump,即凸块,是晶圆级封装中

2025-03-04 10:52:57 4978

4978

铜引线键合由于在价格、电导率和热导率等方面的优势有望取代传统的金引线键合, 然而 Cu/Al 引线键合界面的金属间化合物 (intermetallic compounds, IMC) 的过量生长将增大接触电阻和降低键合强度, 从而影响器件的性能和可靠性。

2025-03-01 15:00:09 2398

2398

电子发烧友网综合报道,据韩媒报道,三星近日与长江存储签署了3D NAND混合键合专利许可协议,从第10代V-NAND开始,将使用长江存储的专利技术,特别是在“混合键合”技术方面。 W2W技术是指

2025-02-27 01:56:00 1037

1037

3D-IC通过采用TSV(Through-Silicon Via,硅通孔)技术,实现了不同层芯片之间的垂直互连。这种设计显著提升了系统集成度,同时有效地缩短了互连线的长度。这样的改进不仅降低了信号传输的延时,还减少了功耗,从而全面提升了系统的整体性能。

2025-02-21 15:57:02 2460

2460

(InFO) 封装这样的 3D 扇出封装方法,则更侧重于手机等大规模消费应用。此外,所有主流设计公司、晶圆代工厂和封测代工厂 (OSAT) 都在投资新一代技术——使用硅通孔 (TSV) 和混合键合的真正裸片堆叠。

2025-02-20 11:36:56 1271

1271

的关键技术之一,它不仅能够保护MEMS器件免受外部环境的影响,还能提高器件的性能和可靠性。Au-Sn共晶键合技术作为一种先进的封装技术,在MEMS气密性封装中展现出

2025-01-23 10:30:52 2886

2886

扇出型晶圆级中介层封装( FOWLP)以及封装堆叠(Package-on-Package, PoP)设计在移动应用中具有许多优势,例如低功耗、短信号路径、小外形尺寸以及多功能的异构集成。此外,它还

2025-01-22 14:57:52 4507

4507

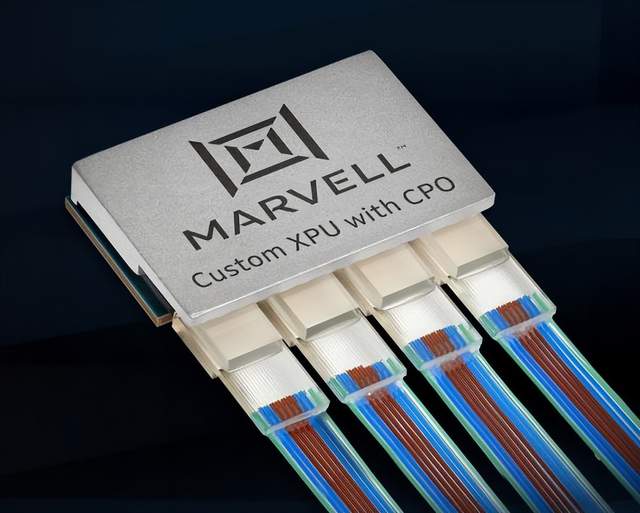

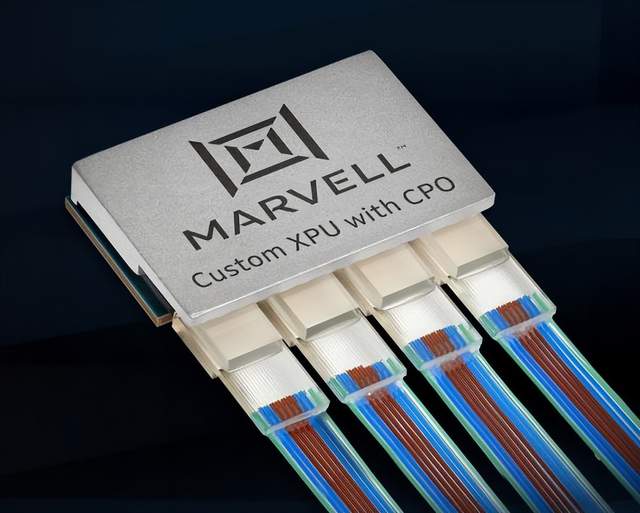

突破性CPO架构为人工智能领域的发展注入新的活力,也促使我们深入探究CPO技术给互连产品究竟会带来怎样的影响。 1 月 6 日,美国芯片大厂Marvell宣布重大突破,将共封装光学架构(CPO

2025-01-17 15:00:12 1348

1348

。 2.5D封装将die拉近,并通过硅中介连接。3D封装实际上采用2.5D封装,进一步垂直堆叠die,使die之间的连接更短。通过这种方式直接集成IC,IC间通信接口通常可以减少或完全消除。这既可以提高性能,又可以减轻重量和功耗。 这种封装的复杂性需要新颖的封装和测试技术。 了解2.5D封装与3

2025-01-14 10:41:33 2902

2902

本文主要介绍功率器件晶圆测试及封装成品测试。 晶圆测试(CP) 如图所示为典型的碳化硅晶圆和分立器件电学测试的系统,主要由三部分组成,左边为电学检测探针台阿波罗

2025-01-14 09:29:13 2358

2358

混合键合技术(下) 先进封装技术(Semiconductor Advanced Packaging) - 3 Chiplet 异构集成(上) 先进封装技术(Semiconductor

2025-01-08 11:17:01 3031

3031

随着半导体技术的飞速发展,晶圆级封装(Wafer Level Packaging, WLP)作为一种先进的封装技术,正逐渐在集成电路封装领域占据主导地位。晶圆级封装技术以其高密度、高可靠性、小尺寸

2025-01-07 11:21:59 3190

3190

生电子共享或原子的相互扩散,从而使两种金属间实现原子量级上的键合。图1在IC封装中,芯片和引线框架(基板)的连接为电源和信号的分配提供了电路连接。有三种方式实现内部连

2025-01-06 12:24:10 1964

1964

电子发烧友App

电子发烧友App

评论