以下文章来源于漫谈大千世界,作者CosmosWanderer

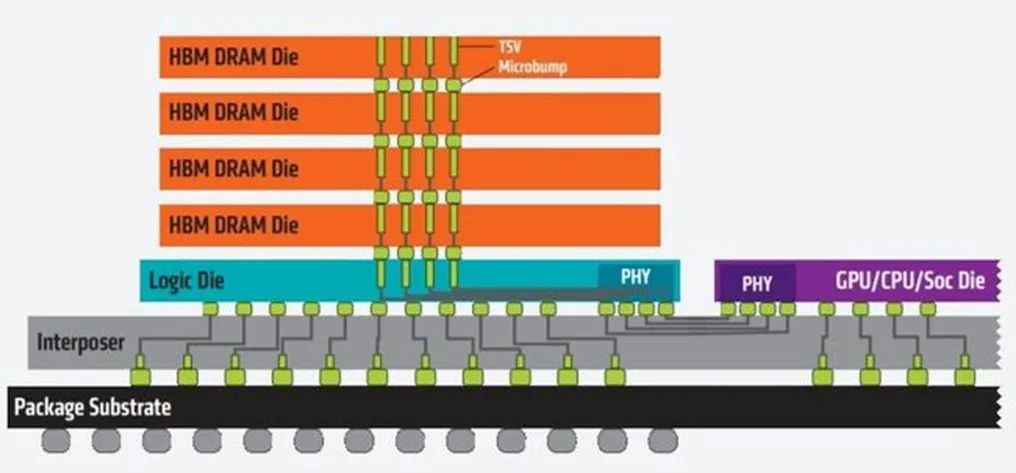

3D-IC通过采用TSV(Through-Silicon Via,硅通孔)技术,实现了不同层芯片之间的垂直互连。这种设计显著提升了系统集成度,同时有效地缩短了互连线的长度。这样的改进不仅降低了信号传输的延时,还减少了功耗,从而全面提升了系统的整体性能。

根据TSV制作工艺顺序的不同,可分为先通孔和后通孔两种技术。

FE3D: 先通孔是指先刻蚀通孔,再装配到操作晶圆上,然后减薄,即在CMOS器件或者后道互连之前的设计阶段介入。

BE3D: 后通孔是指先将晶圆键合到另一个芯片/晶圆上,然后再刻蚀通孔,即在后道互连或者键合之后的后期开始。

1. 3D IC的堆叠方式

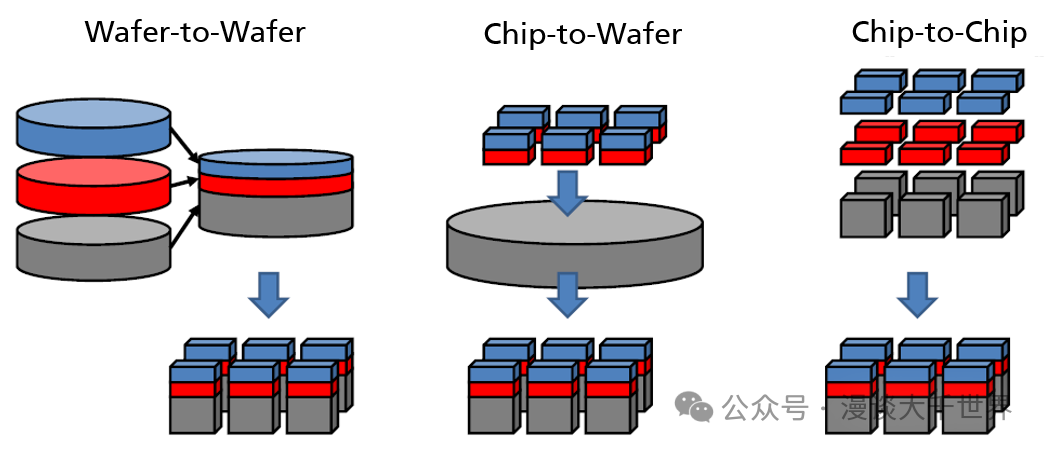

基于TSV(Through-Silicon Via,硅通孔)技术的3D IC堆叠方式主要有三种类型,每种类型都有其特点和应用场景。

晶圆到晶圆堆叠(Wafer-to-Wafer, W2W)

两个晶圆均没有切片;工艺简单,产出效率最高,成本最低

这个名称也有称为Wafer on Wafer,WoW

晶片到晶圆堆叠(Die-to-Wafer, D2W)

将切片后的晶片堆叠到晶圆上。这种方式相比W2W,可能在良率上有所提高,因为可以对单个晶片进行筛选。工艺相对简单,成本和产出效率介于W2W和D2D之间。

这个名称也有称为Chip on Wafer,CoW

晶片到晶片堆叠(Die-to-Die, D2D)

将切片后的两层晶片堆叠在一起。这种方式可以使用已知良晶片(Known-Good-Die, KGD),因而良率最高。但是工艺最复杂,产出效率最低,因为需要对每个晶片进行精确的对准和堆叠。

这个名称也有称为C2C.

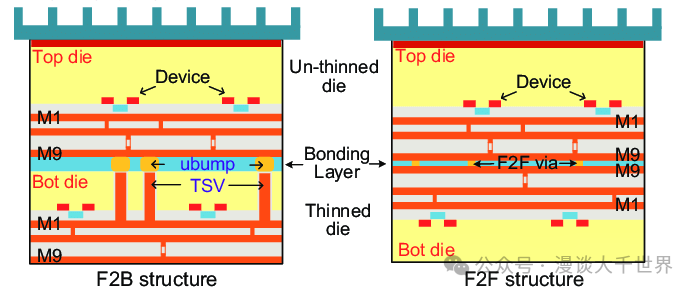

2. 3D IC的堆叠方向

无论晶圆是否切片,3D IC堆叠方向分为三种.

面对面(Face-to-Face, F2F)

面对背(Face-to-Back, F2B)

背对背(Back-to-Back, B2B)

3. 基于TSV的3D IC关键集成技术

3D IC集成的关键技术主要包括以下几个方面:

对准(Alignment)

对准(Alignment)是3D IC制造过程中的一个关键步骤,它确保了在不同层的芯片或晶圆堆叠时,各个层之间的电路图案能够精确地对齐。这种精确对齐对于实现电气连接的可靠性和功能性至关重要。对准技术的准确性直接影响到3D IC的性能、产量和可靠性。

对准(Alignment)可以采用直接或者间接的方式进行对准。如果两个硅片中有一个是对可见光或者红外线透明的,就可以采用直接对准。当两个硅片都不对可见光或者红外线透明时,就必须采用间接对准方式。在这种情况下,先将第一个硅片对准到一个参考点上再抬高一定的距离,然后再将第二层硅片对准到同一个参考点上。当然间接对准没有直接对准的精确度高。

键合(Bonding)

键合技术是指借助各种化学和物理作用连接两个或多个芯片或晶圆。目前有四种键合技术是最常用的,分别是氧化物键合、金属键合、粘合剂键合和焊接。

氧化物键合:利用上下两层芯片表面的隔离层(通常是SiO₂)进行键合。这种技术的优点是可以在低温下进行,且与半导体工艺兼容。但是,它需要高质量的化学机械抛光和复杂的硅片清洁。

金属键合:可以使用铜或金作为金属材料。金比铜更容易键合,所需温度和压力较小。铜键合成本低,键合强度高,与半导体工艺兼容。金属键合的主要优势是可以同时实现机械和电连接,且过程中不产生多余气体。但对工艺温度和压力的要求较高,且可能因温度不一致导致对准误差。常用的金属键合可控塌陷芯片连接(Controlled Collapse Chip Connect, C4)和薄膜键合。

粘合剂键合:使用粘合剂来连接衬底或晶圆。典型的粘合剂键合是伦斯勒理工学院研发的聚合物键合技术。

焊接是一种在印刷电路板上广泛应用的技术,也可以用于3D IC集成 。它像金属键合一样,也可以同时实现机械连接和电连接。

晶圆减薄(Wafer Thinning)

在堆叠之前,需要将晶圆减薄到合适的厚度,以减少堆叠后的总厚度,提高封装的紧凑性和散热性能。

目前的金属淀积及等离子体开孔工艺而言,要求上层芯片的TSV高度控制在几十微米以内,以确保TSV的工艺可靠性。

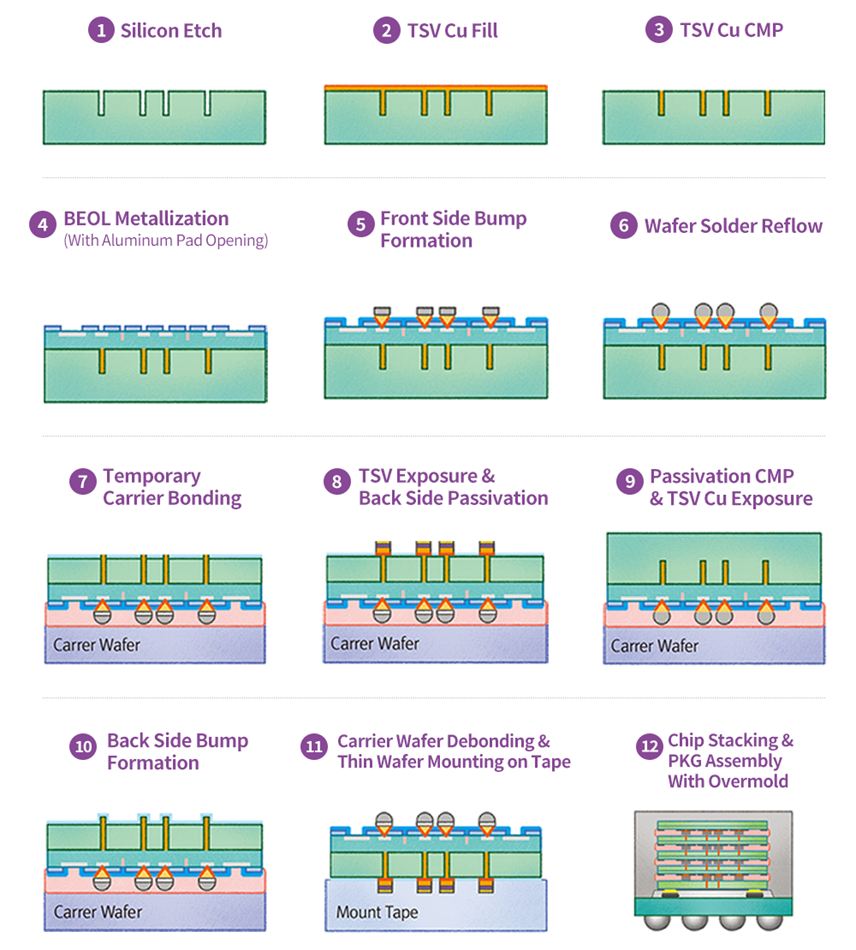

TSV(Through-Silicon Via)

TSV是实现3D IC垂直互连的关键技术,通过在硅片中钻孔并填充导电材料来实现不同层之间的电气连接。根据TSV制作工艺顺序的不同,可分为先通孔和后通孔两种技术。

FE3D: 先通孔是指先刻蚀通孔,再装配到操作晶圆上,然后减薄,即在CMOS器件或者后道互连之前的设计阶段介入。

FE3D: 先通孔是指先刻蚀通孔,再装配到操作晶圆上,然后减薄,即在CMOS器件或者后道互连之前的设计阶段介入。

键合技术包括直接键合、使用中间层(如硅中介层)的键合、以及使用微凸点(microbumps)等。

TSV的制造涉及到深反应离子刻蚀(DRIE)、绝缘层沉积、金属填充等多个步骤。

这些关键技术相互配合,共同实现了3D IC的高密度集成、高性能和小型化。随着技术的发展,3D IC在移动设备、高性能计算、人工智能等领域的应用越来越广泛。

-

芯片

+关注

关注

462文章

53550浏览量

459257 -

IC

+关注

关注

36文章

6267浏览量

184287 -

晶圆

+关注

关注

53文章

5348浏览量

131703 -

TSV

+关注

关注

4文章

136浏览量

82382

原文标题:基于TSV的3D-IC

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

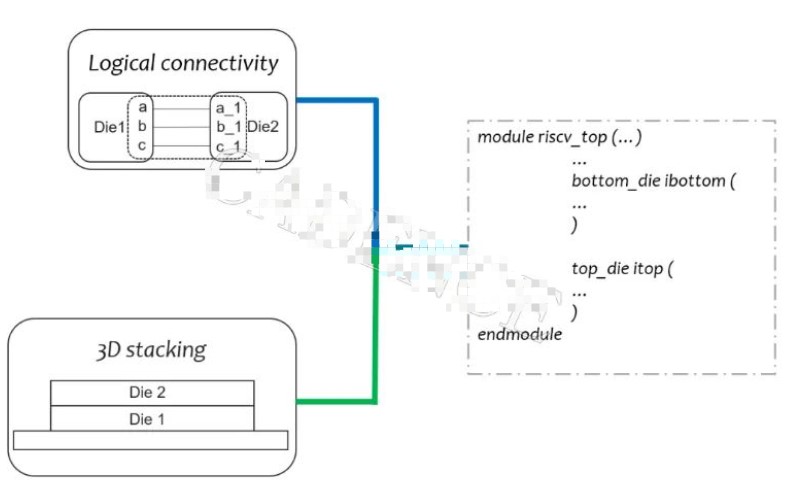

如何建立正确的3D-IC设计实现流程和实现项目高效管理的挑战

3D-IC设计之系统级版图原理图一致性检查

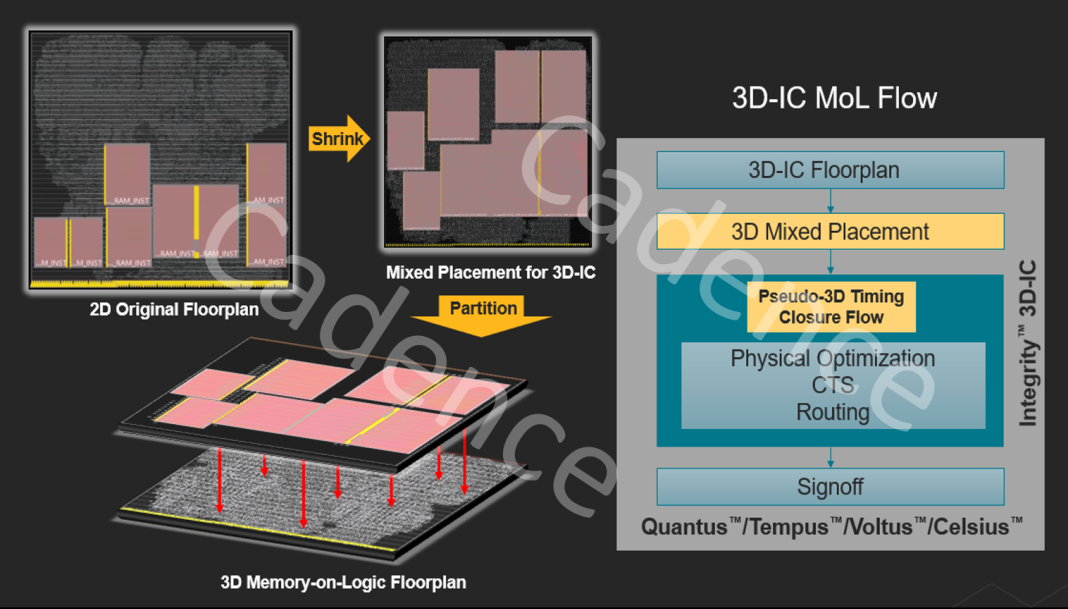

Cadence 凭借突破性的 Integrity 3D-IC 平台加速系统创新

新思科技推出3D-IC新技术

TSMC 和 Cadence 合作开发3D-IC参考流程以实现真正的3D堆叠

Cadence Integrity 3D-IC平台Ô支持TSMC 3DFabric技术,推进多Chiplet设计

Integrity™3D-IC平台助力设计者实现驱动PPA目标

Cadence Integrity 3D-IC自动布线解决方案

3D-IC未来已来

产品资讯 | 3D-IC 设计之自底向上实现流程与高效数据管理

基于TSV的3D-IC关键集成技术

基于TSV的3D-IC关键集成技术

评论