在半导体产业持续追求高性能、小型化的进程中,晶圆级封装(WLP)凭借其卓越的电气性能和尺寸优势,已成为先进封装技术的关键领域。锡膏作为晶圆级封装中实现电气连接与机械固定的核心材料,其性能与应用直接关乎封装质量与芯片可靠性。作为锡膏厂家,傲牛科技的工程师将在本文中,深入剖析晶圆级封装中锡膏的应用场景、类型选择与性能要求,并介绍我司在该领域的前沿产品与解决方案。

一、晶圆级封装工艺中的锡膏应用环节

晶圆级封装涵盖多种先进工艺,如扇入型(Fan - In)、扇出型(Fan - Out)、倒装芯片(Flip Chip)及硅通孔(TSV)封装等。在这些工艺中,锡膏主要应用于以下关键环节:

- 凸点(Bump)制作:在倒装芯片和扇入型晶圆级封装中,通过钢网印刷将锡膏精确沉积在芯片焊盘或晶圆表面,经回流焊形成具有特定高度与形状的焊料凸点,为芯片与基板的互连提供可靠接口。例如,在0.1mm以下细间距的倒装芯片封装中,锡膏印刷的精度与一致性对凸点质量至关重要。

- 植球工艺:扇出型晶圆级封装在重新布线层(RDL)制作完成后,需借助锡膏将锡球精确植于RDL焊盘上,实现芯片与外部电路的电气连接。这一过程要求锡膏具备良好的触变性与润湿性,以确保锡球在回流后位置准确、焊点牢固。

- 芯片与基板互连:无论是何种晶圆级封装形式,最终都需通过锡膏焊接实现芯片与基板(或载板)的可靠互连。在这一环节,锡膏需在不同材料(如硅芯片、有机基板、陶瓷基板)表面形成良好的冶金结合,保障电气信号高效传输与机械结构稳定。

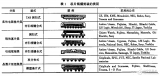

二、晶圆级封装常用锡膏类型

随着无铅化趋势的推进,晶圆级封装领域广泛采用无铅锡膏,主要体系包括:

- Sn-Ag-Cu(SAC)体系锡膏:以其优良的机械性能、较高的熔点(217 - 221℃)和良好的润湿性,成为高端应用的首选。例如,在5G通信芯片、高性能计算芯片的晶圆级封装中,SAC体系锡膏能够满足高频信号传输对焊点可靠性与稳定性的严苛要求。

- Sn-Cu体系锡膏:成本相对较低,且具备较好的焊接性能,在对成本敏感的消费电子芯片封装中应用广泛。其熔点约227℃,在一些对工作温度要求不高的场景中,能有效平衡成本与性能。

- Sn-Bi体系锡膏:具有较低的熔点(约139℃),适用于热敏元件或多层堆叠封装中的低温焊接工艺。在可穿戴设备芯片封装中,由于对功耗与散热要求较高,Sn-Bi体系锡膏可在较低温度下完成焊接,减少对周边元件的热影响。

三、晶圆级封装对锡膏的性能要求

- 高精度印刷性能:针对晶圆级封装的细间距(<0.2mm)、高密度特点,锡膏需具备优异的触变性,在印刷过程中能迅速填充钢网开孔,并在印刷后保持形状稳定,避免塌落与桥连。例如,对于0.15mm间距的晶圆级CSP封装,锡膏印刷的偏差需控制在±5μm以内。

- 良好的润湿性:锡膏需在不同金属表面(如铜、镍、金)迅速铺展,形成牢固的冶金结合,确保焊点的电气与机械性能。润湿性不良会导致虚焊、开路等缺陷,影响封装成品率与可靠性。

- 高可靠性焊点:在高温、高湿、振动等复杂工作环境下,焊点需保持长期稳定。锡膏应具备低空洞率、高抗疲劳性能,以满足汽车电子、航空航天等领域对芯片可靠性的严苛要求。例如,汽车发动机控制单元芯片的晶圆级封装,焊点需经受1000次以上的高低温循环测试。

- 低残留与易清洗性:焊接后,锡膏残留应尽量少,且易于清洗,避免残留物质对芯片性能产生影响,如腐蚀、漏电等。特别是在医疗电子芯片封装中,对锡膏残留的控制尤为严格。

四、傲牛科技锡膏产品在晶圆级封装中的优势

作为专业的封装材料生产企业,傲牛科技深耕锡膏领域多年,为晶圆级封装提供了一系列高性能产品,具有显著优势:

- 卓越的印刷精度:我公司采用先进的配方与生产工艺,使锡膏具有极佳的触变性与流动性控制,在超精细间距印刷中表现出色。例如,针对0.1mm间距的倒装芯片封装,我司锡膏的印刷精度可达±3μm,远超行业平均水平,有效降低了印刷缺陷率。

- 优化的润湿性配方:通过对合金成分与助焊剂体系的深入研究,我公司锡膏在多种金属表面均能实现快速、充分的润湿,焊点饱满、光亮,结合强度高。在实际应用中,相比同类产品,我司锡膏的焊点抗剪切强度提升了20%,极大提高了封装的可靠性。

- 高可靠性焊点保障:锡膏在研发过程中充分考虑了不同应用场景的可靠性需求,通过添加特殊合金元素与优化微观结构,尤其是我公司最新与日本材料科技公司联合开发的低空洞抑制技术,显著降低了焊点空洞率,提高了抗疲劳性能。

- 低残留与环保清洗方案:我公司致力于绿色环保封装材料的研发,锡膏焊接后残留少,且采用环保型助焊剂体系,易于清洗。配套的清洗工艺与清洗剂,能在不损伤芯片与封装结构的前提下,彻底清除残留,满足医疗、航天等对清洁度要求极高的应用场景。

在晶圆级封装技术蓬勃发展的当下,锡膏作为核心封装材料的重要性不言而喻。凭借在锡膏研发、生产方面的深厚积累与技术创新,傲牛科技为客户提供了全方位、高性能的解决方案,助力半导体产业迈向更高性能、更小尺寸、更可靠的封装新时代。期待与广大客户携手合作,共同探索晶圆级封装的无限可能,为行业发展贡献力量。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

锡膏

+关注

关注

1文章

1000浏览量

18359 -

晶圆级封装

+关注

关注

5文章

47浏览量

11823 -

FOWLP

+关注

关注

1文章

18浏览量

10202 -

FOWLP封装

+关注

关注

0文章

4浏览量

2989

发布评论请先 登录

相关推荐

热点推荐

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)

工艺技术的研究,由深圳市华芯邦科技有限公司(Hotchip)提出,可解决元器件散热、可靠性、成本、器件尺寸等问题,是替代传统封装技术解决方案之一。本文总结了HRP工艺的封装特点和优势,详细介绍其工艺实现路线,为传统

提供半导体工艺可靠性测试-WLR晶圆可靠性测试

随着半导体工艺复杂度提升,可靠性要求与测试成本及时间之间的矛盾日益凸显。晶圆级可靠性(Wafer Level Reliability, WL

发表于 05-07 20:34

晶圆级封装的 “隐形基石”:锡膏如何决定芯片可靠性?

晶圆级封装的 “隐形基石”:锡膏如何决定芯片可靠性?

评论