以下文章来源于十二芯座,作者MicroX

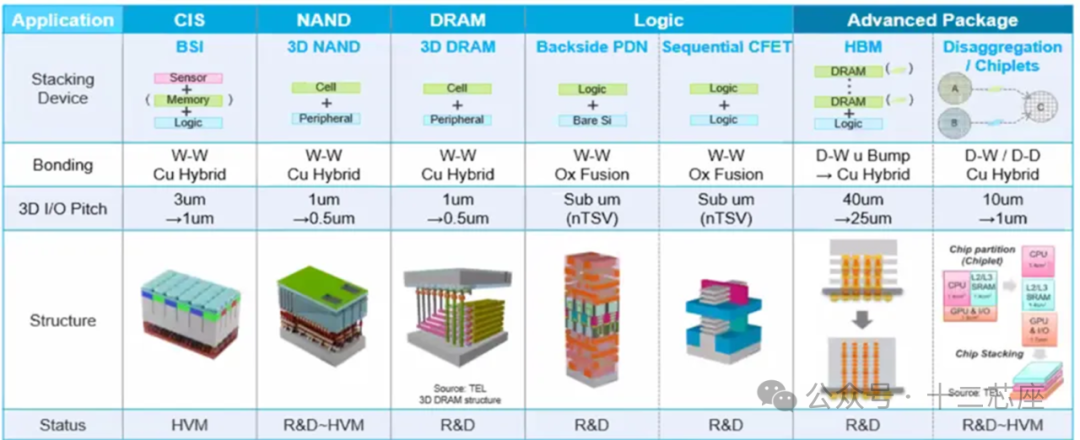

在先进封装中,Hybrid bonding(混合键合)不仅可以增加I/O密度,提高信号完整性,还可以实现低功耗、高带宽的异构集成。它是主要3D封装平台(如台积电的SoIC、三星的X-Cube和英特尔的fooveros)背后的基础技术。展望未来,随着逻辑和内存堆叠变得更加紧密耦合,带宽需求不断增加,键合技术只会变得越来越重要,成为芯片和系统层面创新的关键推动者。

技术原理与架构特点

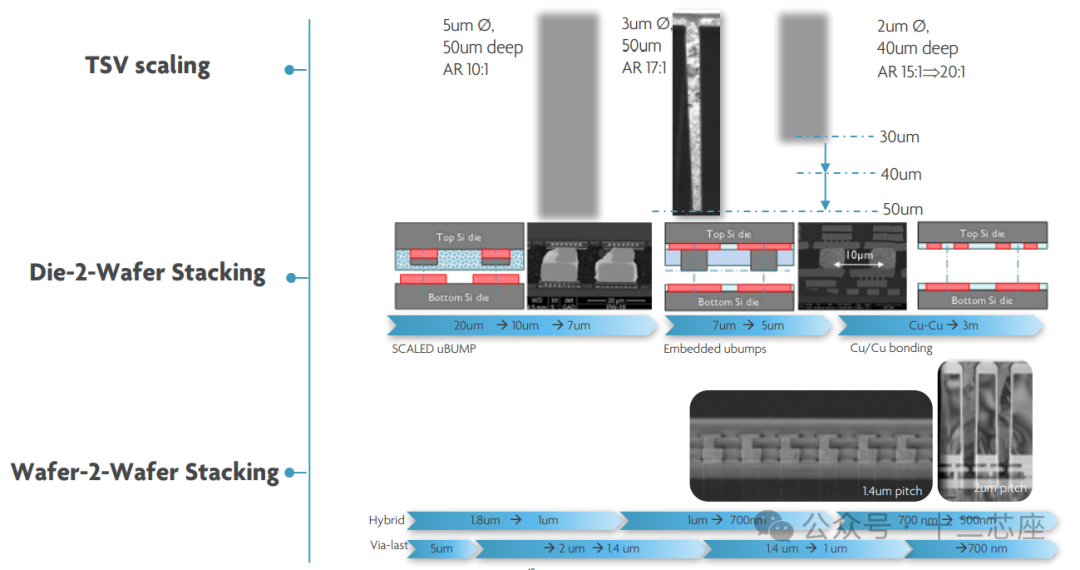

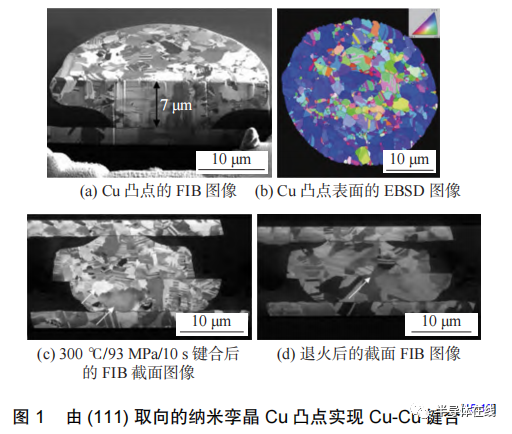

Hybrid bonding 是一种以无凸点互连结构为特征的半导体堆叠技术。与传统的基于焊料的封装不同,混合键合通过直接的铜对铜(Cu-Cu)接触实现电气和机械互连。上下芯片紧密键合,其间仅有被介质材料封装的超细图案化铜焊盘。这些铜焊盘的间距通常低于10微米,并通过硅通孔(TSVs)连接到芯片内部的金属层,形成完整的信号和电源路径。

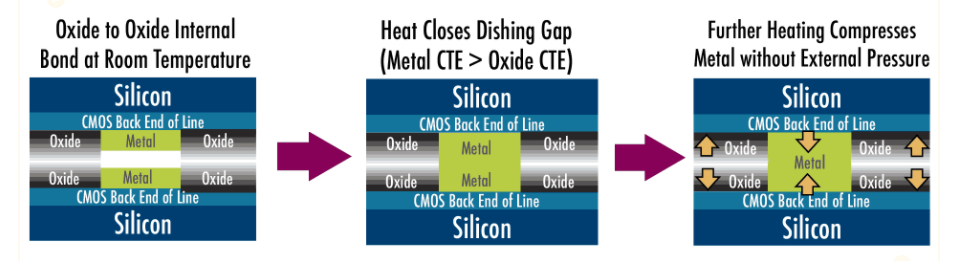

“混合”一词指的是介电对介电的分子键合和金属对金属的铜键合的结合,两者均无需粘合剂。这使得界面更加稳定,损耗更低,具有卓越的电气和热性能。

技术优势与系统级益处

Hybrid bonding 提供了众多的技术和系统级优势,从根本上重塑了芯片设计和系统架构:

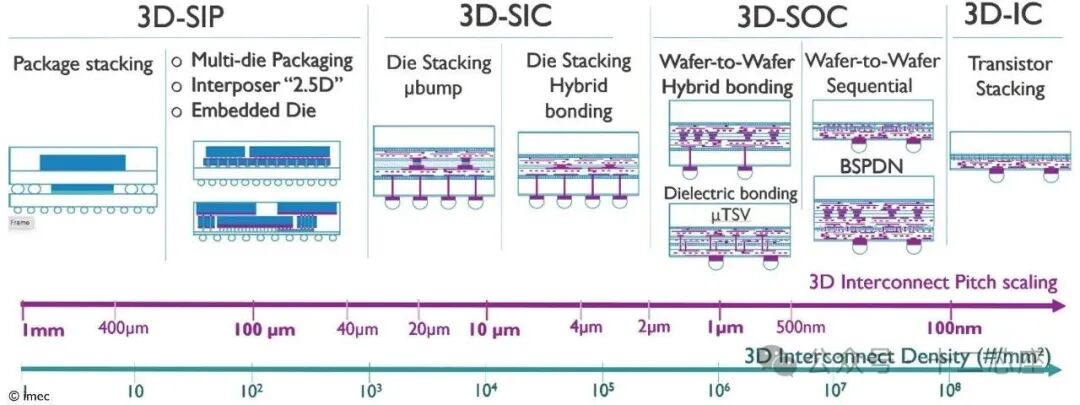

超高互连密度:能够在低于10微米甚至达到数百纳米的范围内实现垂直互连,远远超过传统凸点方法的密度。

低电阻和低功耗:消除焊料凸点显著降低了互连电阻,提高了能效和热性能——这对于高速数据路径至关重要。

低延迟和短互连:极大地缩短了信号路径,使其接近芯片内部的距离,提高了性能,特别是在人工智能、近内存计算和3D缓存架构中。

架构创新:高密度互连使设计人员能够对芯片功能进行模块化和异构集成,克服了单芯片面积和产量的限制。

制造挑战与关键工艺控制

尽管 Hybrid bonding 具有变革性潜力,但它带来了严格的工艺要求。关键因素包括:

表面平整度:键合界面极其敏感于微尺度粗糙度。介电表面要求粗糙度小于0.5纳米,铜焊盘小于1纳米。这需要化学机械抛光(CMP)作为关键步骤。

清洁度和颗粒控制:即使是1微米的颗粒也可能导致毫米级区域的键合失败。混合键合需要ISO 3级或更好的洁净室环境,使其在清洁度需求上更接近前端晶圆厂。

对准精度:晶圆对晶圆(W2W)键合系统必须实现低于50纳米的对准精度,集成高分辨率光学元件和精确的机械定位。键合压力和停留时间也必须严格控制,以实现初始的范德华键合(van der Waals bonding)和随后的铜对铜键合(Cu-Cu bonding)。

工艺概述

Hybrid bonding 以晶圆对晶圆(W2W)或芯片对晶圆(D2W)的形式实现,遵循以下一般步骤:

TSV形成:通过硅通孔在基底晶圆中建立信号和电源路径。

键合层制造:在晶圆顶部沉积介电层(例如二氧化硅或碳氮化硅)并图案化铜焊盘。

CMP抛光:对两个键合表面进行抛光,以满足纳米级平整度要求。

表面激活和清洁:用等离子体(例如氮气)处理以激活表面,随后用去离子水冲洗。

对准和预键合:使用先进的定位系统对准晶圆,并施加低压力键合以启动介电粘附。

热退火:应用受控的热处理以形成铜对铜金属键,最终完成混合界面。

W2W与D2W工艺选择

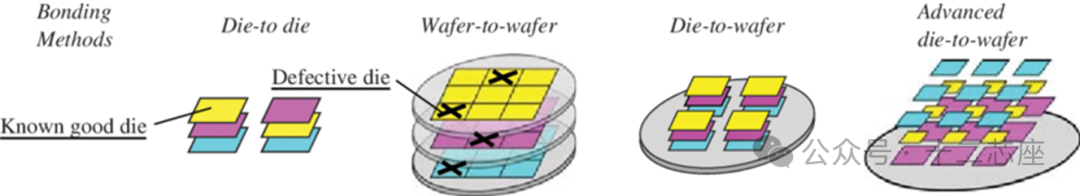

W2W:适用于高产量、小面积芯片;具有对准和吞吐量优势。常见于图像传感器和3D NAND。

D2W:适用于大型或复杂芯片,使用经过晶圆分类后的已知良好芯片(KGD)。技术上具有挑战性,但能够实现模块化和异构集成。AMD的3D V-Cache(SoIC)是使用D2W混合键合的突出例子。

Wafer to wafer:指的是将两个完整的晶圆(wafer)直接进行键合或连接。

Die to wafer:则是指将单个芯片(die)与另一个完整的晶圆进行键合或连接。

-

半导体

+关注

关注

339文章

31241浏览量

266585 -

键合

+关注

关注

0文章

107浏览量

8305 -

先进封装

+关注

关注

2文章

562浏览量

1062

原文标题:先进封装中的混合键合技术:CIS/NAND/DRAM/Logic/Advanced package

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

详解先进封装中的混合键合技术

详解先进封装中的混合键合技术

评论