来源:学习那些事

作者:前路漫漫

扇出型晶圆级封装(FOWLP)技术

FOWLP技术概述

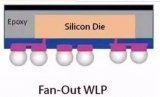

常规IC封装需经过将晶圆与IC封装基板焊接,再将IC基板焊接至普通PCB的复杂过程。与之不同,WLP基于IC晶圆,借助PCB制造技术,在晶圆上构建类似IC封装基板的结构,塑封后可直接安装在普通PCB上 。这种创新的封装方式自苹果A10处理器采用后,在节约主板表面面积方面成效显著。根据线路和焊脚与芯片尺寸的关系,WLP分为Fanin WLP(线路和焊脚限定在芯片尺寸以内)和Fanout WLP(可扩展至芯片尺寸之外,甚至实现芯片叠层) 。

a)IC封装 b)WLP

FOWLP技术特点

FOWLP突破了传统封装的限制,在面积扩展的同时,能够灵活地加入有源和/或无源器件,进而形成系统级封装(SIP)。相较于常规封装技术,它具备一系列显著优势。首先,可大幅增加I/O接口密度,满足芯片日益增长的信号传输需求;其次,为SiP技术的延伸提供有力支持,促进系统集成度的提升;再者,拥有更优良的电气性能,信号传输损耗更低,以及出色的热性能,能有效散热,确保芯片在高负载运行时的稳定性;此外,其可靠性更高,封装线路更精细,为实现高性能、小型化的芯片封装奠定了坚实基础 。

FOWLP工艺流程

一、基本工艺流程

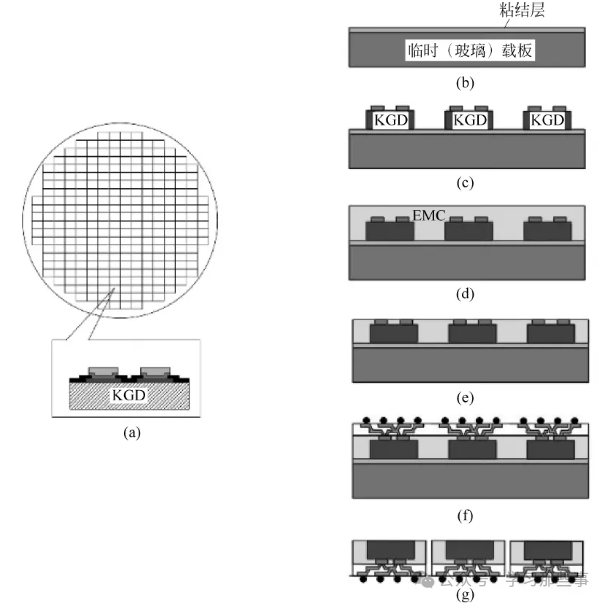

FOWLP的制作涵盖重构晶圆、再布线、植球、切割等关键工艺步骤。其中,重构晶圆技术是FOWLP的核心,它决定了封装的整体架构和性能。而RDL技术及凸点技术与WLCSP相近,在实现芯片电气连接和信号传输方面发挥着重要作用。依据重构晶圆所用主要材料的差异,FOWLP可划分为树脂型、玻璃基和硅基FOWLP 。当下,树脂型FOWLP凭借其成本效益和工艺成熟度,成为主流的封装形式,并进一步细分为芯片先装/面朝下、芯片先装/面朝上和芯片后装/先RDL三种工艺类型。

二、树脂型FOWLP工艺

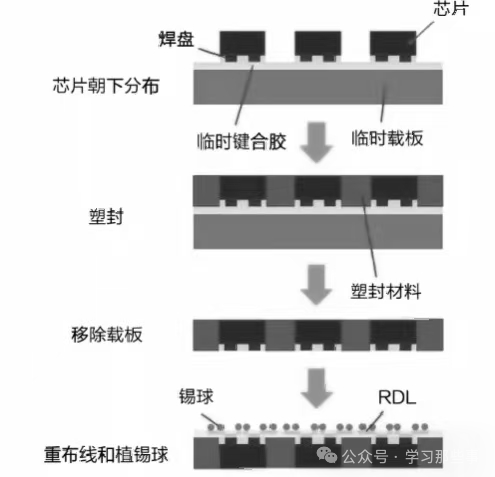

1.芯片先装/面朝下工艺步骤

1)在临时载板上均匀涂覆黏结层,为后续芯片的固定提供基础支撑。

2)对芯片进行严格测试,确保其性能达标后,将芯片面朝下精准排布到载板上,严格控制芯片位置,保证准确无误。

3)运用EMC(环氧模塑料)材料,通过模压成型工艺制作重构晶圆,并进行固化处理,使芯片与载板牢固结合为一体。

4)固化完成后,去除载板和黏结层,为后续工序创造条件。

5)在晶圆表面制作再布线层,实现芯片电气连接的重新布局,以满足封装的电气性能需求。

6)在再布线层上贴焊球,完成电气接口的构建,确保芯片与外部电路的可靠连接。

7)最后通过划片工序,将重构晶圆分割成单个封装,得到最终的封装产品。此工艺操作流程相对简单,能够直接埋入不同厚度的芯片和无源器件,为多样化的芯片集成提供了极大便利。

2.芯片先装/面朝上工艺步骤

1)首先在晶圆的芯片焊盘上制作UBM(底部金属化层)和铜柱接触焊垫,这是保障芯片电气连接和信号传输的关键步骤。

2)对晶圆进行减薄切割处理,使其满足封装尺寸和性能要求。

3)在临时载板上涂覆黏结层,为芯片的放置做好准备。

4)将经过测试合格的芯片面朝上精心排布到载板上,确保芯片位置准确。

5)采用EMC材料,通过模压成型工艺制作重构晶圆,并进行固化操作。

6)固化后,对EMC进行削磨处理,精准露出铜柱接触焊垫,为后续的再布线和连接奠定基础。

7)在露出的铜柱接触焊垫上制作再布线层,并贴焊球,实现芯片的电气连接。

8)去除载板和黏结层,然后进行划片操作,将重构晶圆分割成单个封装。该工艺的优势在于封装厚度更薄,有利于芯片散热,并且在载板的支持下能有效改善工艺过程中的翘曲问题。但也存在局限性,如无法埋入不同高度的器件,同时芯片上预制铜柱、涂覆PI膜等操作会导致生产周期延长、成本显著增加。此外,在露铜工艺中易出现铜污迹和表面沾污问题,不过可通过在铜柱焊垫完成后在晶圆表面涂覆一层PI的方法有效解决 。

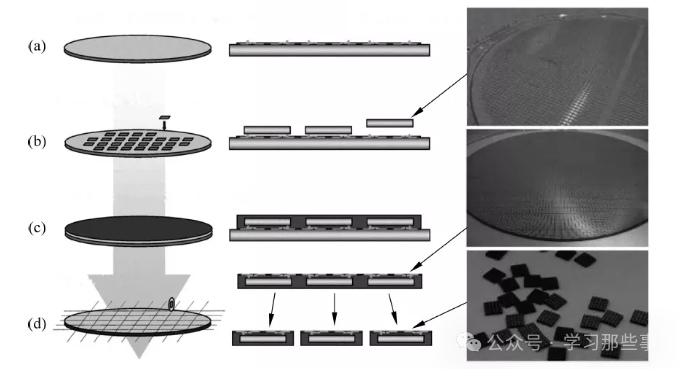

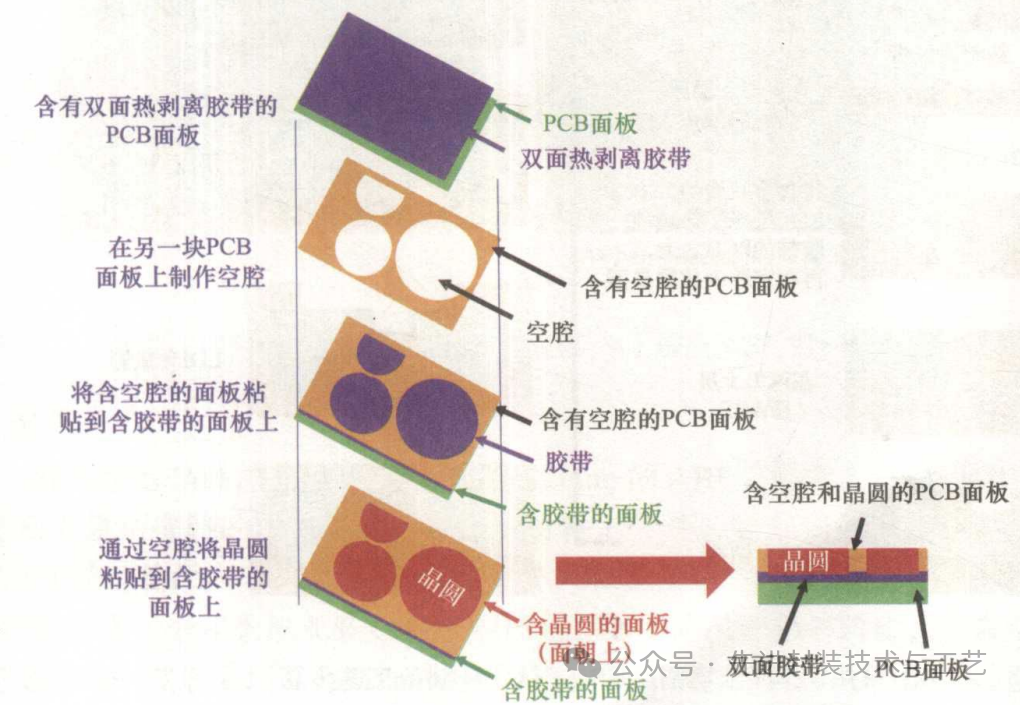

芯片后装/先RDL工艺步骤

1)先将光敏PI沉积在硅承载片上,并设置格栅阵列状的开口,这些开口用于实现芯片与外部的电气连接。

2)使用半加成法制作Cu RDL(铜再布线层),形成多层RDL结构,同时在顶部铜线的相关位置形成带有Sn - Ag焊料帽的铜柱凸点。

3)以高精度(芯片到晶圆3μm)将芯片倒装键合到晶圆上,此时芯片的焊盘表面经过化学镀Ni/Pd/Au处理,以确保良好的电气连接性能。

4)完成键合后,进行晶圆模压操作,使芯片与周边结构牢固结合。

5)模压完成后,移除硅承载片。

6)最后通过切割工序,将晶圆分离成单个封装。此工艺在RDL精度方面表现优异,产出率更高,尤其适用于集成不同高度的器件。在生产过程中,由于硅承载片的支撑作用,能有效改善晶圆翘曲问题,为实现高质量的芯片封装提供了有力保障。

4.不同工艺组合与特点

根据重布线工序顺序和芯片放置方式的不同,FOWLP主要衍生出面朝上的先芯片处理、面朝下的先芯片处理和面朝下的后芯片处理三种组合工艺。面朝上的先芯片处理工艺需利用CMP将塑封层减薄,这一过程成本高昂,因此在实际应用中较少被封装厂采用。面朝下的先芯片处理工艺在移除载板并添加RDL制程时,容易引发翘曲问题,需要在工艺操作中提前采取防范措施。尽管存在这一挑战,但该工艺凭借其自身优势,在封装厂中得到了广泛应用,例如苹果的A10处理器。面朝下的后芯片处理工艺先进行RDL工艺,这种方式能够有效降低芯片封装制程产生的不合格率,目前在封装厂中也应用较多 。

FOWLP的优势与挑战

1.封装与集成优势

FOWLP采用独特的布线方式,能够巧妙地埋入多种不同芯片。在形成重构晶圆后的布线过程中,一次性实现多个芯片的互连,这一创新极大地减小了封装尺寸,有效降低了成本。与传统的倒装芯片球栅阵列(FC - BGA)封装相比,FOWLP在凸点制备完成后,无需使用封装基板便可直接焊接在印刷电路板上,简化了封装流程,提高了生产效率 。

2.电气与热性能优势

在无源器件的处理上,FOWLP技术展现出卓越的性能。在塑封成型时,其衬底损耗更低,电气性能更优,外形尺寸更小。这一系列优势带来了能耗更低、发热更少的显著效果,使得在相同功率下,芯片的工作温度更低;或者在相同温度时,电路运行速度更快。其厚铜线路的寄生电阻更小,衬底与塑封料间的电容更小,衬底损耗更少,电感与塑封料越接近损耗因子越小,Q值越高。此外,“消失的”基板层减小了整体尺寸,缩短了热流通路径,降低了热阻,为芯片的高效稳定运行创造了良好条件 。

二、FOWLP面临的挑战

1.热相关问题

FOWLP焊接点的热膨胀情况与BGA极为相似,在芯片和PCB之间不可避免地存在热膨胀系数不匹配的问题。当经过220 - 260℃回流焊时,聚合物内吸收的水分会迅速汽化,产生高内部蒸汽压。若胶体组成不良,就极易出现胶体剥落现象,严重影响封装的可靠性和性能 。

2.工艺精度问题

在重新建构排布过程中,维持芯片从抓取到放置于载具上的位置不发生偏移至关重要,在铸模作业时同样不能出现偏移。由于介电层开口、导线重新分布层与焊锡开口制作皆依赖光学光刻技术,且掩模对准晶圆及曝光是一次性完成的,这对芯片位置的精确度提出了极高的要求。哪怕是微小的偏移,都可能导致后续工艺的偏差,影响封装的质量和性能 。

3.晶圆与芯片问题

芯片放置于临时载板及重新排布过程中,会不可避免地产生翘曲问题。重新建构晶圆由塑胶、硅及金属材料组成,硅与胶体比例在三个方向上存在差异,铸模时的热胀冷缩会显著影响晶圆的翘曲行为。同时,芯片放置在载板晶圆上和包覆成型过程中,会出现轻微移动,这一现象对工艺产生不利影响。此外,采用扇出式封装仍存在因分割而引起的损坏问题,尽管相比其他封装方式,其损坏程度相对较轻,但仍不容忽视 。

-

封装技术

+关注

关注

12文章

605浏览量

69367 -

工艺流程

+关注

关注

7文章

118浏览量

16874 -

晶圆级封装

+关注

关注

5文章

47浏览量

11823

原文标题:扇出型晶圆级封装(FOWLP)技术

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

扇出型晶圆级封装技术的工艺流程

扇出型晶圆级封装技术的工艺流程

评论