混合键合(Hybrid Bonding)工艺介绍

简介:

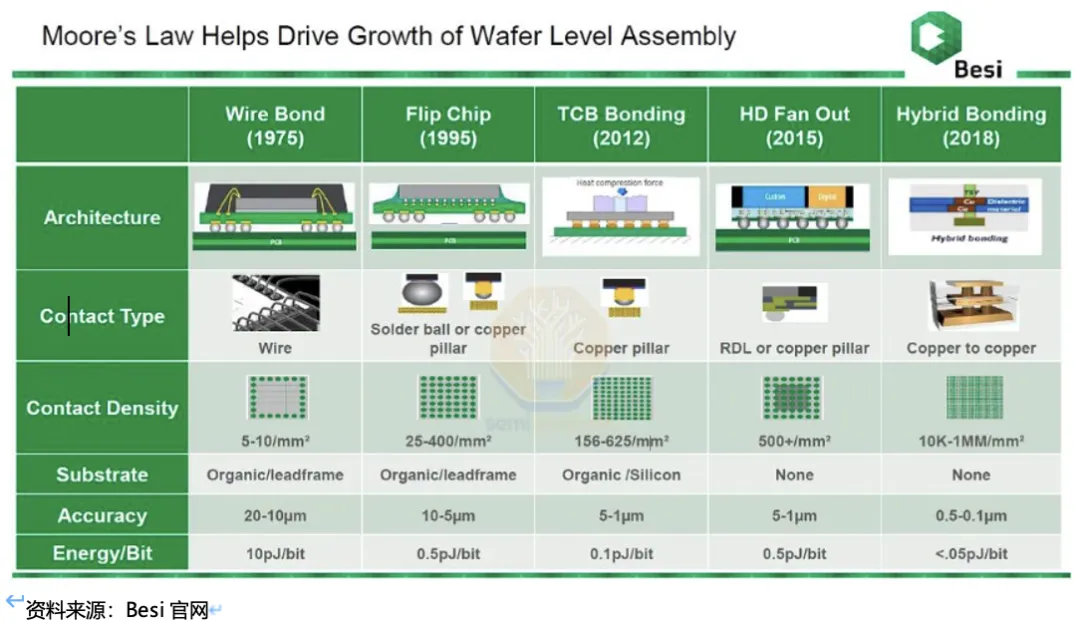

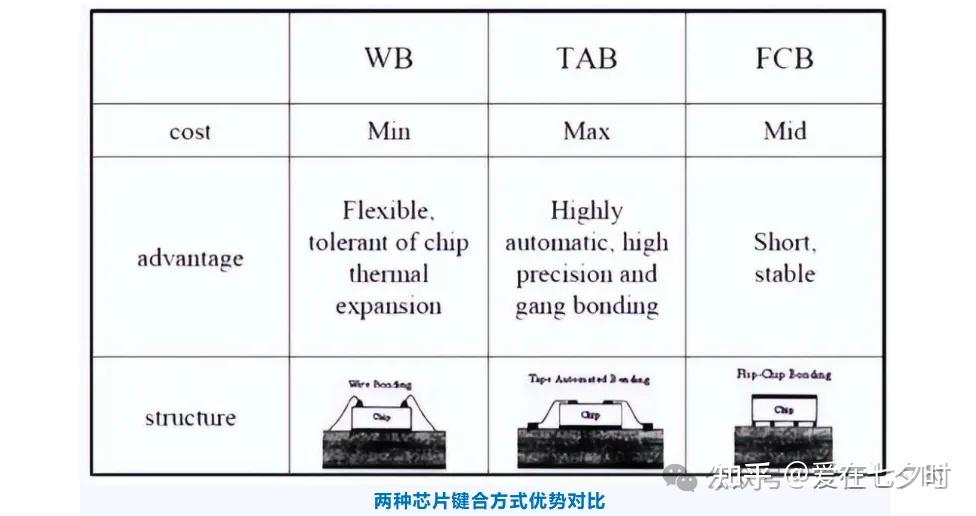

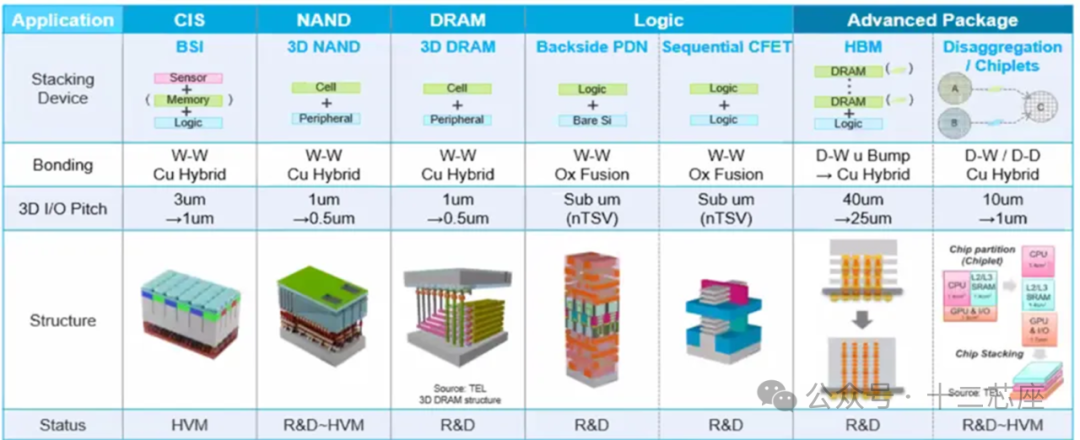

所谓混合键合(hybrid bonding),指的是将两片以上不相同的Wafer或Die通过金属互连的混合键合工艺,来实现三维集成,在Hybrid Bonding前,2D,2.5D及3D封装都是采用焊锡球凸点(solder bump)或微凸点(Micro bump)来实现芯片与基板,芯片与中介层(Interposer),芯片与芯片间的电连接。Solder bump/micro bump在制备工艺中都有植球的步骤,所植的球就是焊锡球(Solder bump),所以在Hybrid Bonding之前芯片间的连接都是靠焊锡球进行连接。

当然Solder bump是植在铜柱(Copper bump)上的。当copper bump pitch小于10~20um时,焊锡球solder bump就变成了工艺难点及缺陷的主要来源。这时候就需要一种新的工艺来解决bump间距小于10微米芯片间键合的问题。

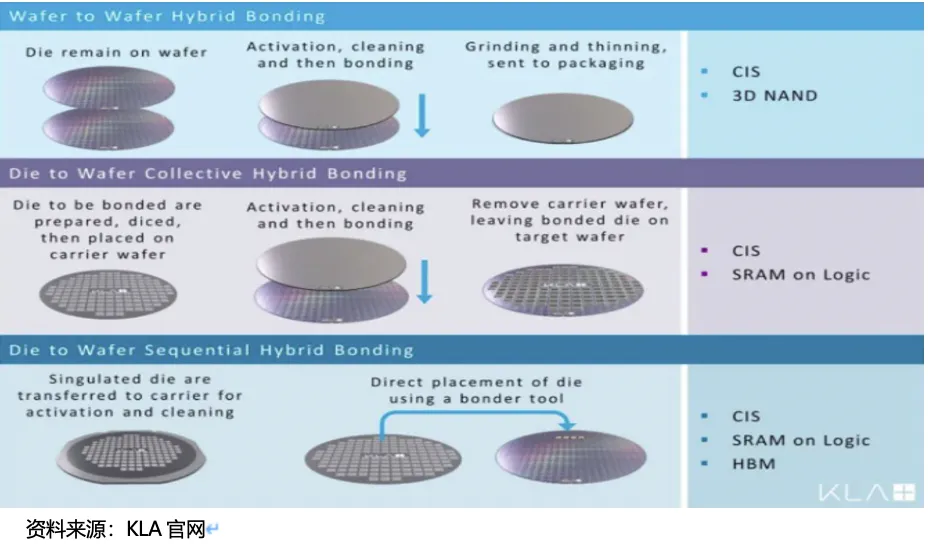

混合键合两种常见的类型:

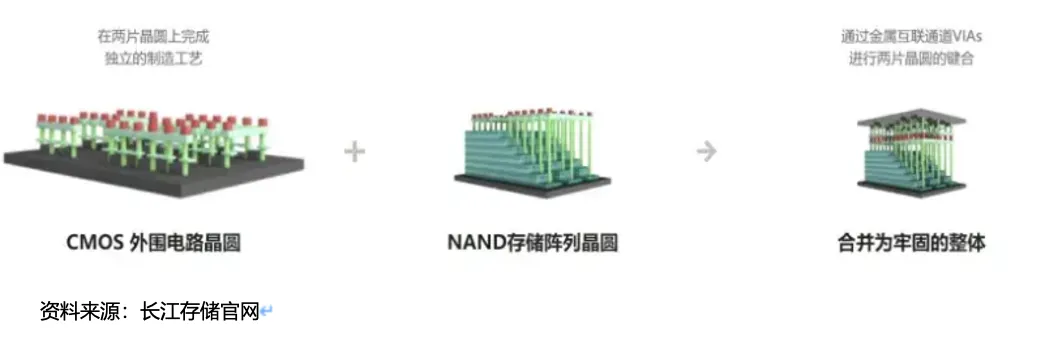

1.Wafer to Wafer (W2W)晶圆对晶圆:适合高良率的芯片,如CMOS、3D NAND。2.Die to Wafer (D2W) 芯片对晶圆:适合不同种类型芯片集成,如异构集成。

W2W可以提供更高的对准精度、吞吐量和键合良率。但一个主要限制是无法选择已知的合格芯片(KGD)。这会导致将有缺陷的芯片粘合到好的芯片上,从而导致优质芯片的浪费。W2W 的另一个缺点是两片晶圆上芯片的尺寸必须一致,因此这限制了异构集成选项的灵活性。所以,W2W适用于良率高的晶圆,通常是设计尺寸较小芯片,如CMOS 图像传感器、3D NAND。

D2W允许将不同尺寸、工艺节点的芯片(如逻辑芯片与存储芯片)选择性集成到同一晶圆上,从而支持异构集成和定制化设计,避免了W2W因整片晶圆键合导致的良率损失问题(例如一片晶圆存在缺陷时,仅影响单个芯片而非整片)。此外,D2W可通过分步测试筛选合格芯片(KGD)再进行键合,降低了整体成本。

这种特性使其在先进封装(如3D堆叠)中更具适应性,尤其适用于需要整合多来源芯片的高性能计算场景。然而,D2W混合键合的技术实现难度更高,主要体现在亚微米级对准精度和界面共面性控制两大挑战。

工艺流程:

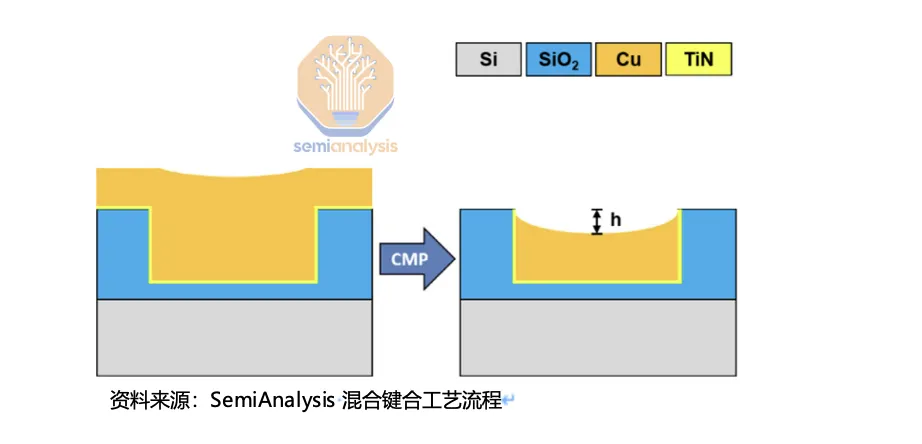

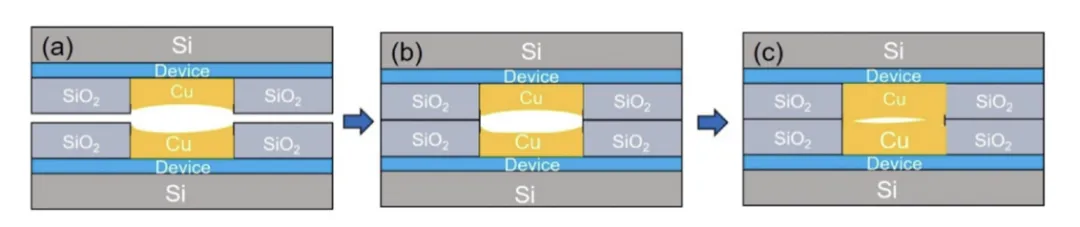

混合键合结合了两种不同的键合技术:介电键合和金属互连。一般采用介电材料(通常是SiO₂)与嵌入式铜(Cu)焊盘结合,通过形成电介质键(dielectric bond)和金属键(metal bond)实现两个晶圆(wafers)或裸片(dies)之间建立永久电连接,而无需焊料凸块。这种无凸块方法通过减少信号损耗和改善热管理来提高电气性能 。

一.表面准备:晶圆需经过化学机械抛光/平坦化(CMP)和表面活化及清洗处理。混合键合层的表面光滑度非常关键。Hybrid Bonding界面处对任何类型的凹凸都可能会产生空洞和无效的键合,通常需要确保表面粗糙度(Ra)低于0.5nm。,铜焊盘为1nm。为了达到这种平滑度,需要进行化学机械平坦化(CMP)。

CMP完成后,还需要进行表面活化(Activation)等离子体处理:对SiO₂表面进行Ar、N₂或O₂等离子体处理,增加表面羟基(-OH)密度,增强亲水性。铜表面可能需还原性等离子体(如H₂)去除氧化层。

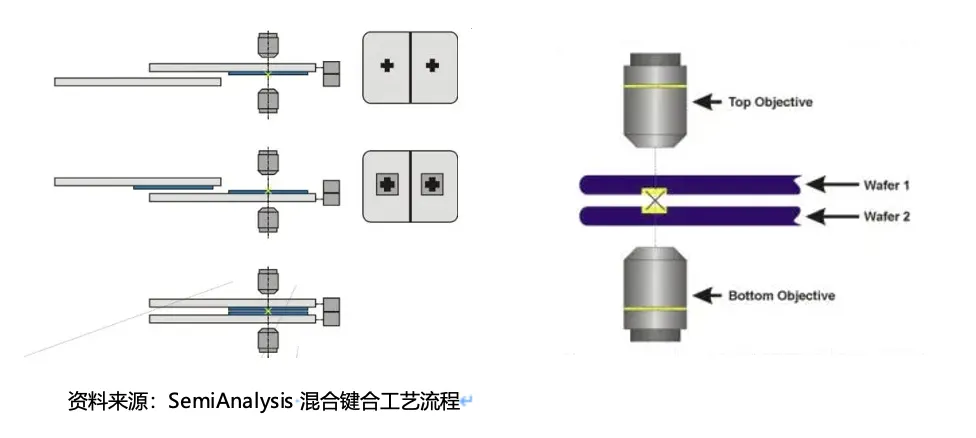

二.对位:晶圆或芯片的对准需要在洁净室(Class 1-10)中进行,避免颗粒污染。经过精确对准,以确保金属焊盘正确对应,从而实现有效的电气互连。

需要注意的是:由于键合过程涉及两个非常光滑且平坦的表面齐平地键合在一起,因此键合界面对任何颗粒的存在都非常敏感;高度仅为1 微米的颗粒会导致直径为10 毫米的粘合空隙,从而导致键合缺陷。

三.预键合:经过对位之后晶圆或芯片间仅形成初始电介质键,此时只是通过范德华力结合在一起,还需要在室温或略高的温度、在N₂或真空环境下,配合一定的压力,通过原子扩散和机械互锁形成牢固的键合。

南京屹立芯创拥有多项创新发明专利技术,设备可以通过在真空和升温环境中对晶圆与芯片施加稳定、均匀的压力,让芯片与晶圆之间更平坦化,实现晶圆或芯片间稳定键合。

南京屹立芯创有着丰富的经验和解决方式,致力于提高客户产品的质量及可靠度。公司的产品广泛应用于半导体封装,电子组装,5G通讯,新能源应用,车用零件,航天模块,生化检测等各大科技领域。

四.键合后处理:初始键合后,还需要通过额外的热处理来进一步促进铜向介电层扩散,确保稳固的互连,以此来增强键合强度和电气性能。

混合键合应用:

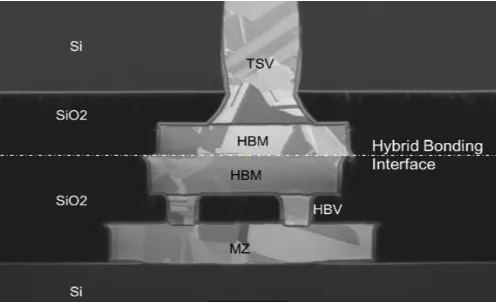

混合键合用于芯片的垂直(或3D)堆叠。混合键合的显著特点是无凹凸。它从基于焊接的凸块技术转向直接的铜对铜连接。这意味着顶模和底模彼此齐平。两个芯片都没有凸块,只有可以缩放到超细间距的铜焊盘。没有焊料,因此避免了与焊料相关的问题。同时混合键合在电学性能方面也有独特的优势,Hybrid Bonding信号丢失率几乎可以忽略不计,这在高吞吐量,高性能计算领域优势明显。

目前常见的应用场景:

1.3D芯片堆叠:混合键合被广泛应用于处理器和内存堆栈中,例如AMD的3D V-Cache技术和HBM高带宽内存的多层堆叠。通过混合键合,可以将CPU与额外缓存芯片紧密连接在一起,显著提升系统性能;同时,在图形处理单元(GPU)和高性能计算领域,将内存芯片直接堆叠到逻辑芯片上,极大地提高了数据带宽和访问效率。

2.异构集成:混合键合技术也促进了异构系统的集成,使得各种不同工艺节点制造的芯片可以有效地结合在一起,形成一个单一的高性能封装体。例如,将射频芯片、传感器、处理器等多种类型的芯片整合在同一封装内,优化了物联网设备、智能手机和其他智能硬件的空间利用和整体性能。

3.图像传感器:混合键合在CMOS图像传感器(CIS)领域也有重要应用,如背照式(BSI)传感器和堆叠式传感器等,其中底层的像素阵列通过混合键合技术与顶层的电路层相连,降低了光路损失并实现了更小型化的相机模组设计。

总结:

混合键合作为先进封装技术的核心组成部分,正逐渐成为推动半导体行业向三维集成发展的重要驱动力。从市场规模来看,当前火爆的AI算力需求,推动混合键合技术市场正以显著增速扩张,其在高密度集成、低功耗传输上的优势使其成为3D封装的关键技术。

文章中图片引用请参考出处标注

审核编辑 黄宇

-

半导体

+关注

关注

339文章

31238浏览量

266576 -

先进封装

+关注

关注

2文章

562浏览量

1062

发布评论请先 登录

半导体芯片制造技术——“芯片键合”工艺技术的详解;

热压键合工艺的技术原理和流程详解

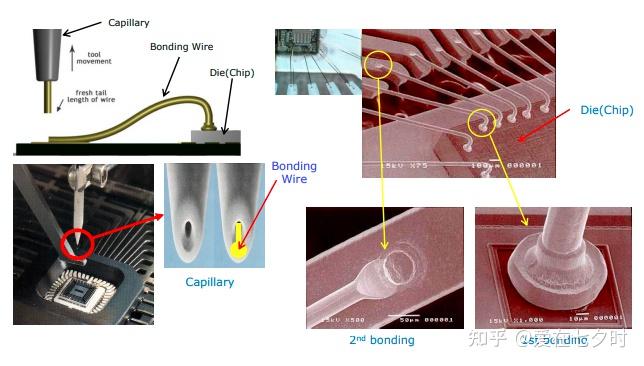

半导体封装“焊线键合(Wire Bonding)”线弧相关培训的详解;

氧浓度监控在热压键合(TCB)工艺过程中的重要性

半导体后道制程“芯片键合(Die Bonding)”工艺技术的详解;

混合键合(Hybrid Bonding)工艺介绍

混合键合(Hybrid Bonding)工艺介绍

评论