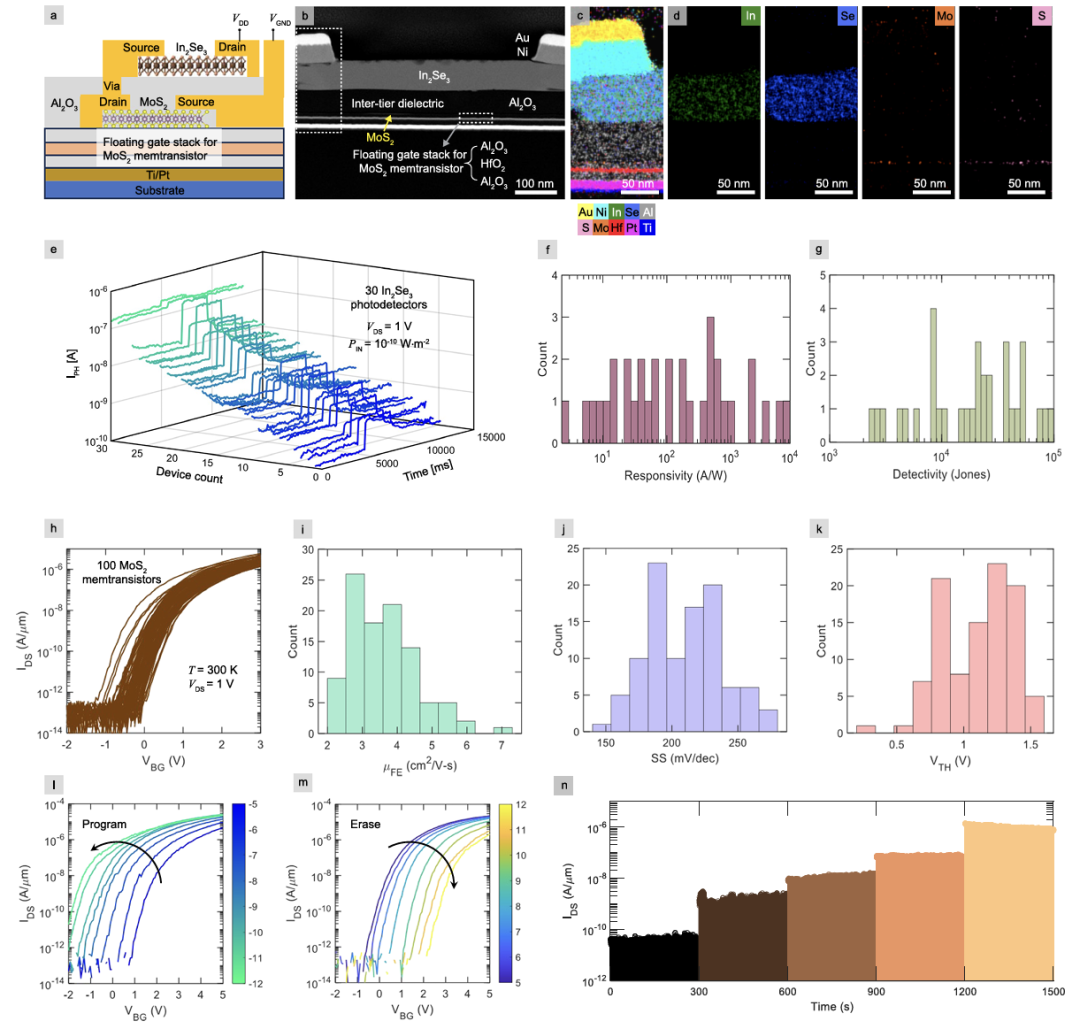

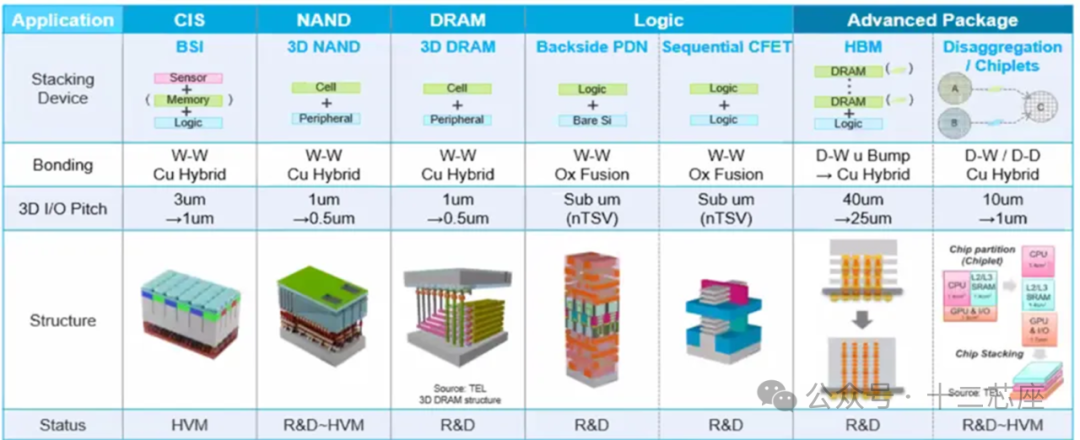

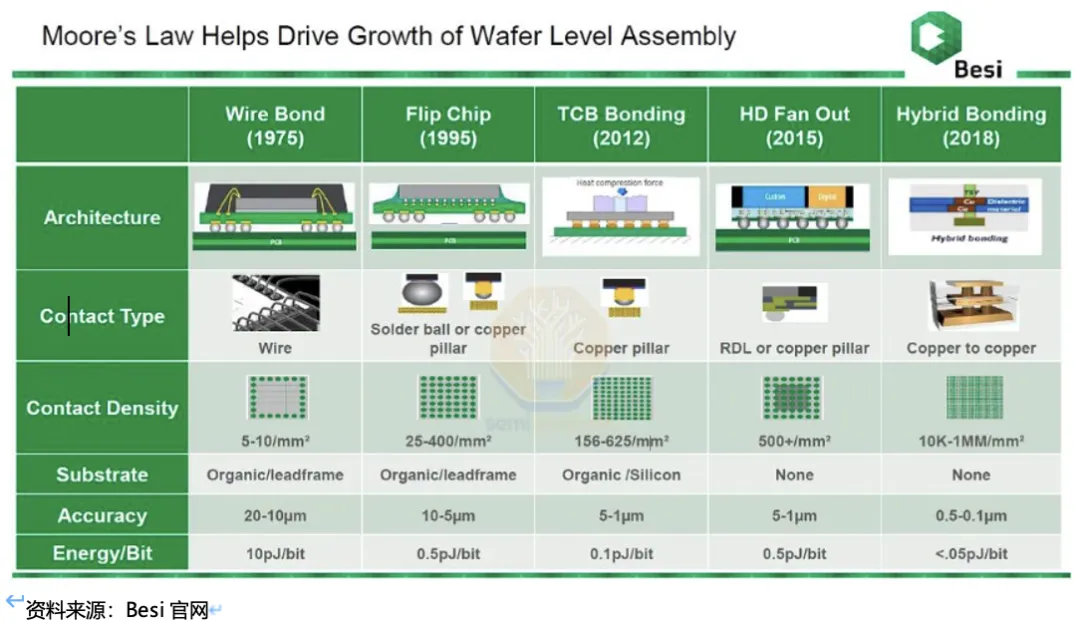

当传统制程微缩逼近物理极限,芯片巨头们正在另一条赛道加速冲刺——垂直方向。Counterpoint Research最新报告指出,混合键合(Hybrid Bonding) 技术已成为实现“单颗芯片一万亿晶体管”目标的关键跳板。当前先进封装虽提高了I/O密度,但愈发复杂的异构设计与Chiplet架构对I/O数量、延迟提出了更高要求,以满足AI、5G和高性能计算等应用。混合键合互连技术正成为关键突破口,它可显著降低能耗、扩大带宽、优化热管理,从而助力摩尔定律继续前行。

Counterpoint Research指出,随着半导体行业迅速转向3D集成,混合键合技术将成为推动下一代高性能计算(HPC)和AI加速器先进封装解决方案的主要驱动力。当前,混合键合技术已在3D Co-Packaged Optics、高带宽内存(HBM)和3D DRAM等领域展现出巨大潜力,通过提供超密集、低损耗的互连,显著提升性能、效率和微型化水平。

数据显示,目前市场上对混合键合技术的需求正急剧增长,特别是在AI、5G和HPC应用中,混合键合技术因其显著的节能、带宽增强和热管理优势,成为满足高I/O密度和低延迟需求的关键解决方案。预计未来几年,混合键合技术的市场规模将大幅扩张,成为支撑摩尔定律持续发展的核心力量。

Counterpoint Research此前预测,混合键合技术将在2025年前后实现广泛应用,推动半导体行业进入一个新的增长阶段。其他机构如国际半导体技术路线图(ITRS)也预测,混合键合技术将成为未来十年内半导体封装领域的主流技术之一,助力实现更高性能和更低功耗的芯片设计。

科技防护,精准选型 晶扬电子提供专业ESD防护方案

晶扬电子 | 电路与系统保护专家

深圳市晶扬电子有 限公司成立于2006年,是国家重点专精特新“小巨人”科技企业、国家高新技术企业、深圳知名品牌、广东省制造业单项冠军产品、深圳市制造业单项冠军企业,知识产权示范企业,建成广东省ESD静电保护芯片工程技术研究中心,荣获中国发明创业奖金奖等。是多年专业从事IC设计、生产、销售及系统集成的集成电路设计公司,在成都、武汉和加拿大设立有研发中心,拥有超百项知识产权和专利,业内著名的“电路与系统保护专家”。为各类电子产品提供全方位、全覆盖的静电保护、高边开关等保护方案。

主营产品:ESD、TVS、MOS管、DC-DC,LDO系列、工业&车规传感器、高边开关(HSD)芯片、电流传感器、汽车开关输入芯片等。

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54414浏览量

469200 -

封装

+关注

关注

128文章

9329浏览量

149039 -

晶体管

+关注

关注

78文章

10439浏览量

148584

发布评论请先 登录

深入解析DLP300S:开启低成本DLP 3D打印新时代

晶体管的基本结构和发展历程

白光扫描干涉法在先进半导体封装混合键合表面测量中的应用研究

LG电子重兵布局混合键合设备研发,锁定2028年大规模量产目标

用于混合组装的微型光电晶体管光耦合器 skyworksinc

3D集成赛道加速!混合键合技术开启晶体管万亿时代

3D集成赛道加速!混合键合技术开启晶体管万亿时代

评论