文章来源:学习那些事

原文作者:小陈婆婆

本文详细介绍了晶圆级扇出系统及其集成技术。

晶圆级扇出封装(FO-WLP)通过环氧树脂模塑料(EMC)扩展芯片有效面积,突破了扇入型封装的I/O密度限制,但其技术复杂度呈指数级增长,本文分述如下:

两代技术对比与系统集成

芯片先置与芯片后置工艺

塑封工艺与表面平坦化技术

再布线层(RDL)技术

垂直互连技术

两代技术对比与系统集成

早期扇出封装

早期扇出封装以嵌入式晶圆级BGA(eWLB)为代表,通过单层RDL实现BGA球扩展,但仅适用于低密度单芯片集成。

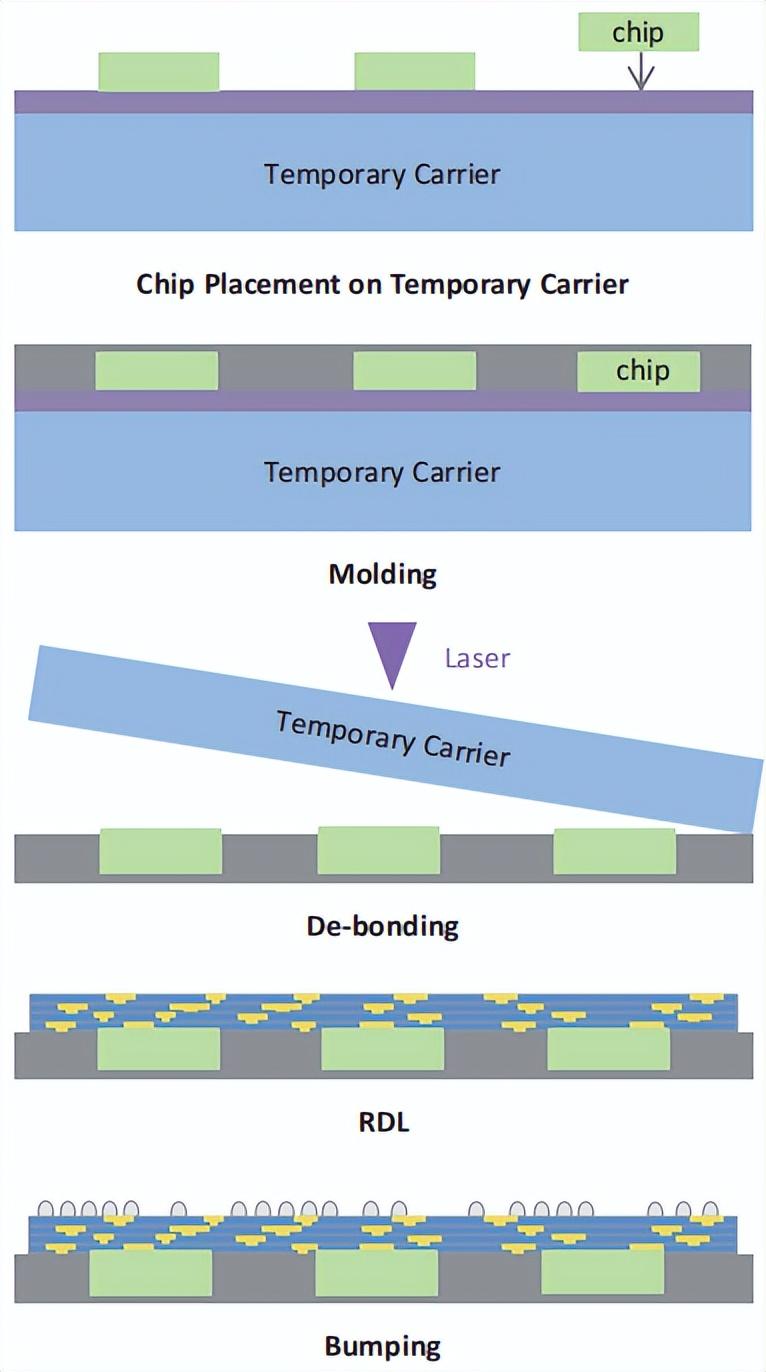

其工艺流程为:

切割硅晶圆并筛选KGD;

将芯片面朝下贴装于临时载板,进行EMC塑封;

通过减薄工艺暴露芯片焊盘;

构建单层RDL与UBM;

植球后切割为单颗器件。

该方案虽成本优于倒装芯片封装,但受限于单层布线与尺寸约束(通常<15mm×15mm)。

第二代扇出平台

第二代扇出平台通过三大革新实现系统级集成:

多层级RDL:采用双层及以上铜布线,支持线宽/间距(L/S)达1μm/1μm的高密度互连;

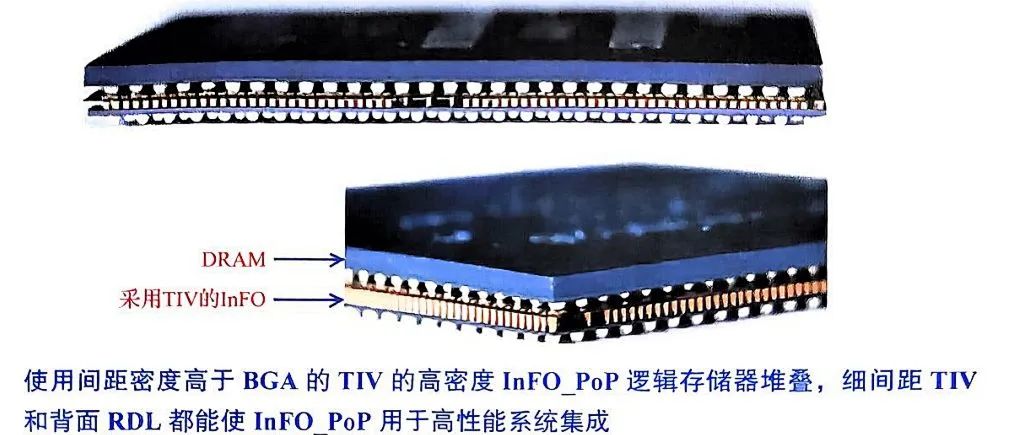

异构集成:集成逻辑芯片、HBM内存及无源器件,形成2.5D/3D堆叠架构;

热管理优化:通过EMC配方调整与金属热界面材料(TIM)集成,将热阻降低40%。

InFO技术使移动计算平台实现30%以上的功耗下降与20%的能效提升,验证了其商业可行性。

芯片先置与芯片后置工艺

当前扇出封装存在两条技术路线:

芯片先置(Die-First)

工艺流程:KGD贴装→塑封→RDL布线→植球

优势:封装厚度可压缩至0.3mm以下,RDL直接沉积于芯片焊盘,消除微凸点结构;

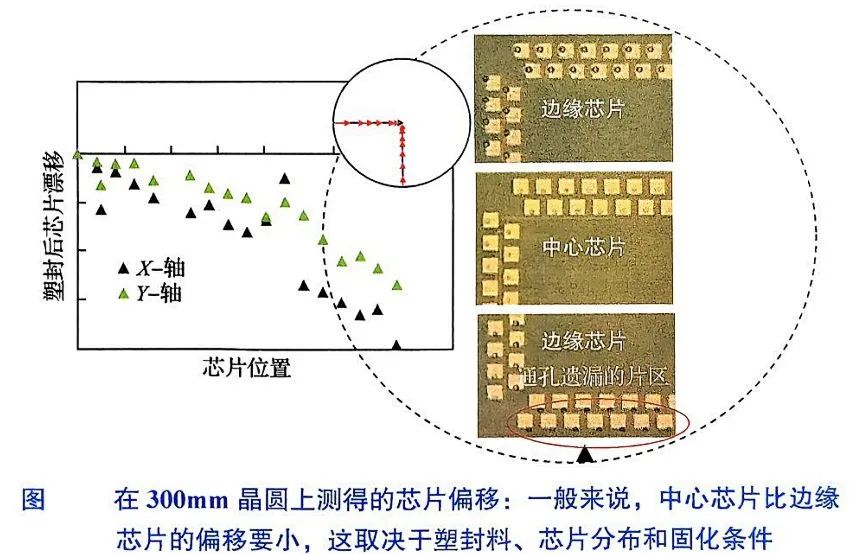

挑战:塑封料固化收缩引发芯片偏移(典型偏差50-100μm),需通过预补偿算法与光刻对准修正。

案例:eWLB采用面朝下贴装,通过载板表面粗糙度控制平面度;InFO则采用面朝上方案,依赖化学机械抛光(CMP)实现EMC全局平坦化。

芯片后置(RDL-First)

工艺流程:RDL布线→倒装芯片键合→塑封→植球

优势:RDL层预先图案化,芯片放置精度达±5μm;

局限:需引入微凸点(典型高度50μm),导致封装厚度增加,且受限于焊盘间距(>40μm)。

案例:SLIM技术采用铜柱凸点实现100μm节距互连,但成本较芯片先置方案高30%。

良率敏感性分析显示,芯片先置方案在12英寸晶圆上可实现98%的嵌入良率,而芯片后置方案因涉及多次热循环,良率下降2%-3%。

塑封工艺与表面平坦化技术

塑封环节需平衡流动性、填料分布与翘曲控制

注射传递模塑:通过优化流道设计(如螺旋形浇口)减少空洞率,但受限于芯片间距(<2mm时易产生流痕)。

压缩模塑:采用低黏度环氧树脂(黏度<50Pa·s),配合等温固化工艺,将翘曲度控制在50μm以内;

面板级塑封:针对600mm×600mm矩形面板,开发分段式压力控制系统,解决大尺寸成型中的填充均匀性问题。

平面化技术直接影响RDL精度

CMP工艺:通过陶瓷磨粒与碱性抛光液,实现EMC表面粗糙度<10nm,满足2μm以下L/S需求;

激光剥离:采用紫外纳秒激光(波长355nm)去除载板,避免机械应力引发的芯片隐裂。

材料选型需权衡热机械性能与工艺窗口:

低CTE配方:通过添加二氧化硅填料(粒径5-15μm),将EMC热膨胀系数降至8ppm/K以下;

低模量体系:采用苯并噁嗪树脂基材,杨氏模量<8GPa,缓解热应力集中。

技术前沿与产业发展趋势

当前扇出封装正朝三个方向演进:

超薄化:通过EMC减薄与临时键合膜(TBF)技术,实现0.1mm级封装厚度;

高频应用:集成低损耗介质材料(Dk<3.0),支持5G毫米波芯片封装;

异质整合:结合玻璃穿孔(TGV)与有机基板,构建多材质混合封装平台。

随着系统级封装(SiP)需求激增,扇出工艺与三维集成技术的融合将成为下一阶段创新焦点。

再布线层(RDL)技术

再布线层(RDL)作为扇出封装的核心组件,其线宽/间距(L/S)精度直接决定封装密度、信号完整性及成本结构。当前主流封装厂形成两大技术路线:

晶圆级RDL工艺

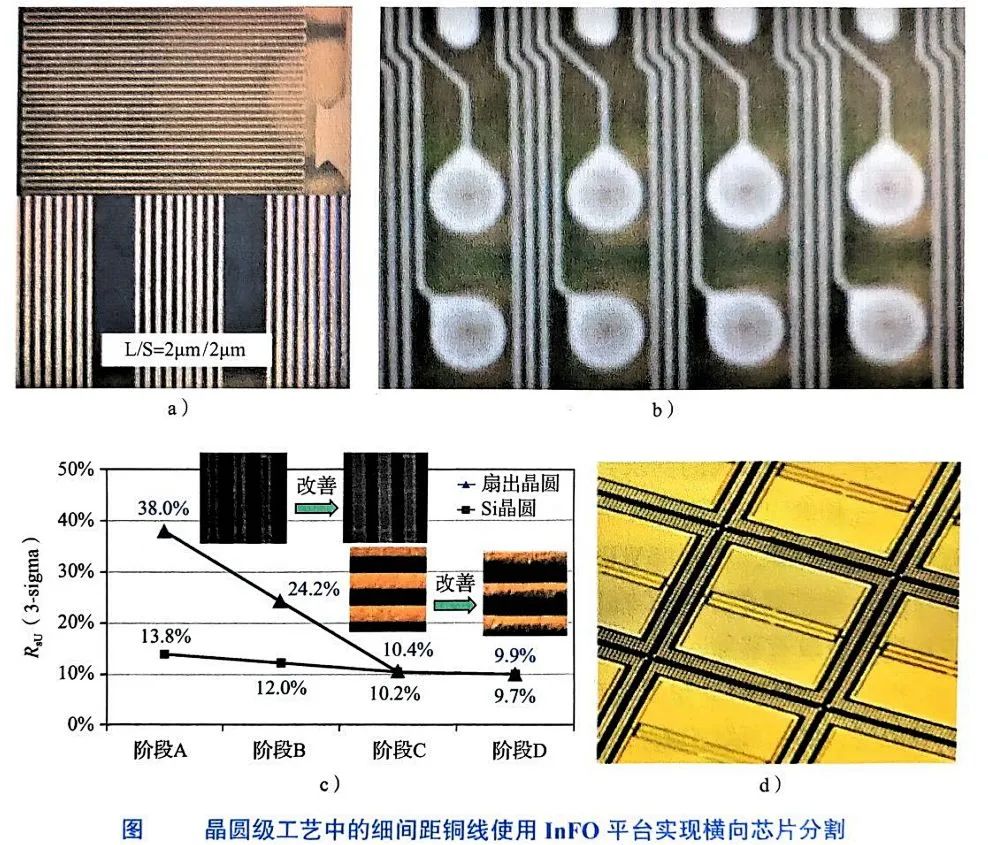

设备协同:采用步进式光刻机(Stepper)与干膜抗蚀剂(Dry Film Photoresist, DFPR),实现L/S=1μm/1μm的超细线宽,匹配硅基后道工艺(BEOL)标准。

材料创新:通过低介电常数(Dk<3.0)聚合物与气隙隔离技术,将寄生电容降低30%,适用于高频(>100GHz)应用;

多层堆叠:采用半加成法(SAP)构建8层以上RDL,单层对准精度达±0.5μm,满足HBM内存与逻辑芯片的2.5D集成需求。

面板级RDL工艺

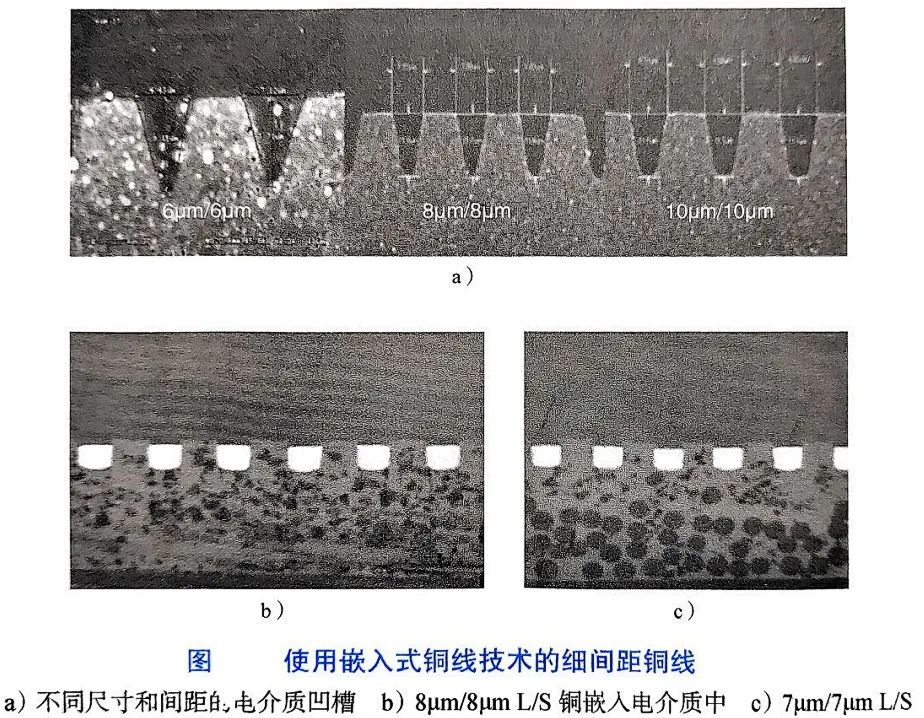

嵌入式布线:通过激光诱导深度蚀刻(Laser Ablation)在EMC中形成沟槽,再经电化学镀(ECP)填充铜,实现L/S=5μm/5μm的埋入式布线,规避传统SAP工艺的侧蚀问题。

成本优化:使用化学镀铜种子层(厚度<1μm),较晶圆级工艺材料成本降低40%,但受限于设备场域,面板尺寸超过600mm×600mm时线宽均匀性下降8%。

垂直互连技术

扇出封装通过三类垂直互连通孔(TIV/TPV/TMV),突破二维集成边界,实现三维堆叠。

穿互连通孔(TIV)

芯片先置方案:采用纳秒紫外激光(波长355nm)在EMC中钻孔,孔径精度达±2μm,再通过无电镀镍/钯/金(ENEPIG)填充,形成垂直电阻<5mΩ的导电通道。

芯片后置方案:在RDL层间通过深反应离子蚀刻(DRIE)构建高深宽比通孔(AR>10:1),匹配硅转接板级(TSV)密度,支持HBM堆叠层数提升至16层。

穿封装通孔(TPV)

集成毫米波天线时,采用低温共烧陶瓷(LTCC)填充通孔,将插入损耗控制在一定范围内,较传统微带线方案提升20%辐射效率。

穿模具通孔(TMV)

针对电源完整性需求,在EMC中嵌入铜柱通孔(直径100μm),通过选择性电镀将直流电阻降低至0.2mΩ,满足AI加速器芯片1000A级电流传输需求。

技术融合及发展趋势

背面RDL扩展:通过激光释放临时载板(Laser Debonding)暴露EMC背面,再构建双层RDL,使BGA阵列密度提升4倍,突破传统封装外围引脚限制;

异质材料整合:结合玻璃转接板(Glass Interposer)与有机基板,利用玻璃的高平整度(TTV<1μm)实现1μm/1μm超细RDL,同时通过有机材料的低模量(<10GPa)缓解热应力。

随着系统级封装需求升级,RDL与垂直互连技术正从单维优化转向协同创新,推动扇出封装向类硅转接板性能演进。

-

芯片

+关注

关注

463文章

54389浏览量

469047 -

晶圆

+关注

关注

53文章

5446浏览量

132715 -

封装

+关注

关注

128文章

9321浏览量

149028 -

BGA

+关注

关注

5文章

586浏览量

51936

原文标题:晶圆级扇出系统及其集成技术

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

什么是晶圆级扇出封装技术

什么是晶圆级扇出封装技术

评论