文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了3D封装中的硅通孔、IC键合和集成技术。

微电子技术的演进始终围绕微型化、高效性、集成度与低成本四大核心驱动力展开,封装技术亦随之从传统TSOP、CSP、WLP逐步迈向系统级集成的PoP、SiP及3D IC方向,最终目标是在最小面积内实现系统功能的最大化。

3D封装技术历经MCM、堆叠封装到芯片级堆叠的迭代,而3D IC作为终极形态,依托TSV垂直互连、晶圆键合与超薄晶圆减薄三大核心技术,正突破二维缩放瓶颈,满足移动电子、可穿戴设备对低功耗、高计算能力的严苛需求。

本文分述如下:

硅通孔(TSV)

3D IC键合与集成技术

晶圆级3D集成

硅通孔(TSV)

硅通孔(TSV)作为3D芯片封装的核心理异构集成技术,通过垂直互连路径最小化信号传输延迟,成为CPU-内存、闪存-控制器等高速数据交互场景的关键支撑,其技术演进深度融合了移动电子小型化需求与系统级封装(SiP)趋势。

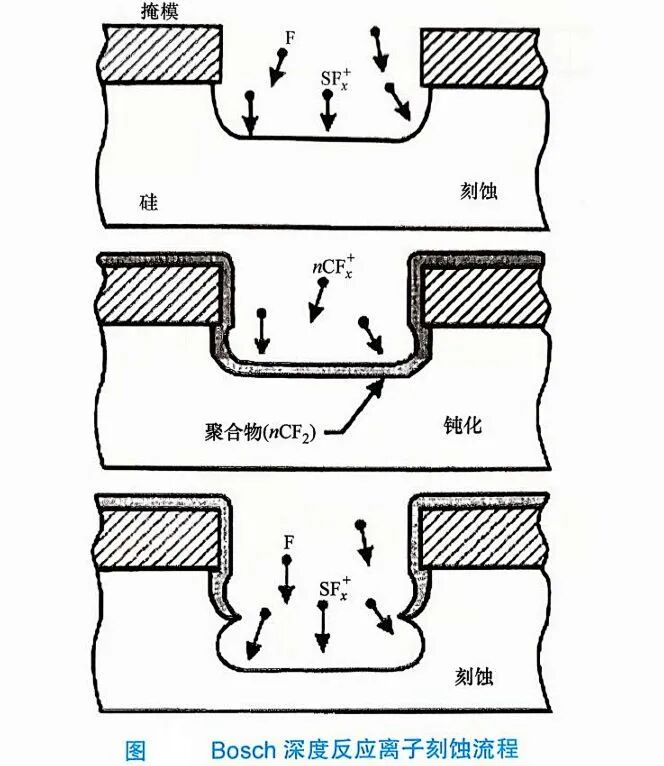

TSV形成工艺涵盖激光钻孔、Bosch深度反应离子刻蚀(DRIE)及低温DRIE三大主流路径:激光钻孔依托聚焦激光束熔化/汽化硅材料实现通孔成型,虽工艺成熟但受限于≥25μm的孔径下限与锥形侧壁特性,多用于低引脚数场景。Bosch工艺通过刻蚀-钝化循环实现高深宽比垂直刻蚀,依托感应耦合等离子体(ICP)平衡氟自由基与聚四氟乙烯类钝化层沉积,在0.5mm硅片刻蚀中需百次级循环,侧壁呈现100-500nm振幅波纹。

低温DRIE则通过-110℃低温环境抑制各向同性刻蚀,结合氧化物/氟化物阻挡层形成原子级平滑侧壁,适用于光学器件等高精度需求场景。

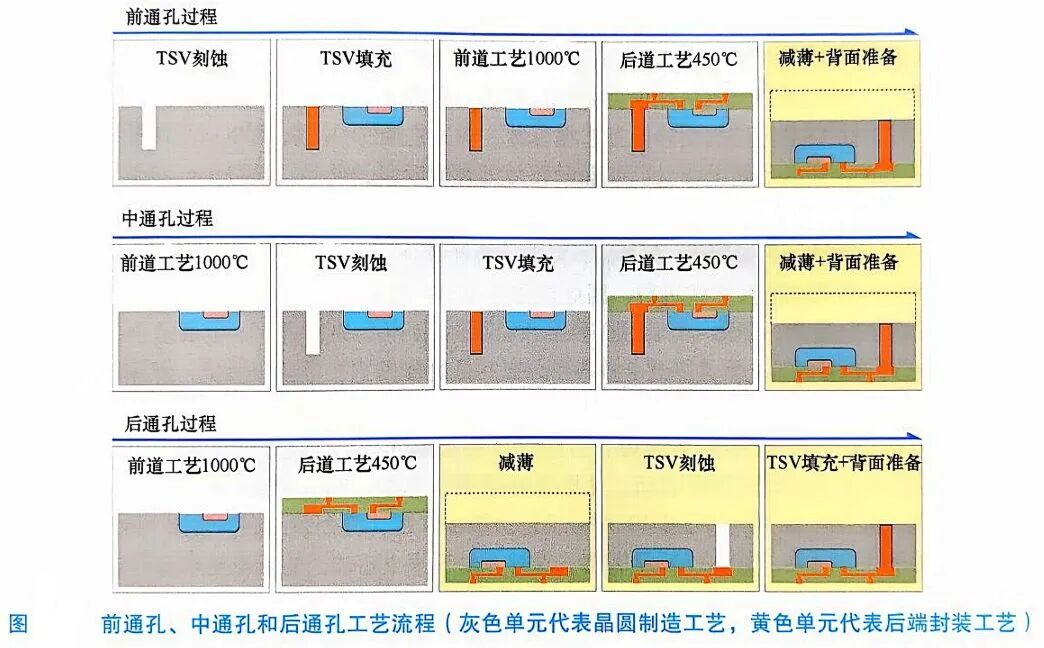

TSV分类依据制造流程分为先通孔(CMOS前)、中通孔(CMOS后互连前)及后通孔(晶圆工艺后),先通孔采用多晶硅填充以耐受高温CMOS工艺,中通孔优选铜材料以利用其低电阻特性,后通孔则通过激光钻孔与电镀铜实现低成本大尺寸通孔,适配传感器、闪存等低I/O密度场景。

填充材料方面,铜凭借优越导电性成为主流,但需通过自底向上电镀解决空隙问题;钨、钼因低热膨胀系数(CTE)特性被用于缓解硅-铜CTE失配导致的热应力,而聚合物绝缘层通过降低介电常数与热应力,在电容优化与可靠性提升方面展现潜力。

当前,TSV技术正与硅光子集成、碳基半导体等前沿领域深度融合,例如在光通信模块中实现光电协同集成,或在AI加速器中通过3D TSV堆叠提升内存带宽;新型材料如石墨烯导热层、氮化镓基TSV的研发,则进一步拓展了高频、高功率场景下的应用边界,持续推动半导体封装向更高集成度、更低损耗的智能集成方向发展。

3D IC键合与集成技术

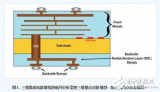

3D IC键合与集成技术作为半导体垂直整合的核心支柱,正通过多元化键合工艺与系统级优化推动三维集成向更高性能、更低功耗演进。在键合技术层面,氧化物熔融键合依托LP-CVD氧化物沉积与原子级抛光(Ra<0.4nm)实现超光滑表面,经H₂O₂/去离子水清洗后,通过Si-OH基团氢键结合与真空退火形成共价Si-O-Si键,确保晶圆级无缝连接;Cu-Sn共晶键合则利用150~280℃低温工艺实现Cu/Sn-Cu或Cu/Sn-Sn/Cu体系合金化,形成热力学稳定的Cu₃Sn合金(熔点676℃),通过Au/Ni缓冲层控制Sn消耗,适配50μm间距TSV互连;直接Cu-Cu键合凭借低温(<350℃)退火促进铜互扩散与晶粒再结晶,实现纯铜互连的优异电热性能与电迁移抗性,节距可压缩至10μm以下;聚合物胶黏剂粘接(如BCB、聚酰亚胺)则通过低温固化兼容后端工艺,提供应力缓冲与异质集成能力,但需解决固化回流导致的精密对准挑战。

3D IC集成通过垂直堆叠与TSV互连突破二维缩放瓶颈,实现封装尺寸缩减、成本优化与异质集成。英特尔2004年3D奔腾4 CPU采用面对面堆叠与背面TSV,实现15%性能提升与15%功耗降低;2007年Teraflops研究芯片通过TSV内存总线达成1TB/s总带宽与2.2W低功耗,验证了3D集成在带宽、功耗、设计自由度上的优势。然而,3D IC亦面临TSV布局占地(如45nm节点10μm×10μm TSV等效50个门)、测试复杂性(跨芯片模块无法独立测试)、热管理(堆叠热积累)、设计工具链缺失、供应链协同及标准缺乏等挑战。

当前,行业正探索混合键合、硅光子集成、碳纳米管导热层等前沿技术,如混合键合通过铜-铜与氧化物复合键合提升互连密度,硅光子集成实现光电协同计算,而碳基材料则优化高频场景下的热管理性能,持续推动3D IC向更高集成度、更低损耗的智能集成方向发展,在人工智能加速器、5G通信模块、自动驾驶芯片等领域展现广阔应用前景。

晶圆级3D集成

晶圆级3D集成在WLCSP领域展现出独特的技术路径与应用价值,尤其体现在CMOS图像传感器与MEMS封装的垂直整合中。以Tessera收购的Shellcase技术为核心,该工艺通过全晶圆级流程实现前后侧互连——硅晶圆与玻璃基板粘接后,经减薄至50~100μm,在焊盘扩展区下方形成沟槽,配合溅射铝层重布线与焊料凸点沉积,最终通过V形划片完成芯片分割。

这种设计在CMOS图像传感器中衍生出ShellOP、ShellOC、ShellBGA三种变体:ShellOP提供光学保护与边缘布线,ShellOC通过光学腔提升光接收效率,ShellBGA则适配背照式(BSI)传感器,通过薄化硅基板减少金属层散射,增强微光性能。例如,OmniVision OV14825便采用此技术,实现4416×3312像素阵列与15fps全分辨率输出,同时支持60fps 1080p视频拍摄,凸显其在移动设备中的薄型化优势。

在MEMS领域,3D晶圆级封装天然契合其三维机械结构需求。DRIE刻蚀形成的复杂结构通过CoW/WoW晶圆堆叠与焊球互连,实现ASIC与MEMS芯片的垂直整合,如ASIC倒装芯片与MEMS芯片面对面键合,形成紧凑的传感模块。这种集成不仅减少寄生效应,还通过共享基板降低整体尺寸,适配可穿戴设备等空间敏感场景。

然而,通用WLCSP的3D堆叠面临成本与集成度平衡的挑战。扇入型WLCSP受限于低I/O计数与小尺寸,3D集成需求不迫切;而扇出型WLCSP通过TMV与扇出工艺扩展封装尺寸,可借鉴BGA基板的3D概念,如基于TMV的PoP结构。当前,行业正探索无TSV的微型凸点倒装芯片互连、铜柱与晶圆成型技术的整合,为特殊应用提供定制化解决方案。例如,Shellcase MVP引入TSV实现垂直互连,减少对焊盘尺寸与间距的限制,提升晶圆利用率;而石墨烯导热层、硅-玻璃混合键合等新材料与工艺的引入,进一步优化了热管理与可靠性。

尽管成本仍是主要障碍,但3D WLCSP在图像传感、生物医疗、工业传感等细分领域的创新持续涌现。例如,集成微流控通道的3D MEMS封装实现芯片级实验室功能,或通过异质集成将传感器、处理器与存储器垂直堆叠,形成智能传感节点。这些进展不仅延续了WLCSP在小型化与高性能上的优势,更通过跨领域技术融合,推动半导体封装向更智能、更集成的方向发展。

-

集成电路

+关注

关注

5464文章

12686浏览量

375727 -

晶圆

+关注

关注

53文章

5449浏览量

132759 -

封装

+关注

关注

128文章

9330浏览量

149047

原文标题:三维集成电路与晶圆级3D集成

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路晶圆测试基础教程ppt

有偿,用matlab仿真三维电路互连线尺寸调整对延时功耗带宽影响

激光直接成型实现低成本3D集成电路

三维集成电路系统的电网分析

基于其三维集成技术平台的三片晶圆堆叠技术研发成功

三维集成电路(IC)设计中的温度控制

三维集成电路与晶圆级3D集成介绍

三维集成电路与晶圆级3D集成介绍

评论