文章来源:学习那些事

原文作者:前路漫漫

本文介绍了晶圆级封装技术的概念、优劣势和发展现状及趋势。

WLP技术概述与发展

圆片级封装(WLP),也称为晶圆级封装,是一种直接在晶圆上完成大部分或全部封装测试程序,再进行切割制成单颗组件的先进封装技术 。WLP自2000年左右问世以来,已逐渐成为半导体封装领域的主流技术,深刻改变了传统封装的流程与模式。

在传统封装工艺中,通常先将晶圆分割成单个裸片,再对裸片进行QFP、BGA、CSP等形式的封装;而WLP实现了前道IC加工与后道IC组装在晶圆层面的整合。其基本工艺是在晶圆完成IC加工后,通过特定工艺直接在晶圆上构建IC互连接口,完成测试、老化等流程后再进行分割,直接产出IC成品。WLP的技术发展与晶圆级凸点技术紧密相关。自20世纪60年代起,IBM公司便在倒装芯片工艺中应用晶圆级凸点技术,WLP正是这一技术自然演进的成果。标准意义上的WLP封装尺寸与芯片一致,也被称为晶圆级芯片尺寸封装(WLCSP),属于真正意义上的芯片尺寸封装。随着技术需求的提升,为突破WLCSP在I/O数量上的限制,扇出型晶圆级封装(FOWLP)应运而生。FOWLP通过在芯片切割后重新排布、模压重组晶圆,实现了面积扩展与复杂的异构集成,提升了封装的集成度,降低了成本,增强了性能。与之对应,WLCSP也被称为扇入型(Fan - in)晶圆级封装(FIWLP)。

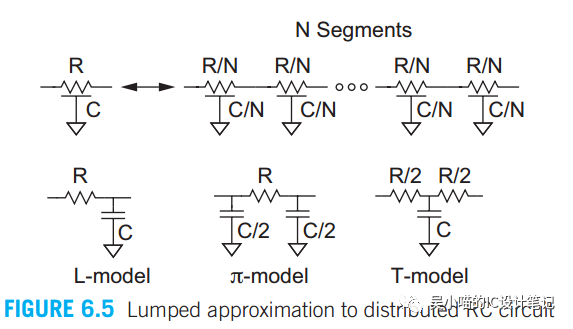

根据电极转移相关的方式,圆片级封装可粗略分为焊区上凸点(BOP)WLP、电极再分布WLP、包封式WLP和柔性载带WLP四种,其中电极再分布WLP是目前晶圆级封装技术的最主要形式。随着芯片复杂性的增加,添加金属重布线层,或称为电极再分布层(RDL)变得十分必要,它能够将焊球从芯片原本焊盘上转移到合适的凸点位置,以满足不断提高的性能需求。

WLP的优势与局限

一、优势

WLP的优势显著。从尺寸上看,它实现了封装面积与芯片面积近乎1:1,相比四边引脚扁平封装、板上芯片(COB)封装等,大幅缩小了在系统电路板上的占用空间,满足了现代电子产品尤其是便携式设备对小型化的极致追求。以一个10mm尺寸的芯片为例,四边引脚扁平封装的面积是900mm²,芯片与PWB直接引线键合的板上芯片(COB)封装的面积是225mm²,而WLP的封装面积和芯片面积相同,仅为100mm²,对于需要减小尺寸或重量的产品而言,采用WLP已经将尺寸或重量降到了最小。

在成本方面,WLP与IC加工类似,随着晶圆尺寸增大和IC尺寸减小,封装成本降低。它在晶圆划片前完成封装和测试,减少了传统封装中因晶圆增大需线性增加封装设备(如引线键合机、模塑机、测试仪和取放装置等)的成本投入;同时,采用标准卷带式传送设备和标准SMT技术进行组装装配,进一步优化了成本结构。并且,在圆片级一次性实现所有IC的测试和老化,也大大降低了测试和老化成本,这对于大规模生产来说,成本优势尤为明显。

在性能上,WLP采用薄膜工艺实现互连,缩短了引线长度,降低了寄生电阻、电容、电感,显著提升了电性能。WLP中的芯片尺寸通常较小,约10mm左右,I/O数从少到中等,一般约100左右,大部分WLP采用面阵列互连,这种互连方式具有诸多优点:一方面,焊料凸点比引线键合的引线尺寸小得多,电感和电阻都很小,从而拥有很好的电性能;另一方面,所有I/O焊盘都在芯片的有源面上方,互连区不超过芯片面积范围,且面阵列互连的I/O节距可以达到最大,可以直接与成本最低的PWB进行互连,大大提高了封装的实用性和经济性。

二、局限

不过,WLP也存在一定局限性。当IC的I/O数量较多时,为保证互连,焊球尺寸和节距需相应减小,这对PWB的制造工艺提出了极高要求,适配的高密度PWB成本昂贵,限制了其在高I/O芯片中的应用。例如,目前实际应用中的最小 PWB 节距已突破 0.5mm,达到 110μm 级别,若要降低到100μm,就需要在一块很大的电路板上采用12μm的光刻技术进行加工,这无疑是十分困难且成本高昂的。

此外,WLP需对晶圆上所有IC进行封装,在早期晶圆加工成品率较低时,会显著增加成本;尽管随着工艺成熟及 AI 检测技术(如 X 射线预筛选、缺陷自动识别)的普及,失效 IC 在封装前即可被高效剔除,资源浪费问题已大幅缓解,但仍是需要持续优化的环节。因为即使现在晶圆加工技术已经有了很大进步,仍难以保证晶圆上所有IC都是完好的,对失效IC进行封装会造成一定的资源浪费。

WLP的应用现状与未来趋势

目前,WLP已广泛应用于可擦除可编程只读存储器(EPROM)、模拟芯片、射频(RF)、集成无源器件(IPD)以及微机电系统(MEMS)等领域。国际半导体技术路线图(ITRS)将其定义为基于晶圆(或晶圆形式)实现封装和测试,且封装后的单个封装体可直接用于电路组装工艺的技术。其主要封装形式包括I/O端扇入型、I/O端扇出型、集成无源器件圆片级封装及各类传感器的圆片级封装等。以扇出型圆片级封装——嵌入式圆片级球栅阵列封装(embedded Wafer Level Ball Grid Array,eWLB)为例,其典型的封装结构所涉及的主要封装材料包括制造再布线层(Redistribution Layer,RDL)中介质层的光敏材料、布线金属层材料和实现微互连的微细连接材料及包封保护材料等。

随着半导体产业向更高集成度、更小尺寸、更低功耗方向发展,WLP 与 2.5D/3D 封装、Chiplet 技术深度融合,凭借其在异构集成方面的潜力,将成为未来先进封装的重要发展方向。

同时,随着技术的不断进步,WLP在解决现有局限性方面也有望取得突破,从而拓展其在更多领域的应用。

-

封装

+关注

关注

128文章

9142浏览量

147899 -

晶圆级封装

+关注

关注

5文章

44浏览量

11775 -

先进封装

+关注

关注

2文章

520浏览量

972

原文标题:晶圆级封装简介

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

晶圆级封装技术的概念和优劣势

晶圆级封装技术的概念和优劣势

评论