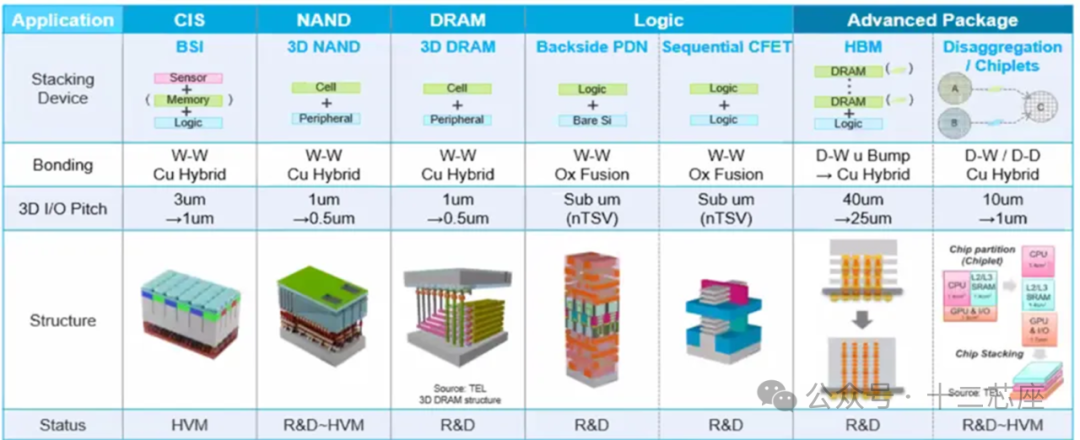

电子发烧友综合报道 作为HBM和3D NAND的核心技术之一,混合键合在近期受到很多关注,相关设备厂商尤其是国产设备厂商的市场前景巨大。那么混合键合是什么?

混合键合是一种结合介电层键合和金属直接键合的先进封装技术,其核心目标是实现芯片间高密度、低电阻的垂直互联。

在工艺过程中,需要经过对准和键合、后键合处理等几个流程。在对晶圆表面进行化学机械拋光(CMP)和清洗之后,通过光学或电子束对准系统实现亚微米级(通常<200nm)的芯片间精准对齐,尤其在芯片到晶圆(D2W)键合中,对准误差需接近零。

键合的方式有晶圆到晶圆W2W和芯片到晶圆D2W两种,在键合过程中,铜触点与介电层(如SiO₂)同时接触,通过热压或<400°C的低温退火实现金属-金属和介电层-介电层的同步键合。

在键合后,还需要通过CMP工艺调整铜层高度,确保铜触点略微凹陷于介电层表面(通常为50-100nm),以避免短路并提升键合强度;同时键合过程中产生的热量需通过散热结构(如嵌入式热沉)快速导出,防止局部热应力导致晶圆变形。

其中技术难点,主要有5点。首先从前面的工艺流程可以看到对准精度是非常重要的,混合键合的互联密度可达1000-5000 PPI,要求对准误差小于200nm,这对设备(如高精度对准机)和工艺稳定性提出了极高挑战;

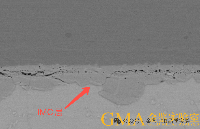

其次是铜触点的凹陷深度需高度均匀,否则会导致键合界面接触不良或介电层破裂,这需要CMP工艺参数和设备的能力去实现;

键合表面的粗糙度需控制在1nm以下,且必须避免任何有机或金属污染,对清洗技术提出极高要求;

键合后的低温退火(通常<400°C)需在保护气氛(如氮气)中进行,以消除界面缺陷并增强键合强度,但过高的热应力可能导致晶圆翘曲或材料疲劳;

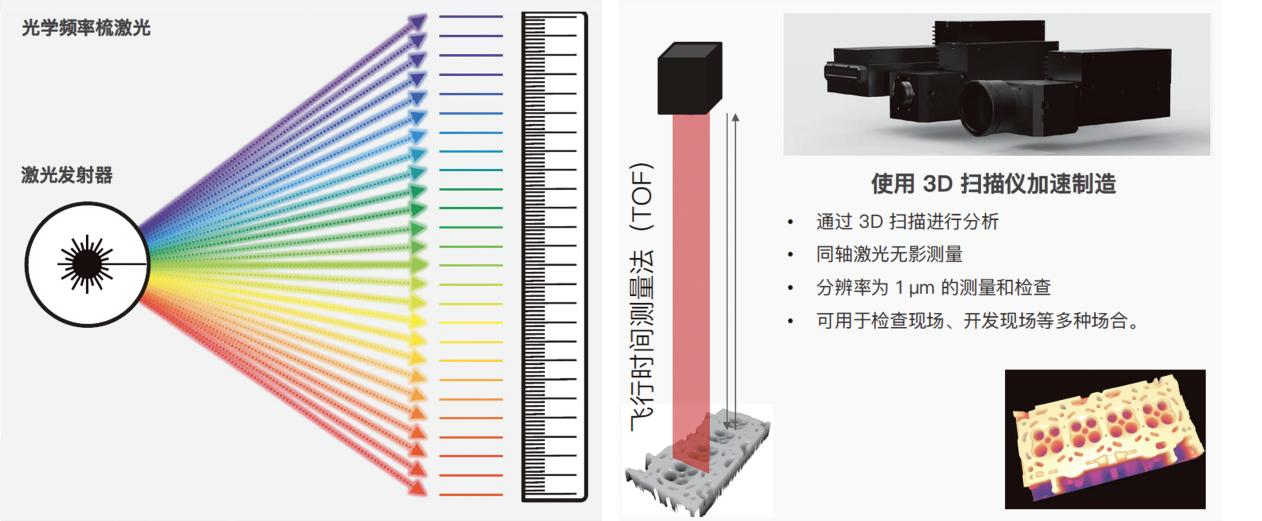

最后,多次键合/解键合载体的使用、高精度设备投入及工艺复杂性显著推高成本。此外,微小缺陷可能导致整片晶圆失效,需通过在线检测技术提升良率。

相对应地,混合键合工艺中,涉及到多种关键设备包括CMP、等离子体活化与清洗设备、高精度对准与键合设备、退火设备、检测与分析设备、电镀ECU设备(用于铜柱的电化学沉积)、减薄与研磨设备等。

混合键合工艺对设备的精密性、稳定性和集成度要求极高,尤其在对准、键合、CMP和退火 环节存在显著技术壁垒。目前,此类设备市场主要由日韩厂商,宝库DISCO、东京电子和欧美厂商KLA、应用材料等主导;但国产设备已在CMP和检测领域逐步突破,比如中电科45所、华海清科等。未来,随着存储、高性能计算和异构集成需求的增长,混合键合设备的市场规模将持续扩大。

发布评论请先 登录

混合键合良率卡脖子?屹立芯创SRS:预键合与退火之间的关键一步

高频超声键合技术:引线键合工艺优化与质量检测方法

北方华创发布12英寸芯片对晶圆混合键合设备Qomola HPD30

NTC热敏芯片键合工艺介绍

详解先进封装中的混合键合技术

IGBT 芯片平整度差,引发键合线与芯片连接部位应力集中,键合失效

混合键合市场空间巨大,这些设备有机会迎来爆发

混合键合市场空间巨大,这些设备有机会迎来爆发

评论