SN65MLVD204B:具有IEC ESD保护的多点LVDS线路驱动器和接收器 在硬件设计领域,数据传输的高效性和稳定性至关重要。SN65MLVD204B作为一款具有IEC ESD保护的多点

2025-12-19 09:30:05 183

183 包括MIL-STD-883C method 3015.7和EIA/JESD22-A114-A。HBM测试的静电电压可从小于2kV到16kV不等。

● 机器放电模式(MM, Machine Model

2025-11-26 07:37:49

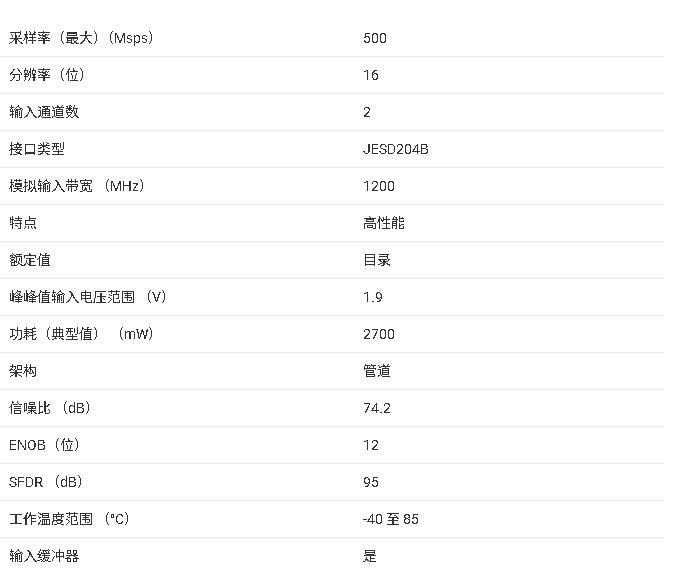

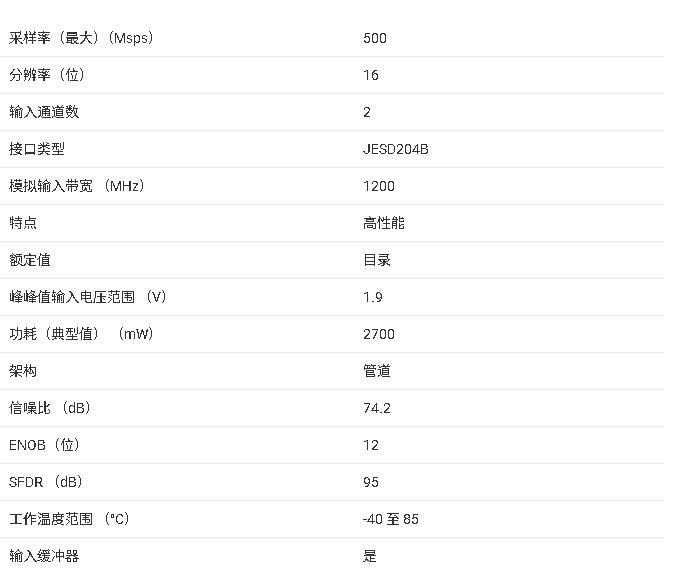

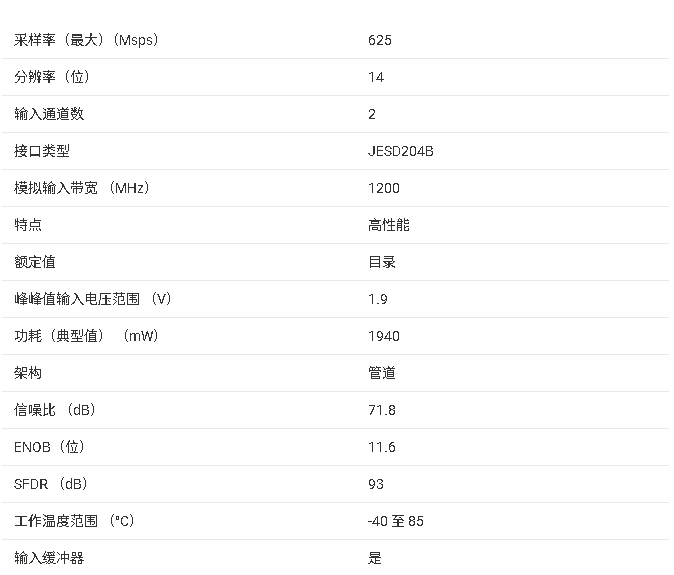

ADS42JB69和ADS42JB49是高线性度、双通道、16位和14位、250MSPS、模数转换器(ADC)。这些器件支持数据速率高达

3.125 Gbps 的JESD204B串行接口。缓冲

2025-11-14 11:18:08 718

718

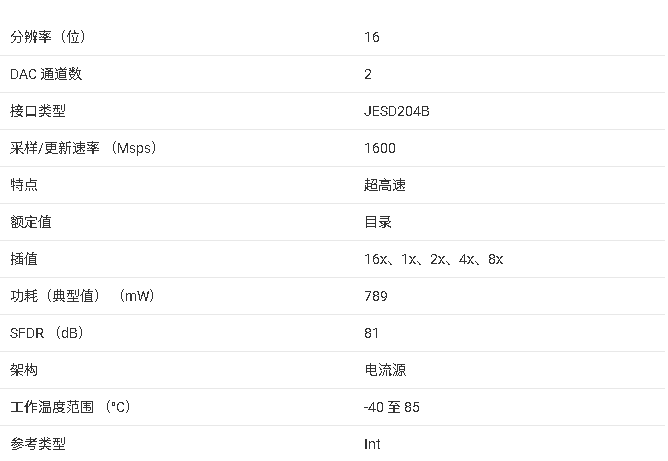

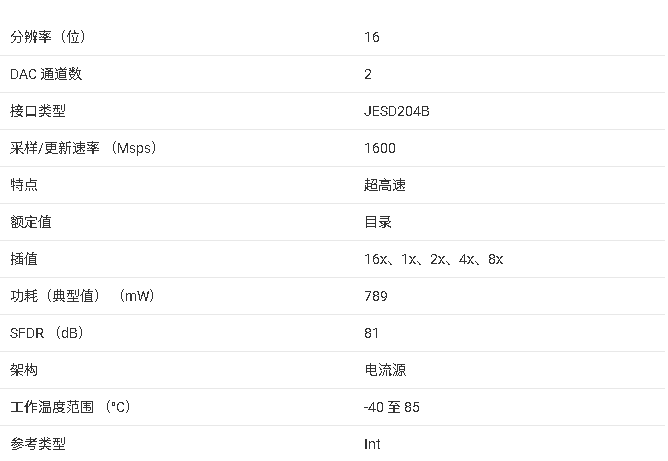

终端兼容的 DAC37J84/DAC38J84 系列是一款低功耗、16 位、四通道、 1.6/2.5 GSPS 数模转换器 (DAC),带JESD204B接口。

数字数据通过 1、2、4 或

2025-11-13 14:31:02 472

472

引脚兼容的DAC37J82/DAC38J82系列是一款非常低功耗、16位、双通道、 1.6/2.5 GSPS 数模转换器 (DAC),带JESD204B接口。最大输入数据速率 是 1.23 GSPS

2025-11-13 13:52:47 434

434

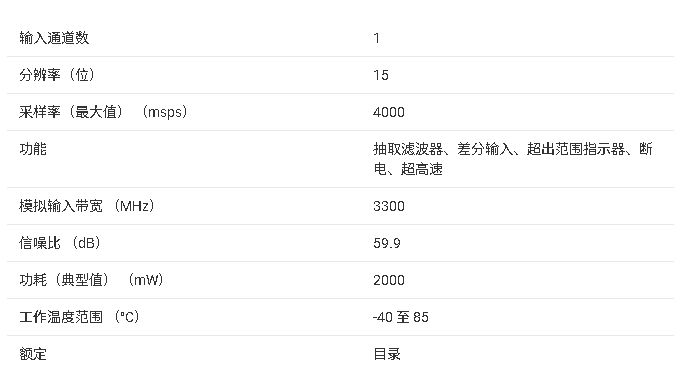

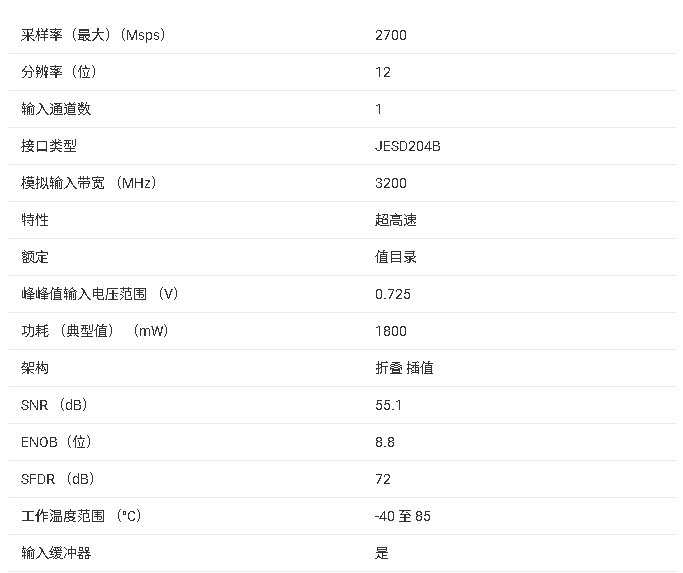

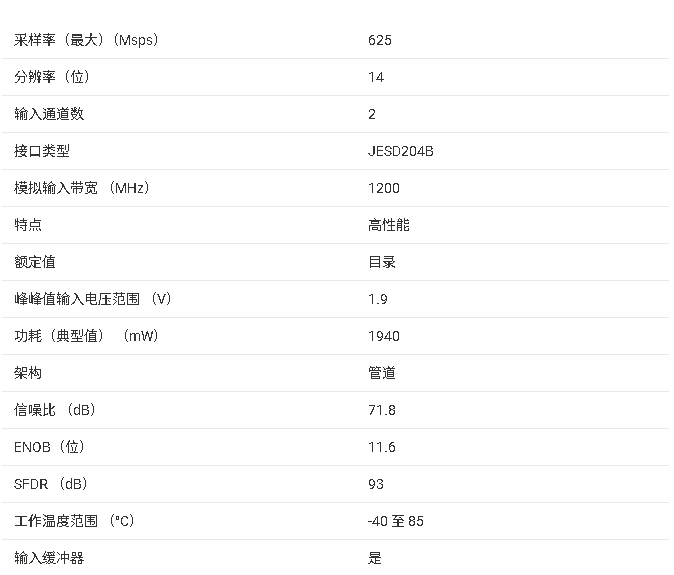

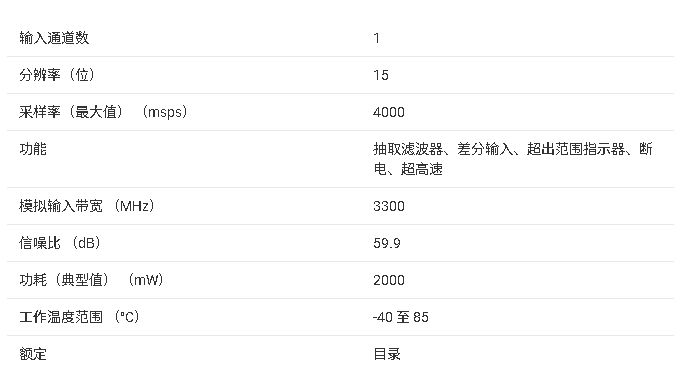

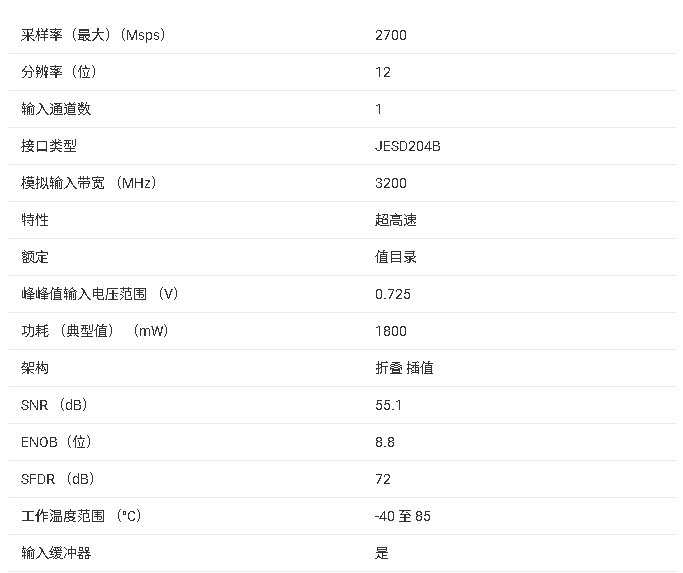

分频器为系统时钟架构设计提供了更大的灵活性,而SYSREF输入则实现了完整的系统同步。ADC34J4x 系列支持串行电流模式逻辑 (CML) 和JESD204B接口,以减少接口线的数量,从而实现高系统集成

2025-11-13 09:27:02 381

381

。选定的频率块在JESD204B串行接口上可用。数据输出为基带15位复数信息,便于下游处理。根据数字下变频器(DDC)抽取和链路输出速率设置,该数据在串行接口的1至5个通道上输出。

2025-11-12 18:13:11 1299

1299

可在JESD204B串行接口上使用。数据作为基带15位复数信息输出,以便于下行处理。根据数字下变频器(DDC)抽取和链路输出速率设置,该数据在串行接口的1至5个通道上输出。

2025-11-12 16:23:44 401

401

和下变频。选定的频率块可在JESD204B串行接口上使用。数据作为基带15位复数信息输出,以便于下行处理。根据数字下变频器(DDC)抽取和链路输出速率设置,该数据在串行接口的1至5个通道上输出。

2025-11-12 15:54:08 433

433

和下变频。选定的频率块可在JESD204B串行接口上使用。数据作为基带15位复数信息输出,以便于下行处理。根据数字下变频器(DDC)抽取和链路输出速率设置,该数据在串行接口的1至5个通道上输出。

2025-11-12 15:05:45 396

396

分频器为系统时钟架构设计提供了更大的灵活性,而 SYSREF 输入则支持完整的系统同步。ADC34J4x 系列支持串行电流模式逻辑 (CML) 和 JESD204B 接口,以减少接口线的数量,从而实现高系统集成密度。

2025-11-12 14:46:20 419

419

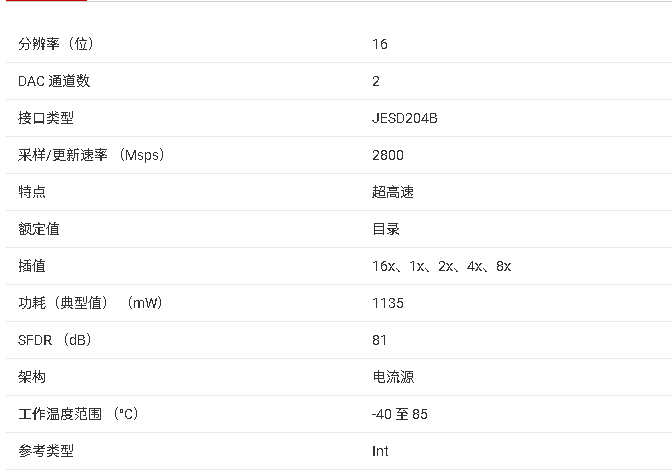

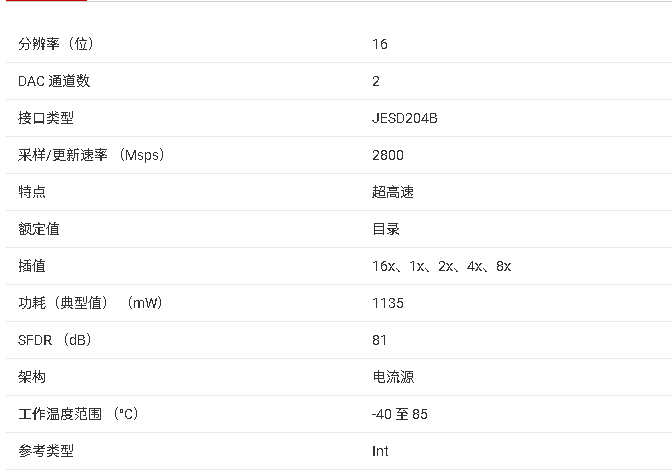

该DAC39J82是一款非常低功耗、16 位、双通道、2.8 GSPS 数模 具有JESD204B接口的转换器 (DAC)。最大输入数据速率为1.4 GSPS。

数字数据通过 1、2、4 或

2025-11-12 11:32:03 547

547

输入分频器为系统时钟架构设计提供了更大的灵活性,而SYSREF输入则实现了完整的系统同步。这些器件支持JESD204B接口,以减少接口线的数量,从而实现高系统集成密度。

2025-11-12 11:25:21 492

492

输入分频器为系统时钟架构设计和SYSREF输入提供了更大的灵活性 实现完整的系统同步。这些设备支持JESD204B接口,以减少 接口线的数量,从而实现高系统集成密度。The JESD204B 接口是一个

2025-11-12 09:23:14 457

457

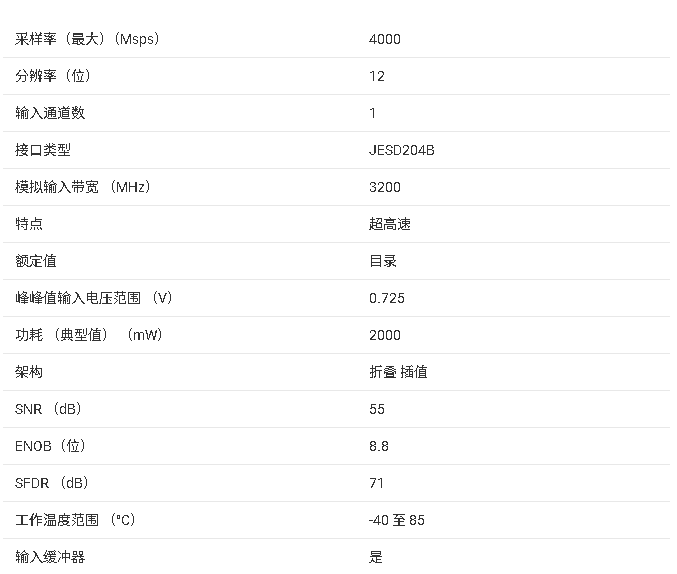

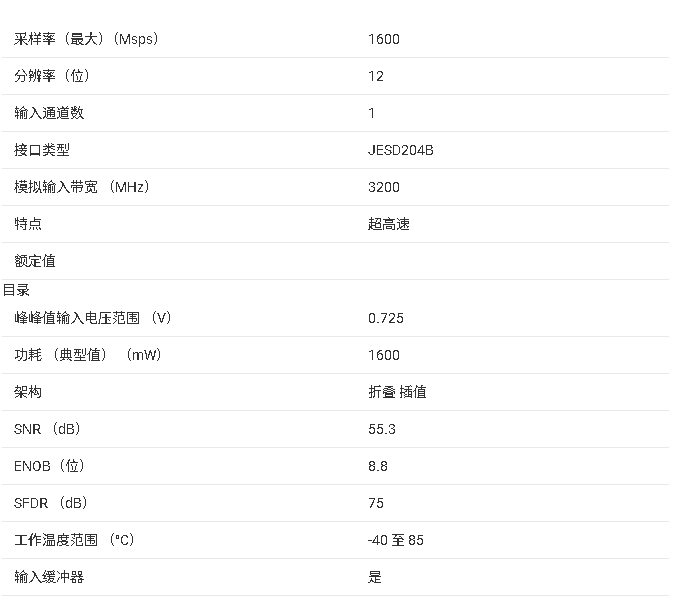

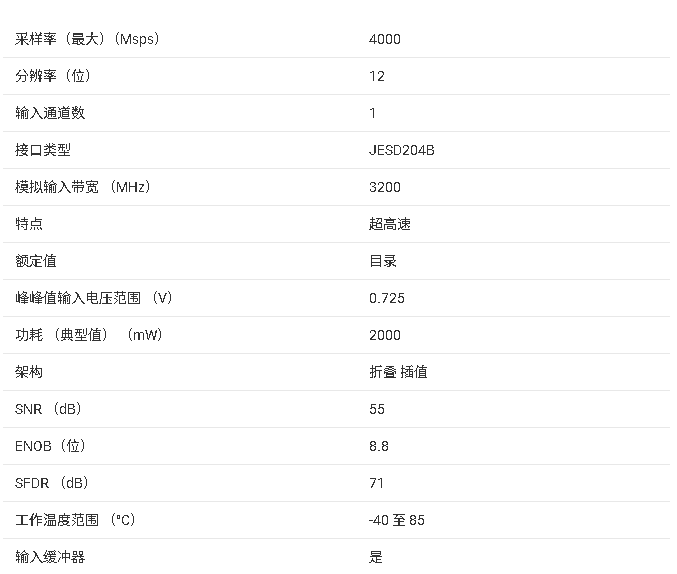

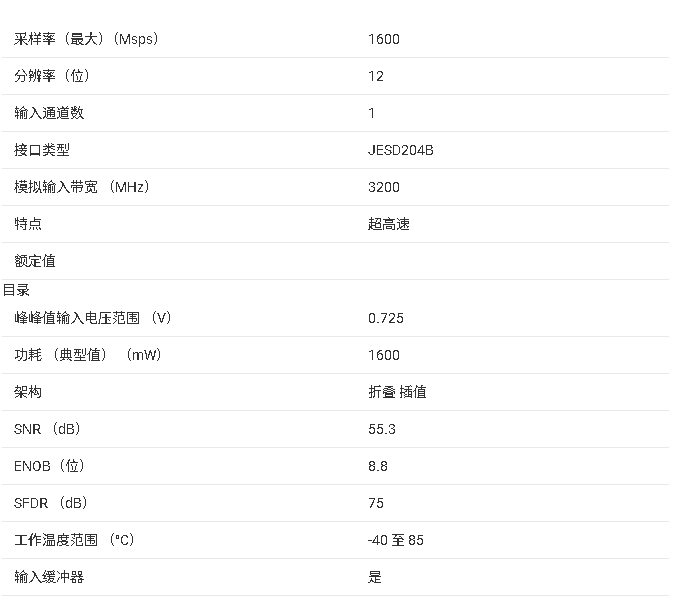

实现最高动态范围的应用。该器件支持数据速率高达 10.0 Gbps 的JESD204B串行接口,每个 ADC 支持一个或两个通道。缓冲模拟输入在宽频率范围内提供均匀的输入阻抗,并最大限度地减少采样保持

2025-11-11 09:47:30 450

450

实现最高动态范围的应用。该器件支持数据速率高达 6.25 Gbps 的JESD204B串行接口。缓冲模拟输入在宽频率范围内提供均匀的输入阻抗,并最大限度地减少采样保持毛刺能量。每个ADC通道都可以选择

2025-11-11 09:36:04 415

415

动态范围的应用。该器件支持数据速率高达10 Gbps的JESD204B串行接口,每个ADC支持两个或四个通道。缓冲模拟输入在宽频率范围内提供均匀的输入阻抗,并最大限度地减少采样保持毛刺能量。可选

2025-11-10 14:56:02 450

450

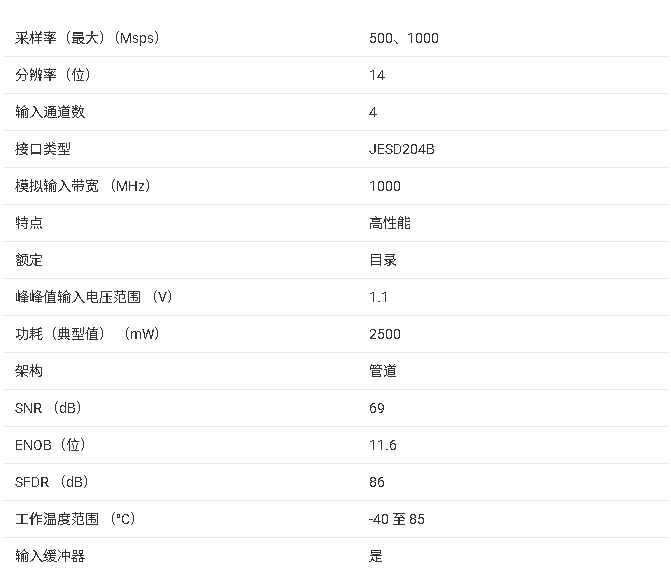

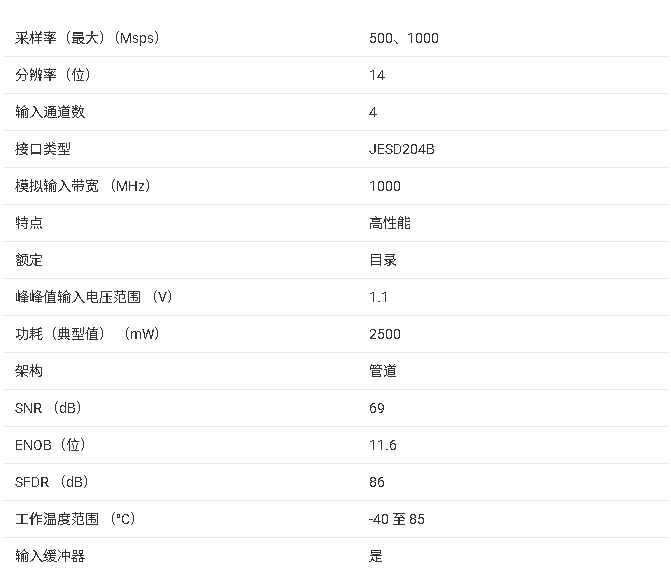

该ADS58J64是一款低功耗、宽带宽、14位、1-GSPS、四通道、电信接收器设备。该ADS58J64支持数据速率高达 10 Gbps 的 JESD204B 串行接口,每个通道一个通道。缓冲

2025-11-07 18:12:43 1439

1439

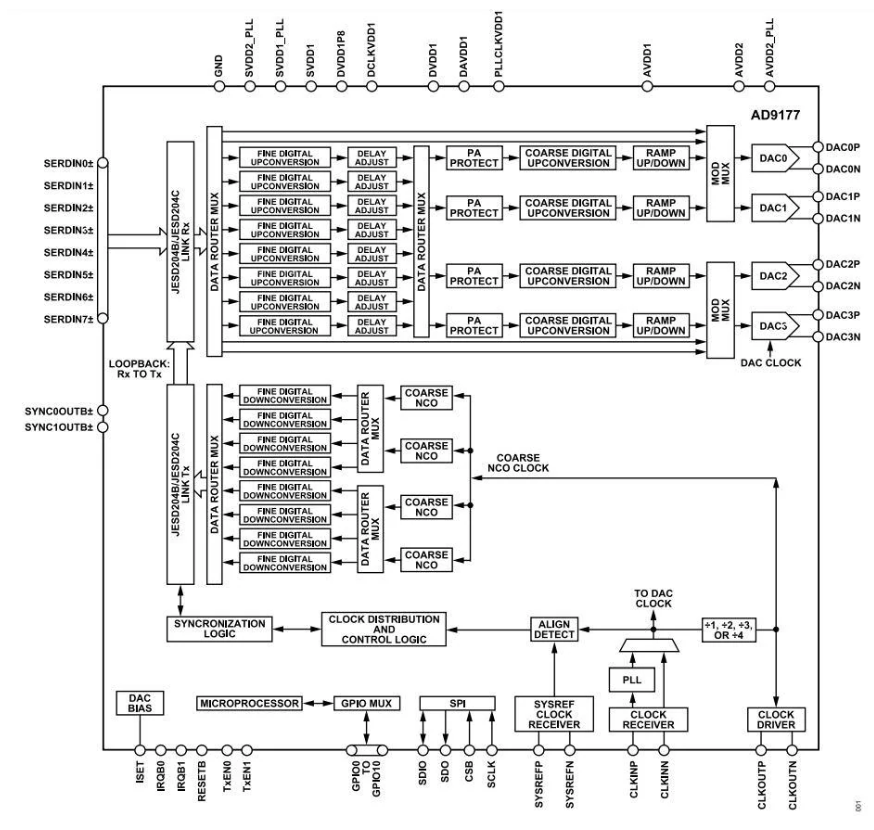

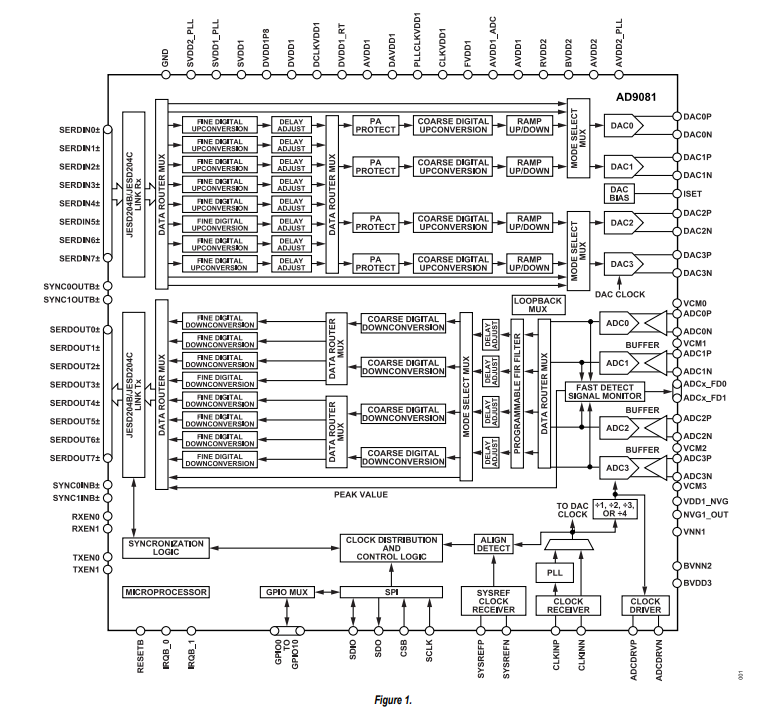

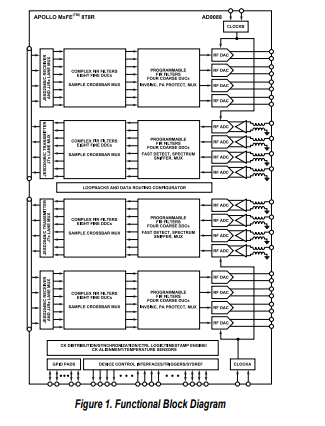

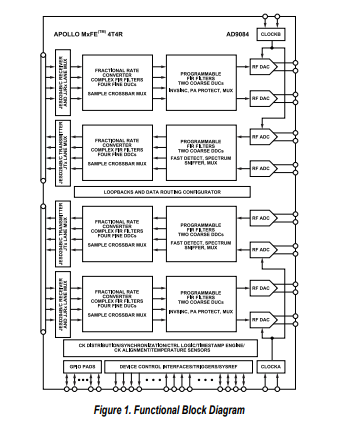

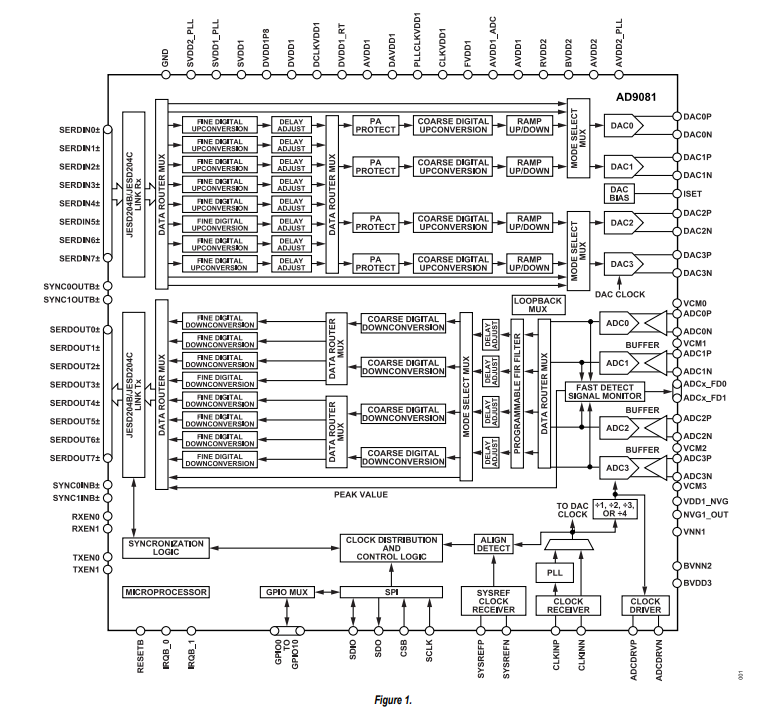

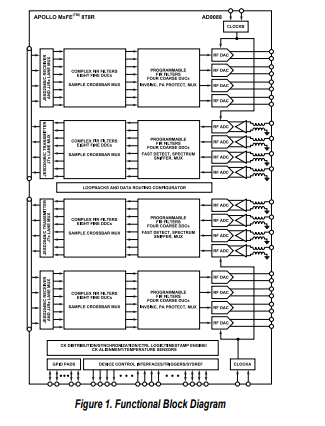

为各种应用生成信号,包括用于无线基站和雷达的 3G/4G 信号。

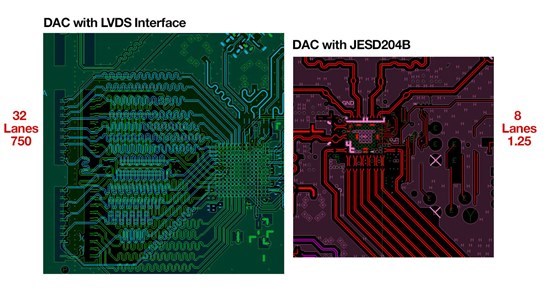

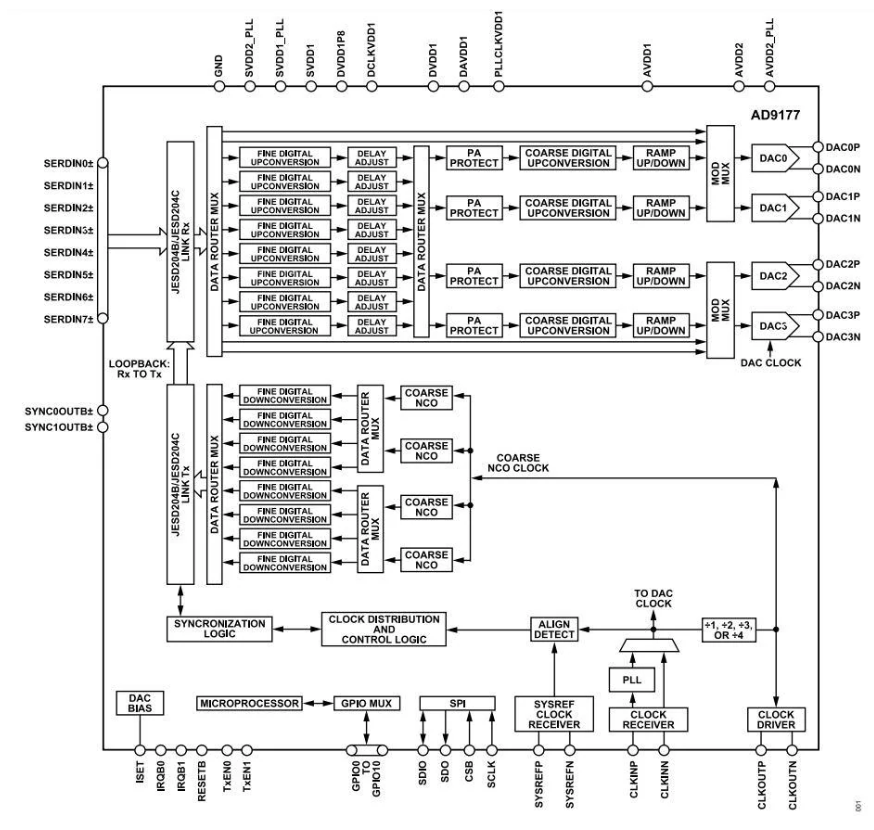

这些器件具有低功耗JESD204B接口,具有多达 8 个通道,最大比特率为 12.5 Gbps,允许每通道 1.25 GSPS 复合

2025-11-07 14:47:20 505

505

为各种应用生成信号,包括用于无线基站和雷达的 3G/4G 信号。

这些器件具有低功耗JESD204B接口,具有多达 8 个通道,最大比特率为 12.5 Gbps,允许每通道 1.25 GSPS 复合

2025-11-06 16:02:08 499

499

JESD204B接口,最大比特率为12.5 Gbps (DAC38RF89)和12.8 Gbps (DAC38RF82)。

2025-11-06 15:53:50 445

445

ADS54J64器件是一款四通道、14位、

1GSPS、模数转换器(ADC),提供宽带宽、2倍过采样和高信噪比。该ADS54J64支持数据速率高达 10 Gbps 的JESD204B串行接口,每个

2025-11-06 14:28:36 377

377

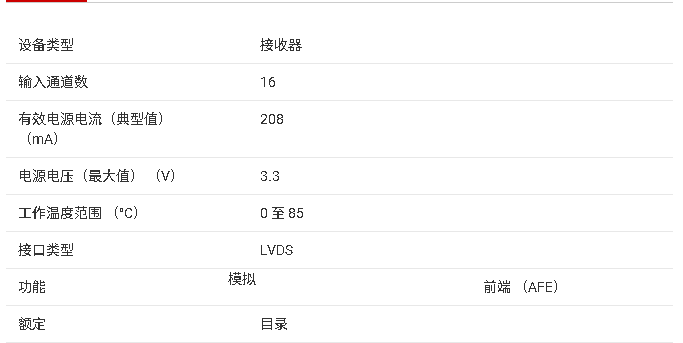

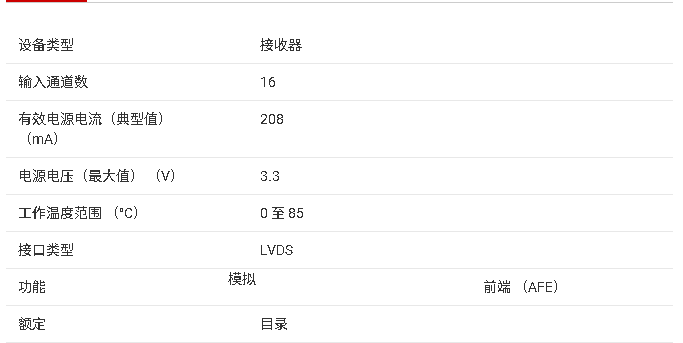

AFE58JD48 设备是一款高度集成的模拟前端 (AFE) 解决方案,专为高级超声系统而设计。

AFE58JD48 是一款集成式 AFE,针对高级医疗超声应用进行了优化。该器件通过具有三个芯片的多芯片模块 (MCM) 实现:一个 16 通道压控放大器 (VCA) 芯片和两个 8 通道模数转换器 (ADC) 芯片。

2025-11-04 09:38:13 395

395

ADC34RF55IRTDT内容介绍: 哈喽,朋友们,今天我要向大家介绍的是一款数模转换器——ADC34RF55IRTDT。 它配备了两位得力助手——双带数字下变频器(DDC)。当它捕捉到高频信号后,这两位助手能立刻将信号“翻译”成更低频率的基带信号,并过滤掉不必要的杂波,大大减轻了后续处理器(如FPGA

2025-10-15 15:56:49

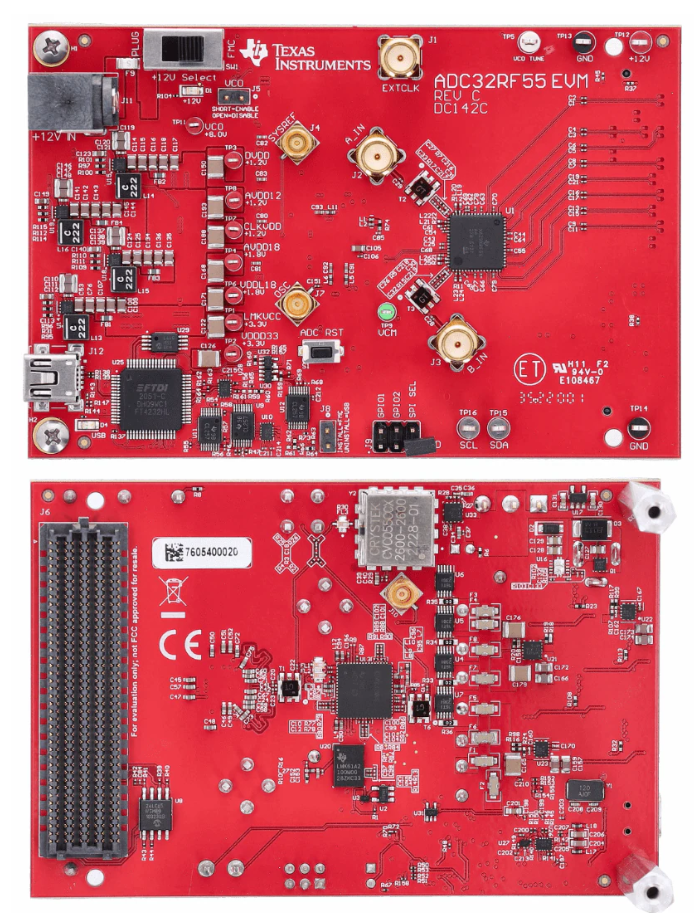

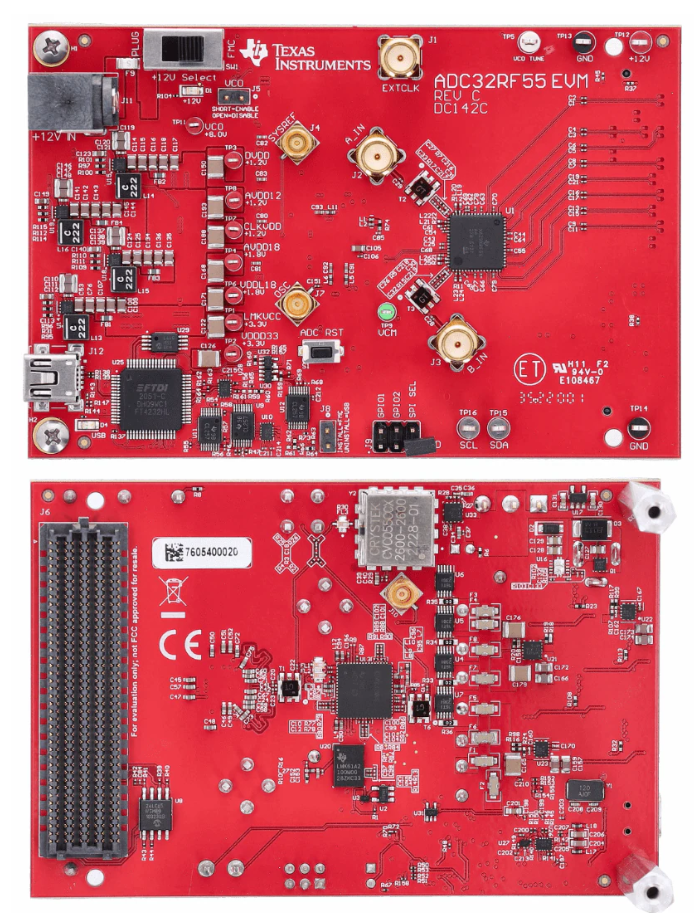

ADC32RF55EVM内容介绍: 哈喽,朋友们,今天我要向大家介绍的是一款数模转换器评估板——ADC32RF55EVM。 它就像一群训练有素的接待员,负责将外界的信号进行“梳妆打扮”:变压器负责将单端信号转换为平衡的差分信号,滤除共模噪声;而放大器则像一个精准的音量调节器,确保信号的幅度恰好能被 ADC

2025-10-15 15:15:58

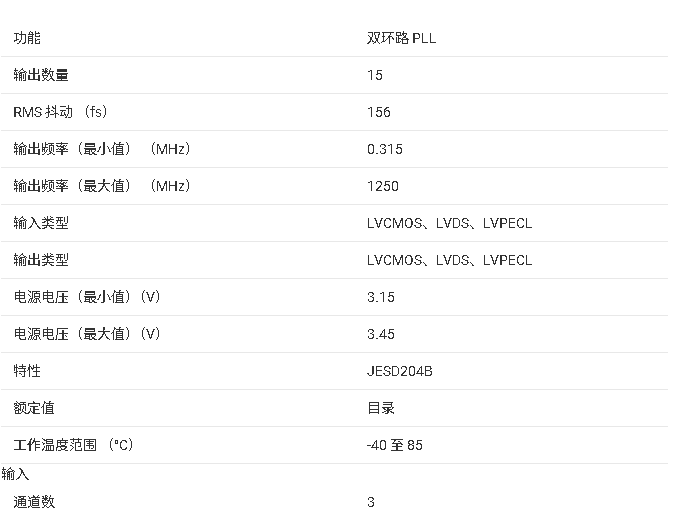

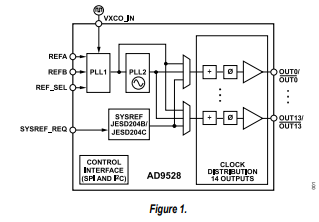

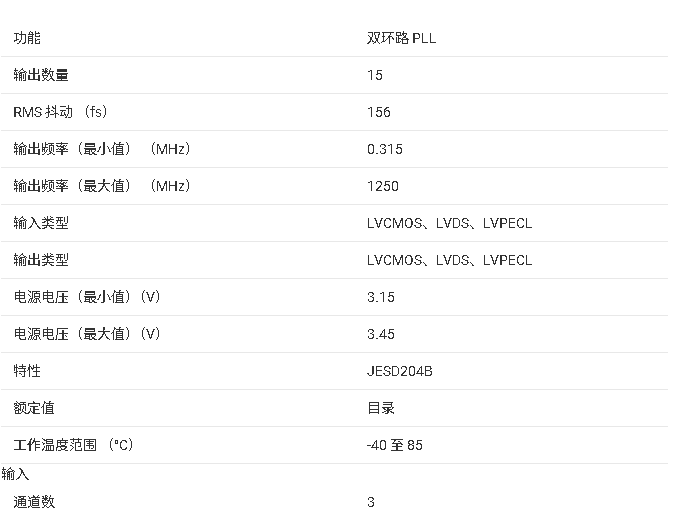

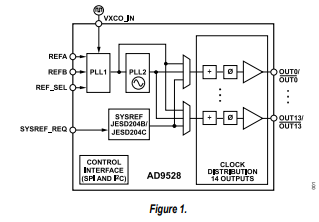

AD9528是一款双级PLL,集成JESD204B SYSREF发生器,可用于多器件同步。

2025-10-15 10:24:53 1197

1197

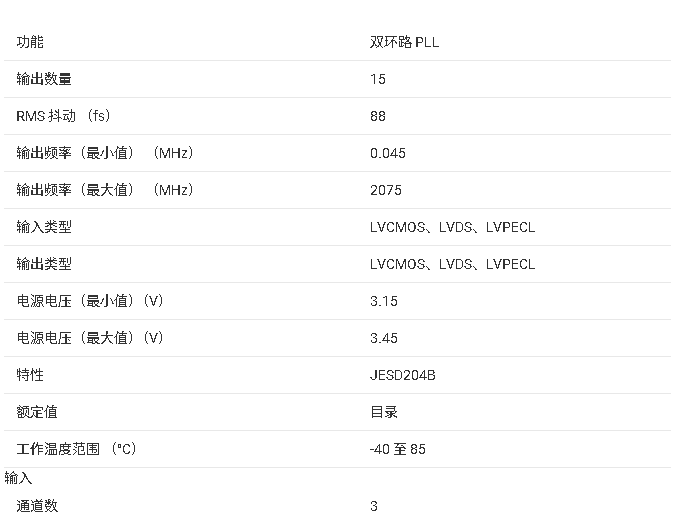

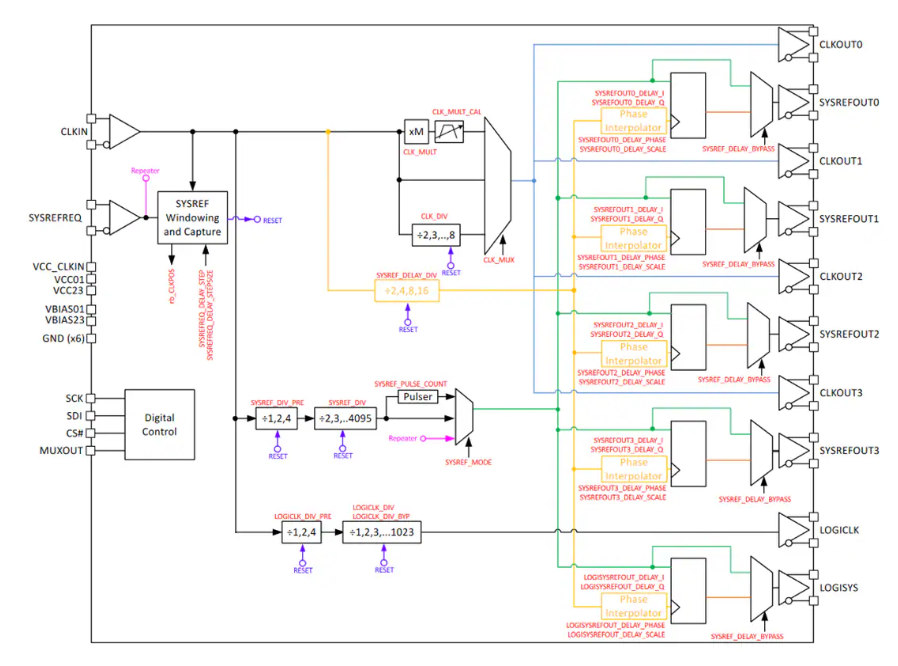

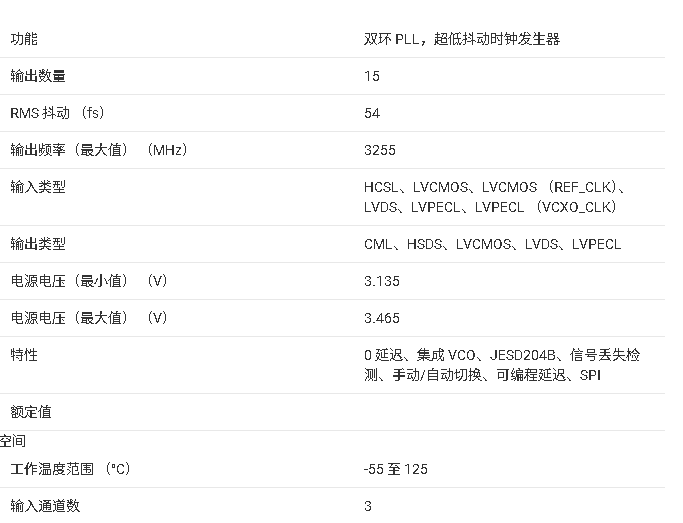

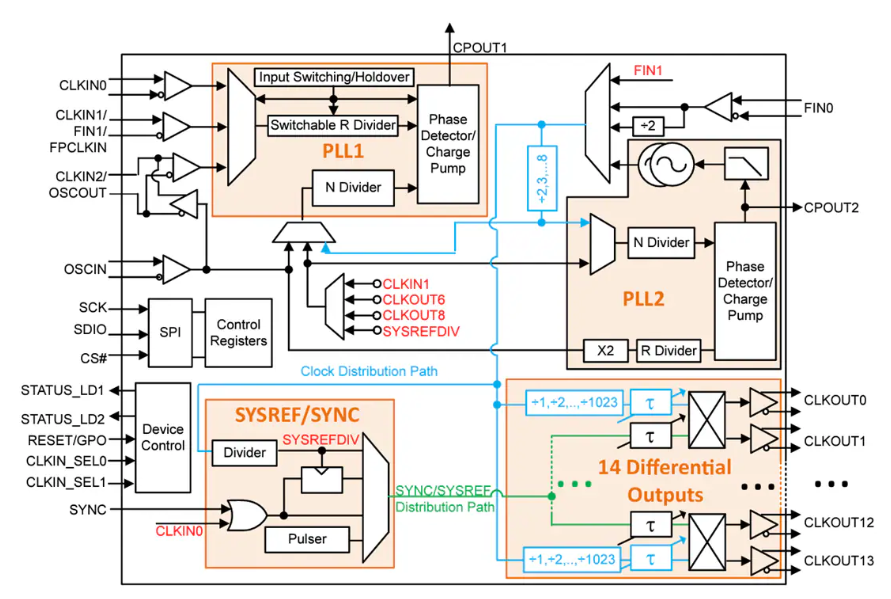

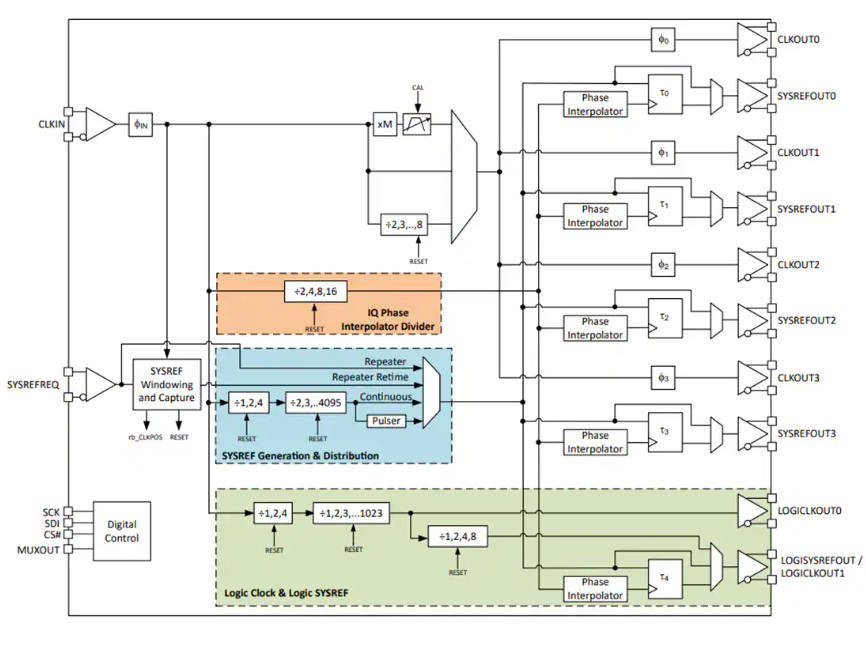

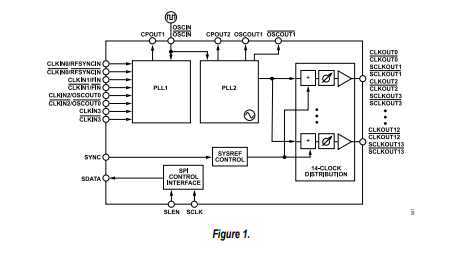

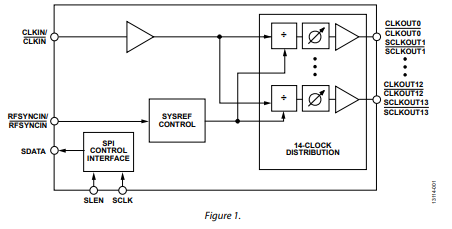

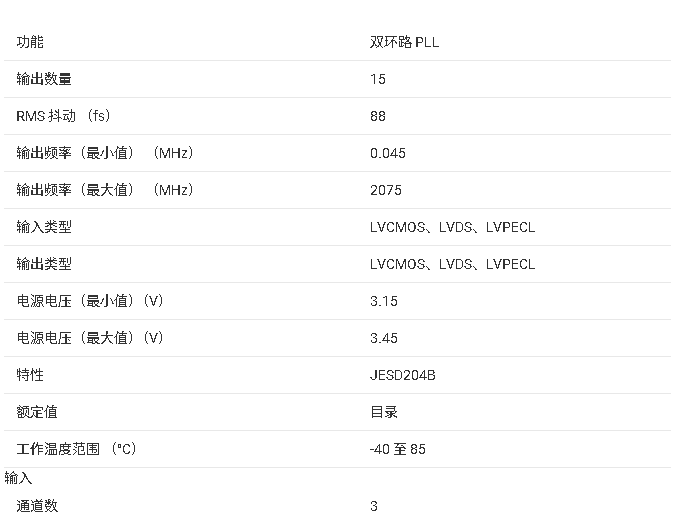

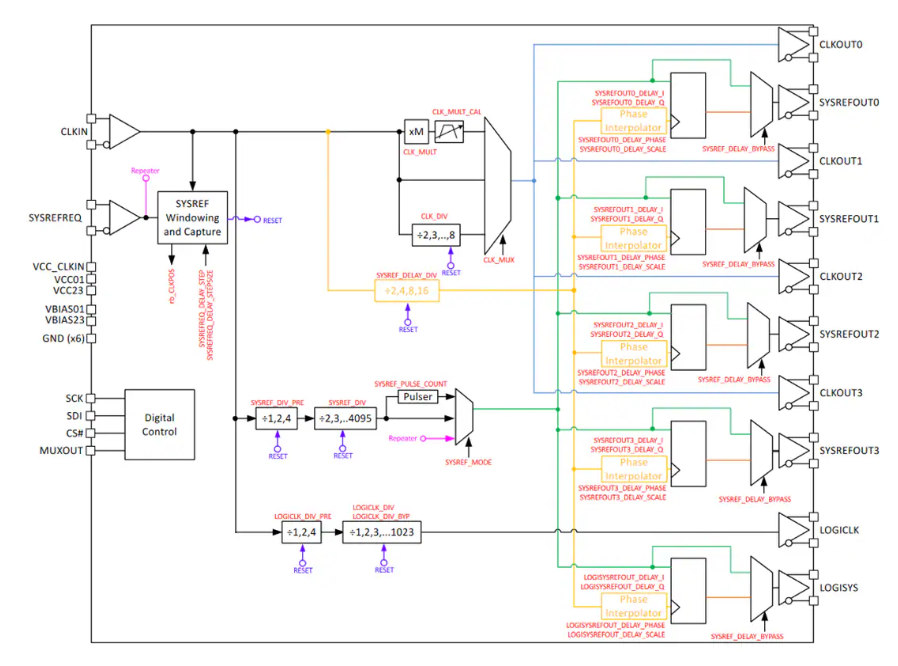

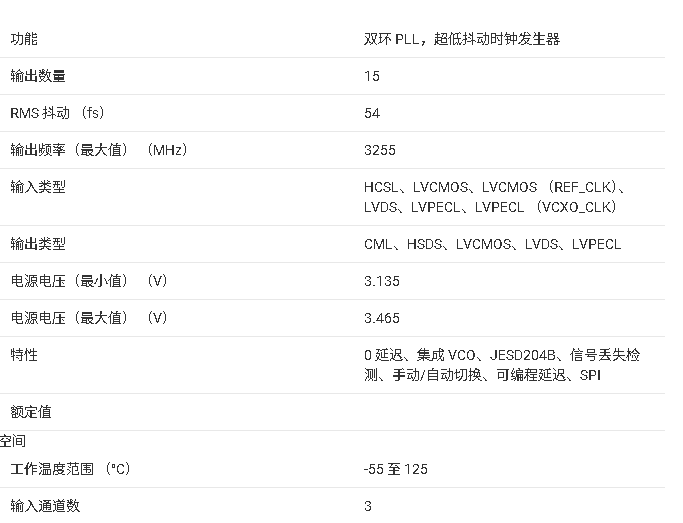

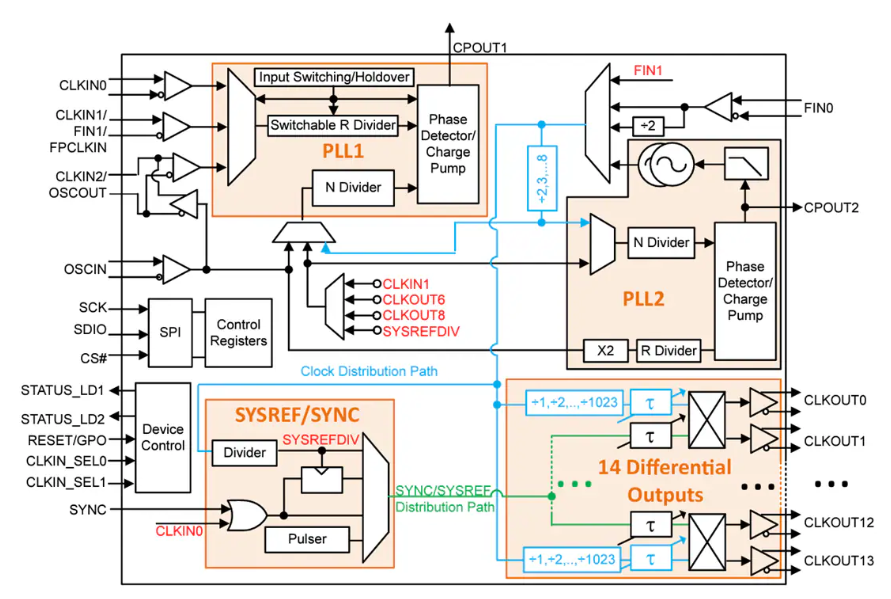

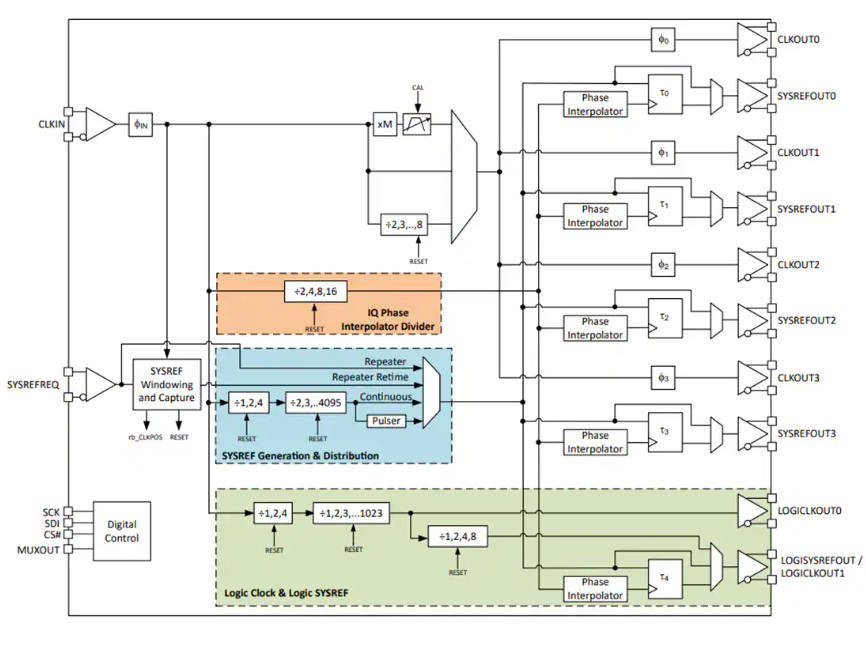

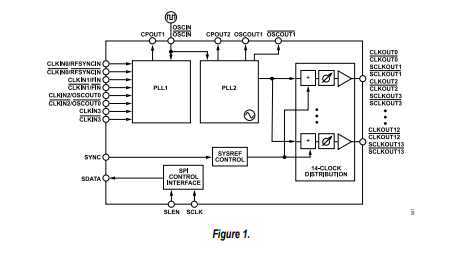

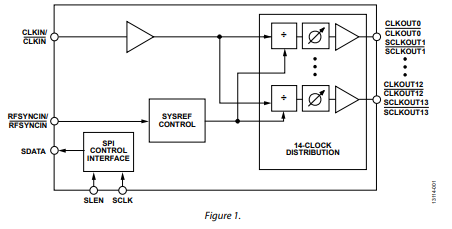

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

2025-09-15 10:10:11 848

848

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

2025-09-15 10:03:34 665

665

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

2025-09-14 11:07:35 901

901

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。

2025-09-13 09:35:35 1028

1028

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。16 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 8 个 JESD204B 转换器或其他逻辑器件。第 17 个输出可配置为提供来自 PLL2 的信号或来自外部 VCXO 的副本。

2025-09-12 16:50:34 907

907

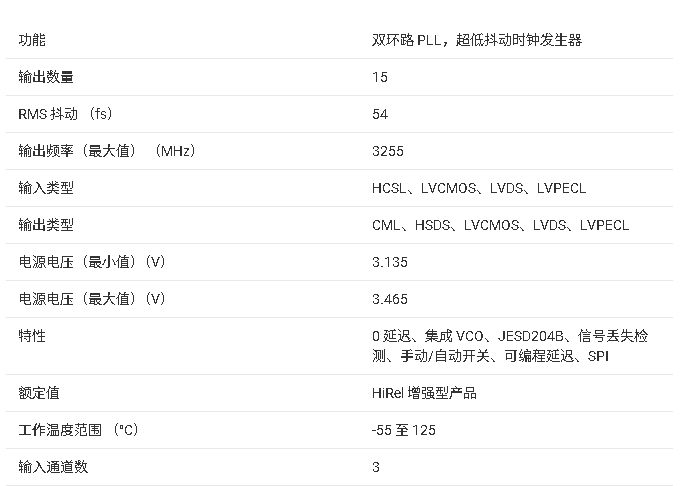

LMK04828-EP 器件是业界性能最高的时钟调理器,支持 JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件

2025-09-12 16:13:11 831

831

LMK04228 器件是业界高性能时钟调节器,支持 JEDEC JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件

2025-09-12 15:02:13 611

611

该LMK04832是一款超高性能时钟调节器,支持 JEDEC JESD204B,还与 LMK0482x 系列器件引脚兼容。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个

2025-09-12 14:11:12 929

929

LMK04832-SP 是一款高性能时钟调节器,支持 JEDEC JESD204B,适用于太空应用。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或

2025-09-11 18:19:56 875

875

Texas Instruments LMX1204 JESD缓冲器/多路复用器/分频器具有高频能力和极低抖动。这一特性可在不降低信噪比的情况下,很好地解决时钟精度、高频数据转换器问题。四个高频时钟

2025-09-11 14:47:51 618

618

LMK04832-SEP 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B

2025-09-11 10:43:33 649

649

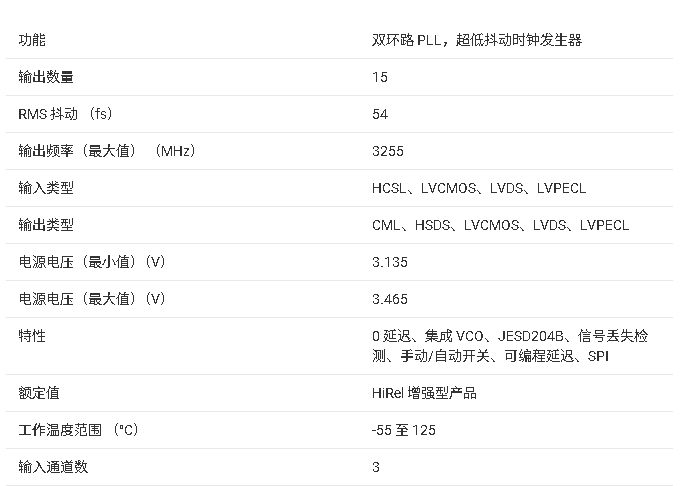

LMK04368-EP 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个

2025-09-11 10:23:20 652

652

LMK04714-Q1 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个

2025-09-11 10:07:11 560

560

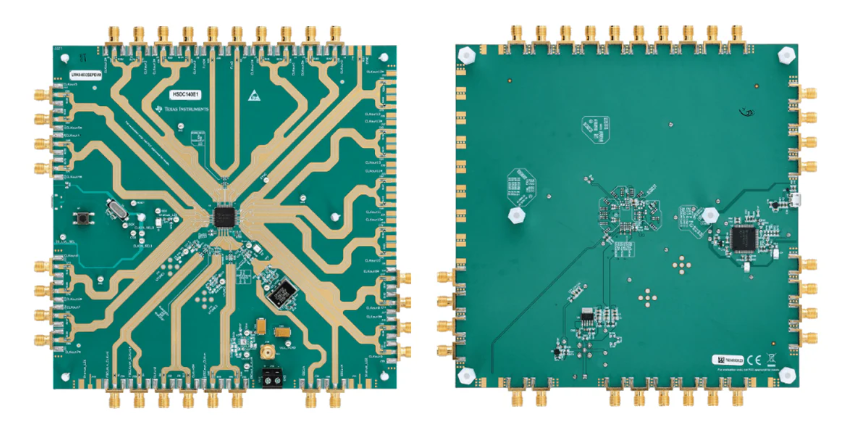

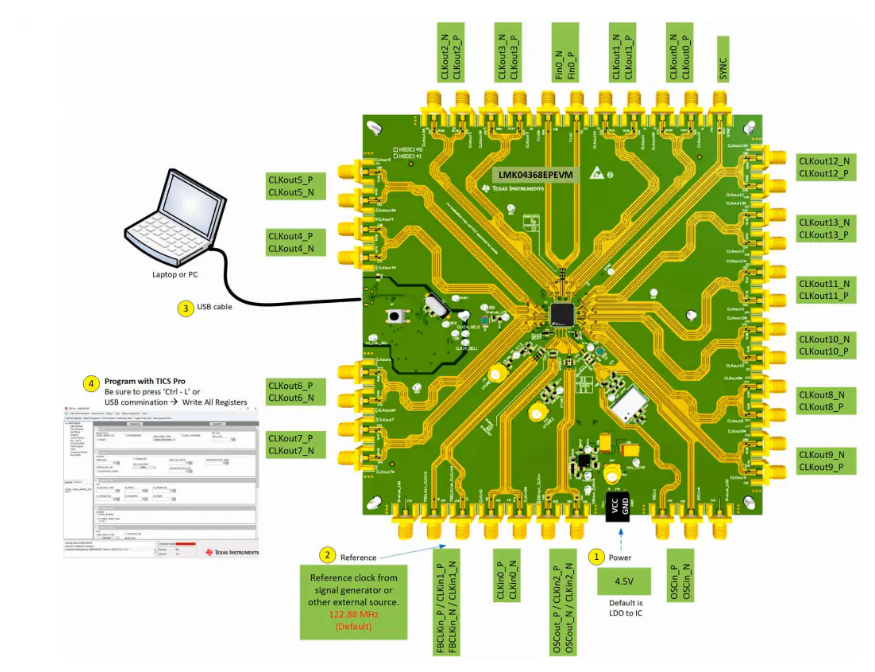

Texas Instruments LMK04832SEPEVM评估模块为LMK04832-SEP开发提供了绝佳的入门方法。LMK04832-SEP是一款空间级、超低噪声、JESD204B/C、双

2025-09-07 14:51:45 877

877

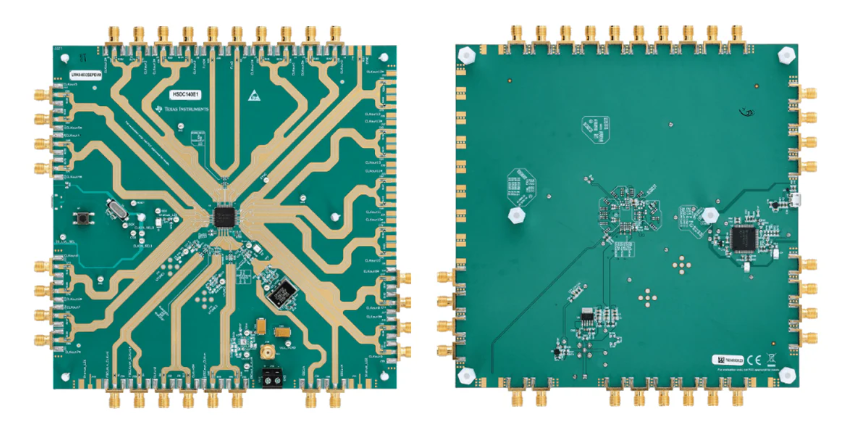

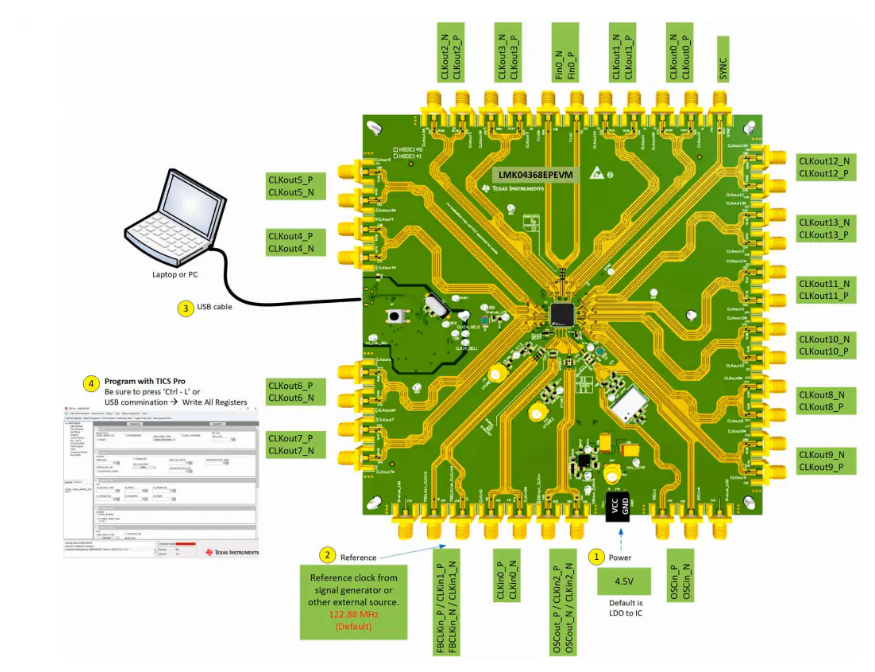

Texas Instruments LMK04368EPEVM评估模块用于演示LMK04368-EP的性能和特性。LMK04368-EP是一款高性能超低噪声JESD204B双环路时钟抖动清除器。每个LMK04368EPEVM评估模块上的TI LMK04368-EP是一个工程模型,仅用于工程评估。

2025-09-07 14:25:34 827

827

年发布)

发布时间

2006年(JEDEC标准JESD204)

2008年(JEDEC标准JESD204A)

2011年(JEDEC标准JESD204B)

核心定位

定义首个串行化数据转换器接口标准

2025-09-05 21:18:18

Texas Instruments ADC32RF55EVM评估模块用于演示ADC32RF55高速JESD204B接口模数转换器 (ADC) 性能。ADC32RF55EVM具有板载电压调节、时钟解决方案 (LMK04832)、变压器耦合模拟输入和USB接口,可实现轻松评估。

2025-09-02 13:56:30 736

736

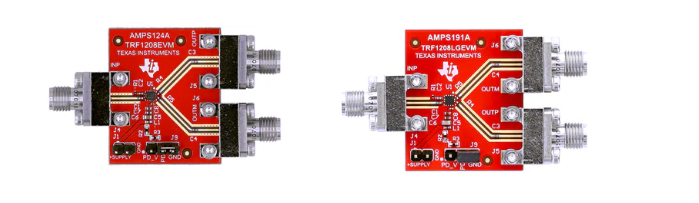

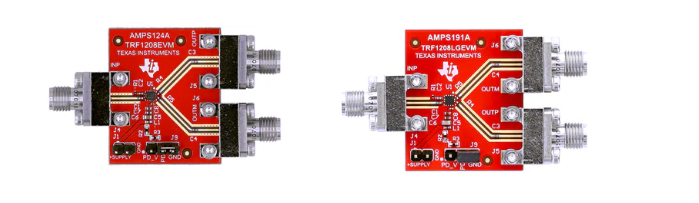

宽带直接射频采样评估。 TRF1208评估模块支持JESD204B/C,可实现同步和兼容性。这些评估模块可在5.5V单输入电压下工作,包含完整的电源管理电路。TRF1208模块具有JESD204B/C

2025-08-27 11:42:55 649

649

10 GbE、CPRI、JESD204B/C 等协议• DDR3 接口:1833 Mbps(900 MHz)• LVDS:1.4 Gbps/对,适用于高速 ADC/DAC 直连关键特性1. 低功耗:20

2025-08-21 09:15:02

Rapid IO、JESD204B/C、USB3.2/3.1/3.0、10GBASE-R/KR等其他协议。凭借其优越的性能和低功耗特性,该PCIe 4.0 IP可广泛应用于基于RISC-V内核的芯片定制、人工智能与机器学习、高性能计算、边缘计算

2025-08-14 10:24:03 24351

24351 Texas Instrument LMK04714-Q1双环时钟抖动清除器是一款高性能时钟调节器,支持JEDEC JESD204B/C,适用于航天应用。PLL2的每个14时钟输出均可配置为驱动七个

2025-08-08 15:05:57 843

843

(如医疗成像)三、TI替代方案1. DAC38J84(DDS+高速DAC)- 关键参数:- 1.5GSPS DAC,支持数字正交上变频- 可配置为DDS模式,支持相位连续跳频- JESD204B接口

2025-08-08 09:53:07

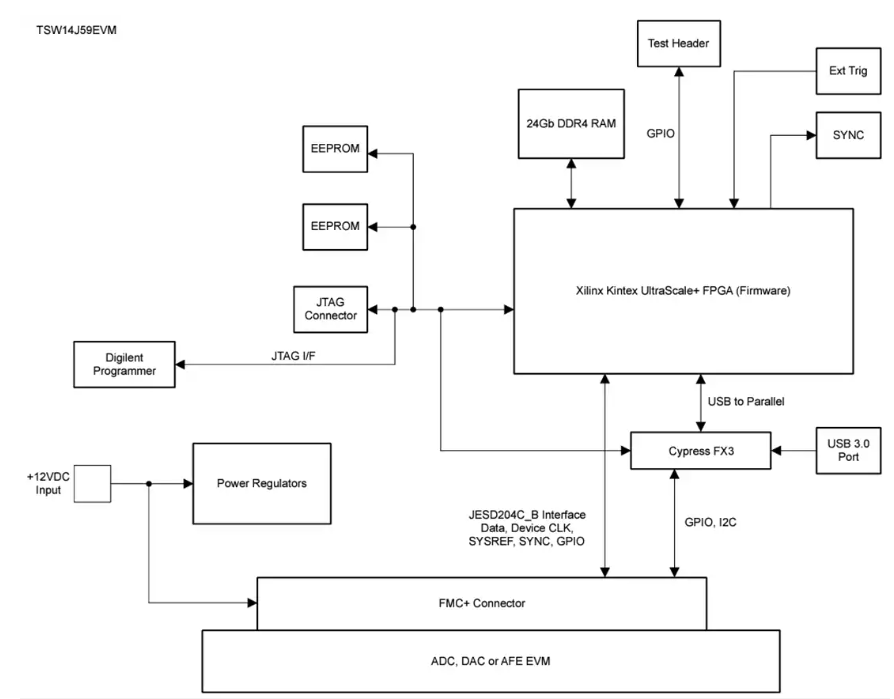

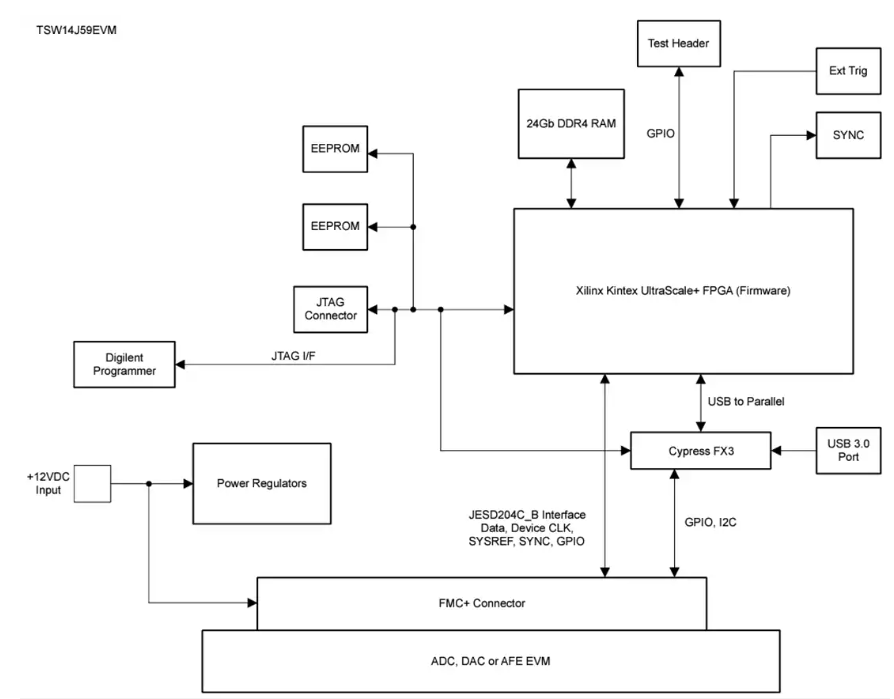

Texas Instruments TSW14J59EVM评估模块(evm)是下一代模式发生器和数据采集卡,用于评估TI JESD204C_B器件系列高速模数转换器(ADC)和数模转换器(DAC

2025-08-03 14:48:41 904

904

SE10F10B5.0UA系列ESD二极管产品数据手册

2025-07-13 14:48:34 1

1 会降低信噪比。四个高频时钟输出和具有较大分频器范围的额外LoICLK输出均与SYSREF输出时钟信号配对。用于JESD204B/C接口的SYSREF信号可以作为输入通过或内部生成,并重新计时到器件时钟

2025-07-06 17:35:48 668

668

和射频数模转换器 (DAC) 内核,支持多达八个基带通道。该器件集成有8通道、24.75Gbps JESD204C或15.5Gbps JESD204B数据接收器 (JRx) 端口、片上时钟倍频器和数

2025-06-27 14:50:33 798

798

本文介绍FPGA与高速ADC接口方式和标准以及JESD204与FPGA高速串行接口。

2025-06-12 14:18:21 2880

2880

时钟和脉冲对准。与IC处理基准和SYSREF信号配合使用时,它支持JESD204B和JESD204C子类1解决方案。

2025-06-06 14:32:57 780

780

实用JESD204B来自全球数据转换器市场份额领导 者的技术信息、提示和建议

2025-05-30 16:31:21 0

0 GN2104

集成CDR,适用于10G光模块

FCO-2L

155.52 MHz

LVPECL

高速ADC/DAC

ADI AD9208

14-bit, 3GSPS JESD204B接口

FCO-5L

2025-05-30 11:53:48

物理层的位置,一种是物理层在JESD204 IP里;另外一种是物理层在JESD204 IP外部,需要再配置JESD204 phy IP核进行使用。

2025-05-24 15:05:00 1827

1827

JESD204B标准接口,采样率可达数GHz,但实际数据速率往往需要通过抽取或内插技术进行调整。采样率与奈奎斯特准则

根据奈奎斯特采样定理,ADC采样率必须至少是信号最高频率的两倍。但在实际工程中,推荐采样率

2025-05-13 09:53:13

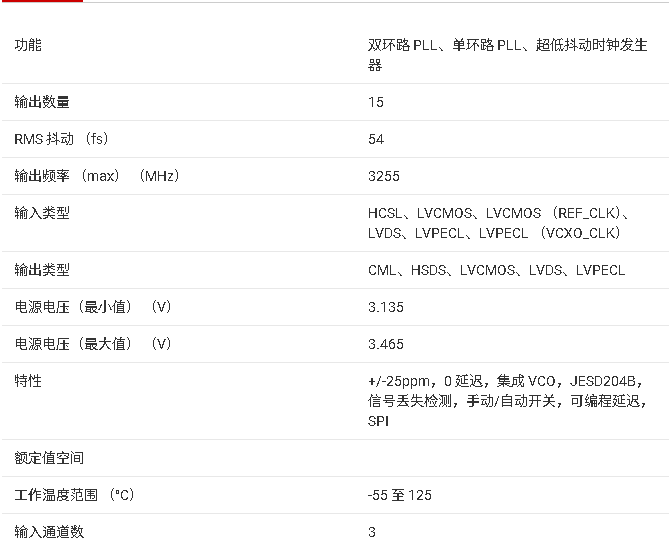

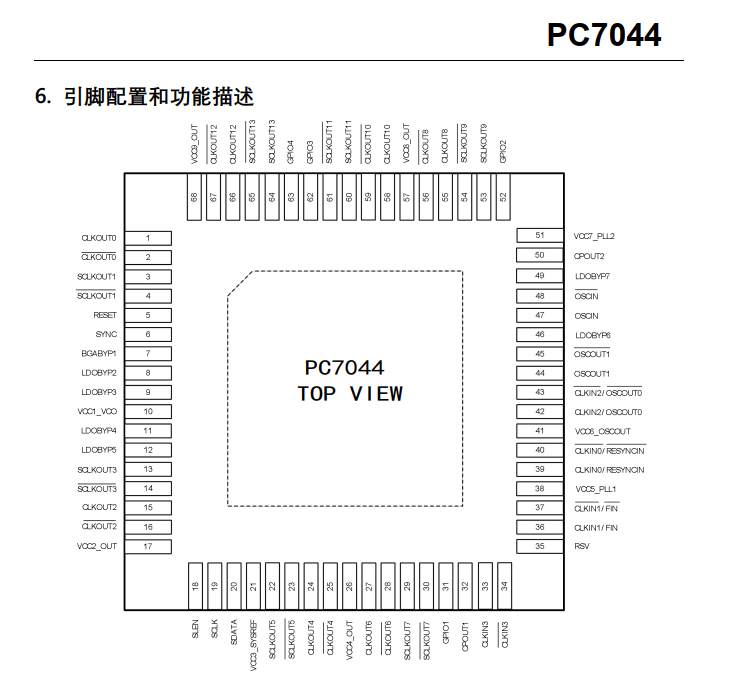

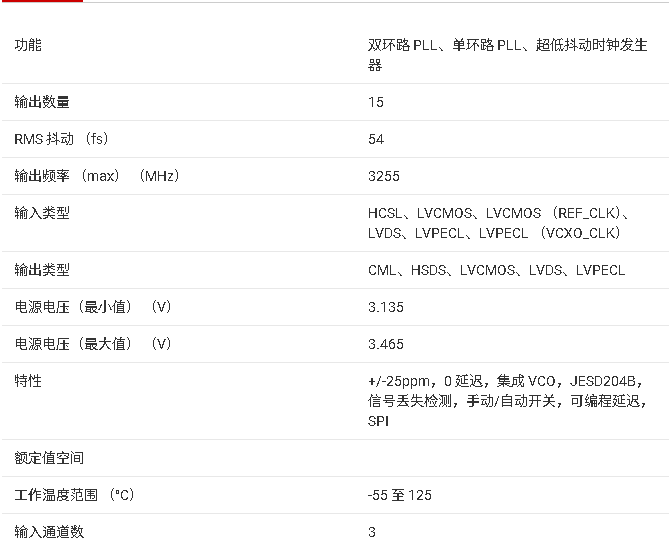

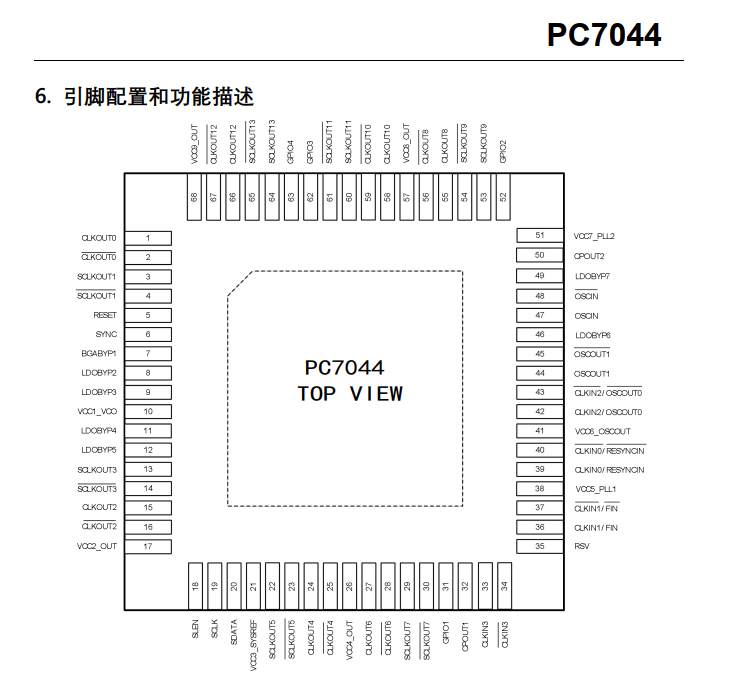

PC7044 是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B 型)接口的高速数据转换器执行参考时钟选择和超低噪声频率的生成。 PC7044 具有两个整数模式的 PLL

2025-05-09 17:59:30 4

4 1. 概述 PC7044 是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B 型)接口的高速数据转换器执行参考时钟选择和超低噪声频率的生成。 PC7044 具有两个整数

2025-05-08 16:01:36 655

655

1. 概述PC7044是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B型)接口的高速数据转换器执行参考时钟选择和超低噪声频率的生成。 PC7044具有两个整数

2025-05-08 15:57:20

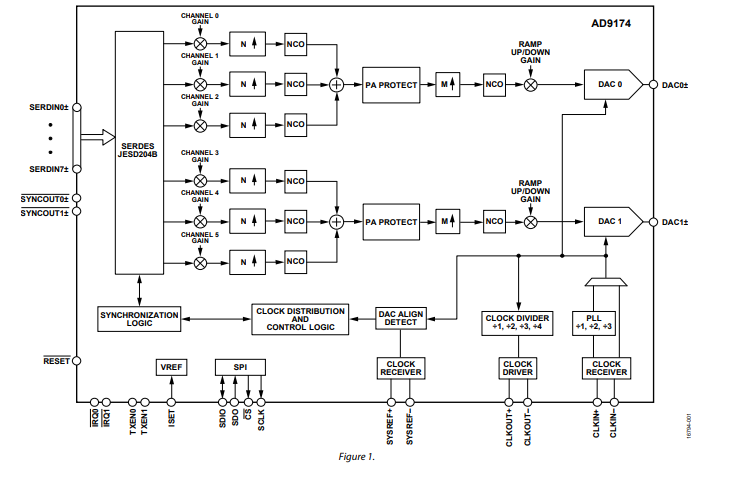

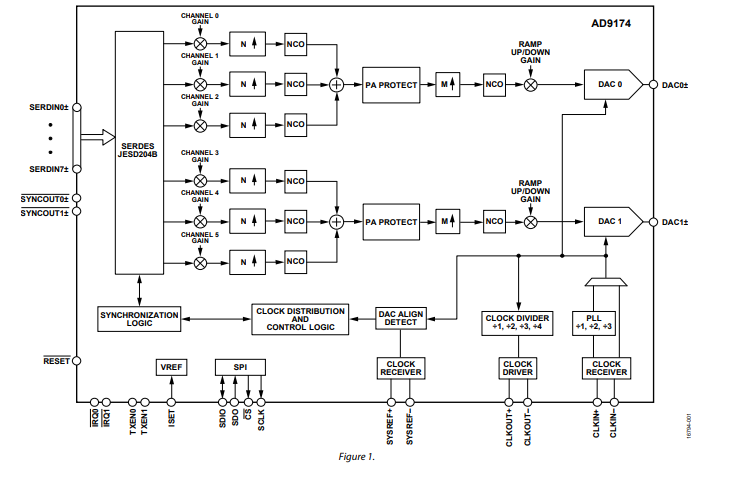

AD9174是一款高性能、双通道、16位数模转换器(DAC),支持高达12.6 GSPS的DAC采样速率。该器件具有8通道、15.4 Gbps JESD204B数据输入端口、高性能片内DAC时钟倍频器和数字信号处理功能,适合单频段和多频段直接至射频(RF)无线应用。

2025-04-30 15:42:42 1156

1156

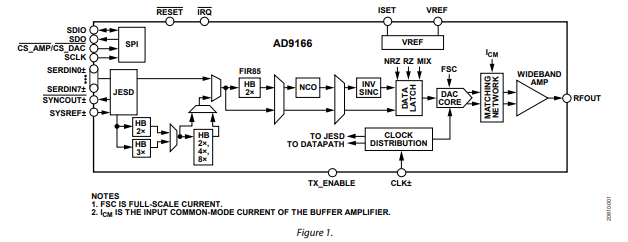

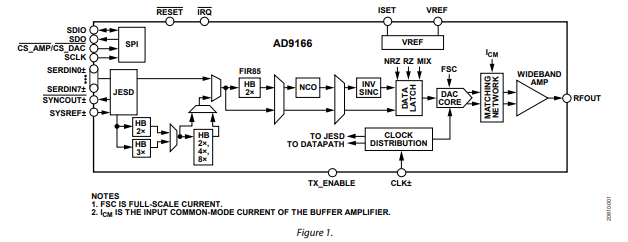

AD9166是高性能、宽带、片内矢量信号发生器,由高速 JESD204B 串行器/解串器(SERDES)接口、灵活的 16 位数字数据路径、正交 (IQ) 数模转换器 (DAC) 内核以及一个集成的差分至单端输出缓冲放大器组成 ,可匹配高达 10 GHz 的 50 Ω 负载。

2025-04-30 15:33:03 1200

1200

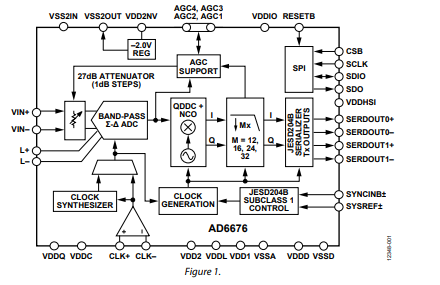

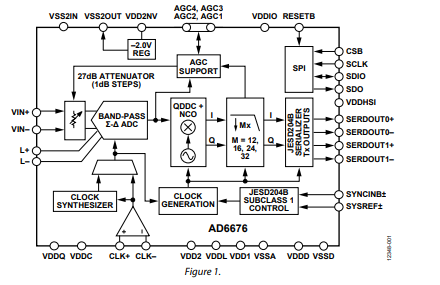

MSPS至266.7 MSPS范围内便于管理的速率。 16位复数输出数据通过单通道或双通道JESD204B接口传输至主机,支持的线路速率高达5.333 Gbps。

2025-04-28 11:01:36 855

855

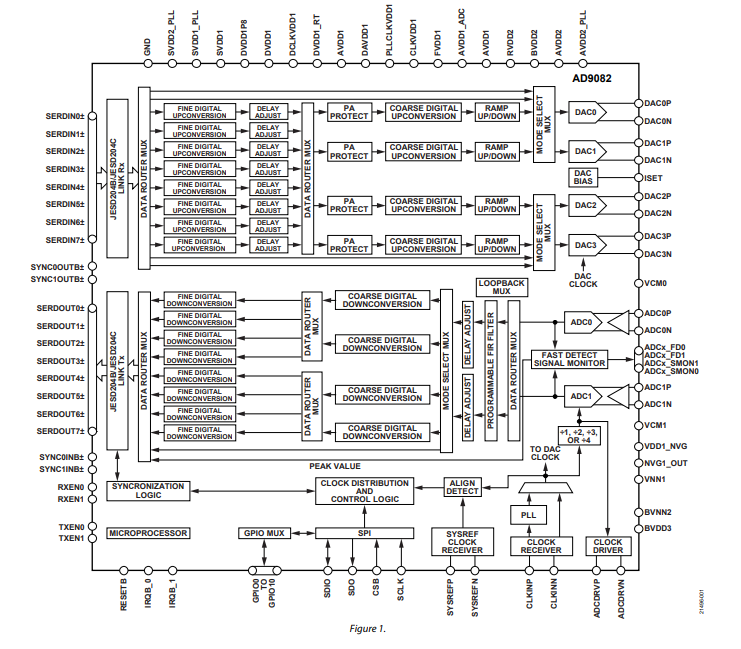

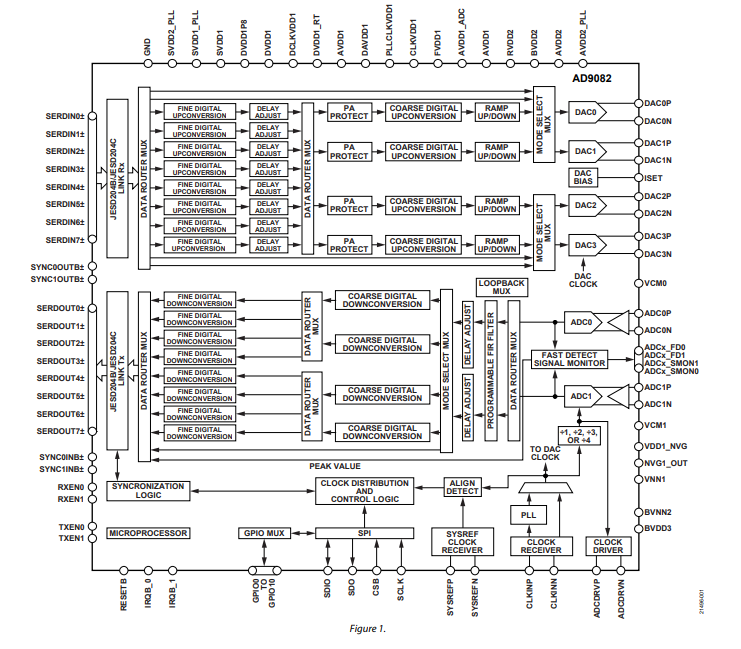

JESD204B数据收发器端口、片内时钟倍频器和数字信号处理(DSP)功能,适合宽带或多频段直接至RF应用。AD9082还具有旁路模式,允许ADC和/或DAC内核的全宽带功能旁路DSP数据路径。此器件还具有低延迟回送和跳频模式,适用于相控阵雷达系统和电子战应用。

2025-04-28 09:51:06 1123

1123

Gbps/通道 JESD204B 标准。该套件还具有片内时钟乘法器,以及直接针对 RF 应用的宽带或多频带数字信号处理(DSP)功能。可以绕过 DSP 数据路径,以允许转换器内核与 JESD204

2025-04-28 09:44:03 1128

1128

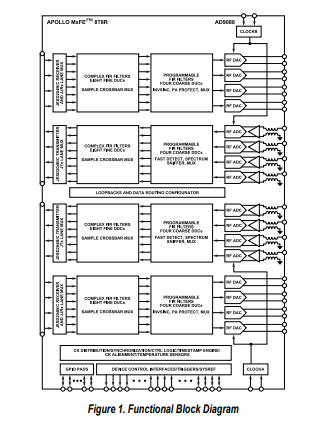

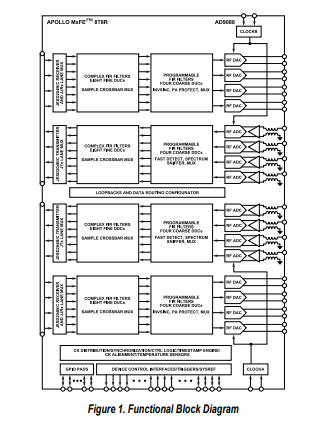

JESD204C 或 20 Gbps JESD204B 数据收发器端口、一个片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9088 还具有旁路模式,允许 ADC

2025-04-28 09:35:17 893

893

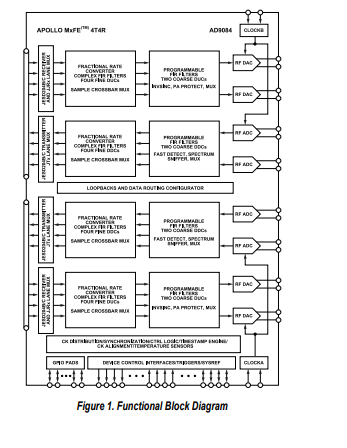

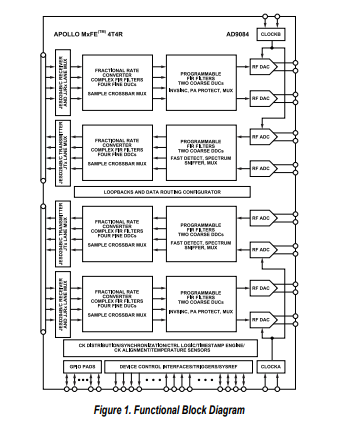

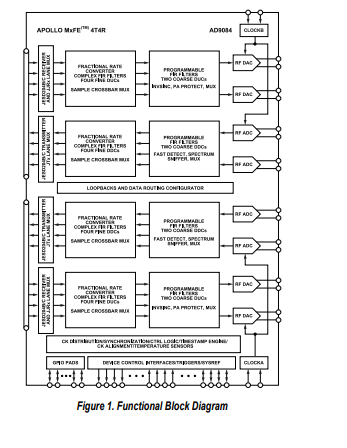

Gbps JESD204C 或 20 Gbps JESD204B数据收发器端口、片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9084 还具有旁路模式,允许

2025-04-28 09:32:20 1365

1365

JESD204B是逻辑器件和高速ADC/DAC通信的一个串行接口协议,在此之前,ADC/DAC与逻辑器件交互的接口大致分为如下几种。

2025-04-24 15:18:36 4479

4479

的应用。该套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 数据接收器 (JRx) 端口、片内时钟乘法器和数字信号处理 (DSP) 数据通路,能够处理

2025-04-18 17:22:55 1026

1026

JESD204C 或 20 Gbps JESD204B 数据收发器端口、一个片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9088 还具有旁路模式,允许 ADC

2025-04-18 15:58:18 1055

1055

JESD204C 或 20 Gbps JESD204B数据收发器端口、片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9084 还具有旁路模式,允许 ADC

2025-04-18 15:47:45 1770

1770

LTC6953 是一款高性能、超低抖动的 JESD204B/JESD204C 时钟分配 IC。LTC6953 的 11 个输出可配置为最多 5 个 JESD204B/JESD204

2025-04-16 14:28:18 1023

1023

HMC7044B 是 [HMC7044]的修订版本,是一款高性能、双环路、整数 N 抖动衰减器,能够为具有并行或串行(JESD204B 和 JESD204C 类型)接口的高速数据转换器执行参考选

2025-04-16 11:27:05 1622

1622

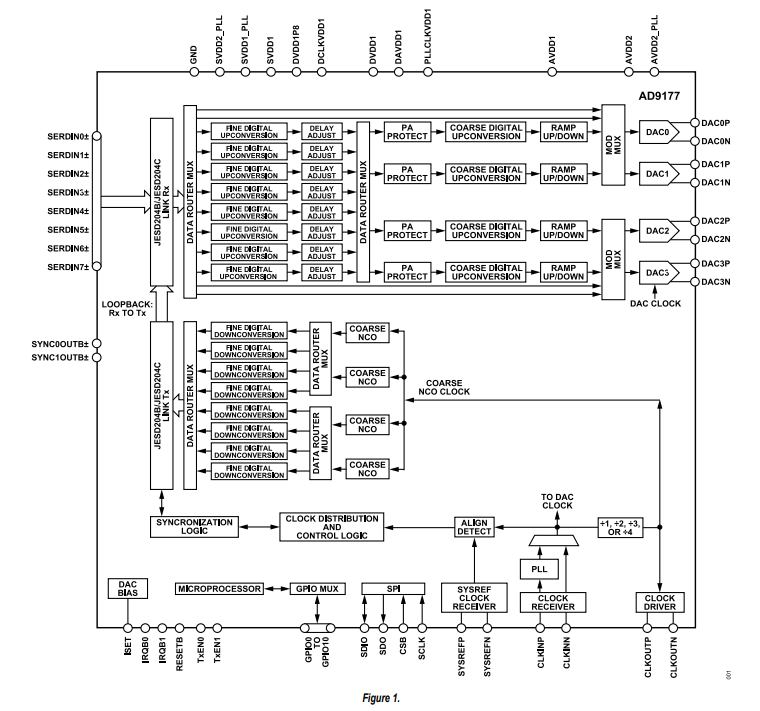

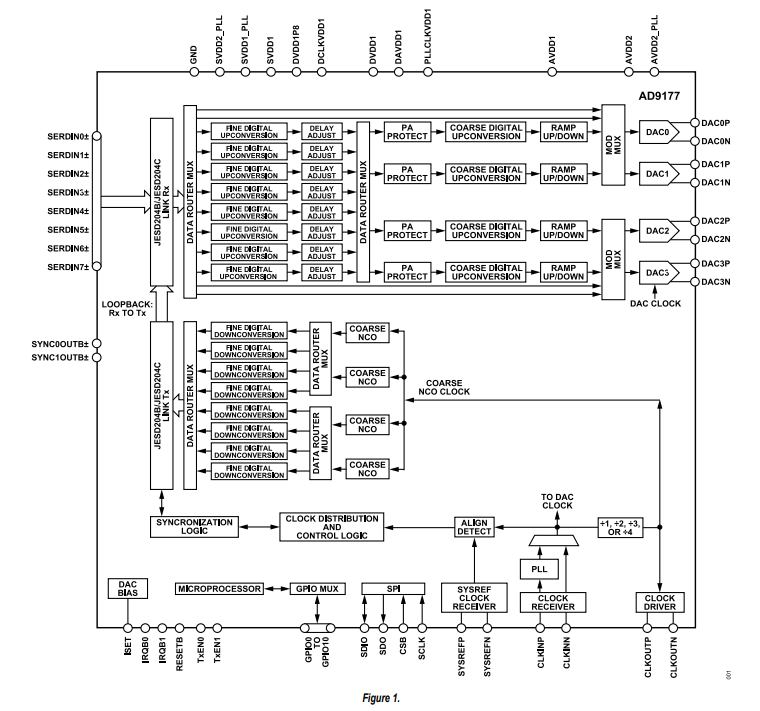

通过MICROBALZE配置AD9177,数据率9.6GSPS

输入300MHz参考时钟,内部倍频至9.6GHz作为采样时钟,显示PLL已锁定

JESD204C 8个lane无法正常校验成功,此时线速率是19.8Gbps;将其配置为9.9Gbps后lane正常

2025-04-15 07:09:14

AD采集芯片为AD9680-1000,时钟芯片为AD9528。当 AD 采样时钟为 500MHz 时,jesd204B (串行线速 = 5 Gbps) 稳定。但是,当 AD 采样时钟为 800MHz

2025-04-15 06:43:11

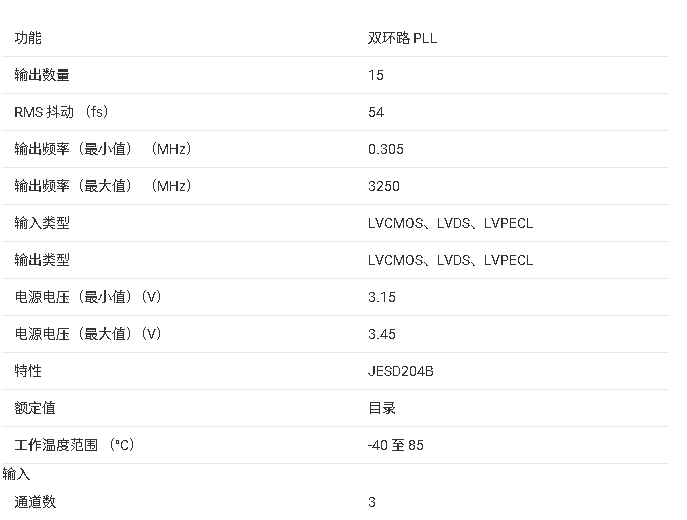

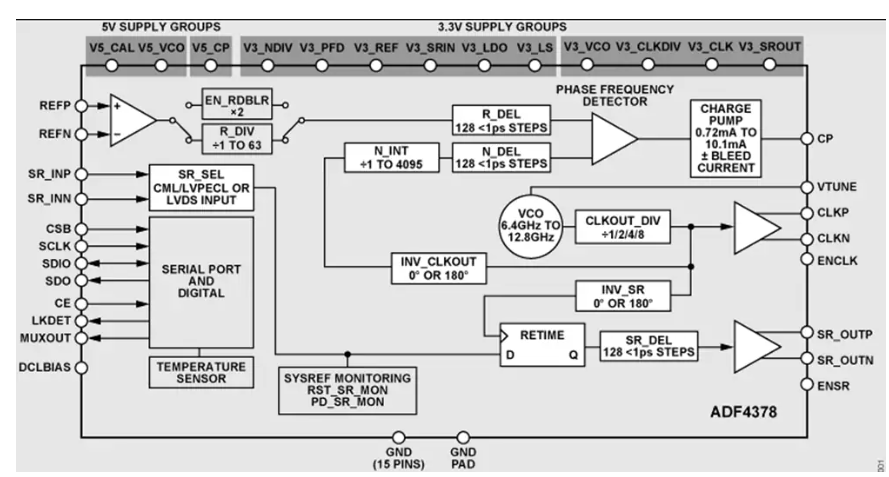

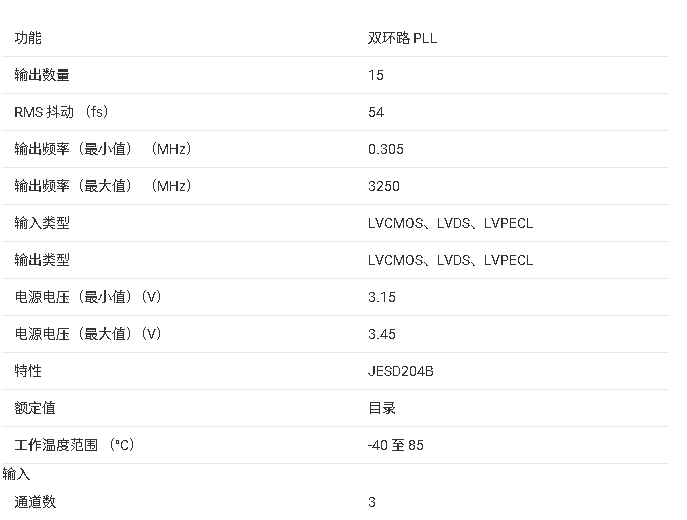

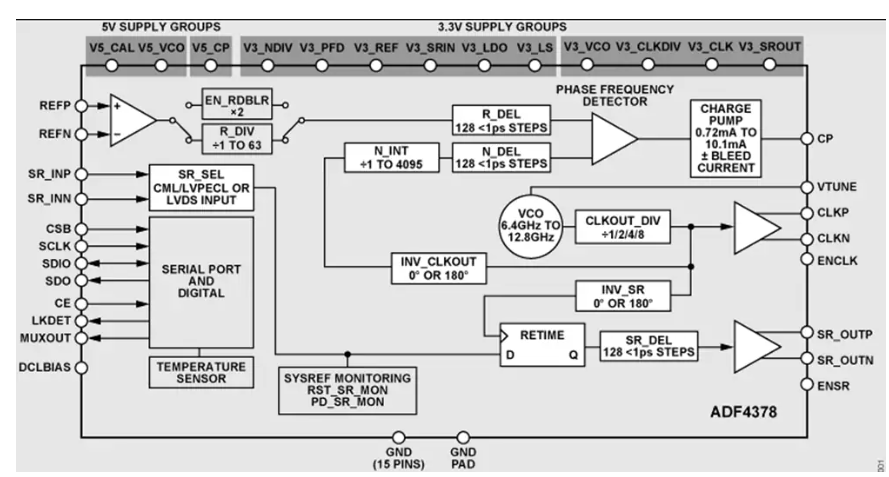

AD9528是一款双级PLL,集成JESD204B/JESD204C SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理

2025-04-10 10:19:13 1141

1141

(BTS)系统中的许多不同器件接口,如数据转换器、本振、发射/接收模块、现场可编程门阵列(FPGA)和数字前端ASIC等。 HMC7043可生成符合JESD204B接口要求的多达7个DCLK和SYSREF时钟对。

2025-04-10 09:38:59 1226

1226

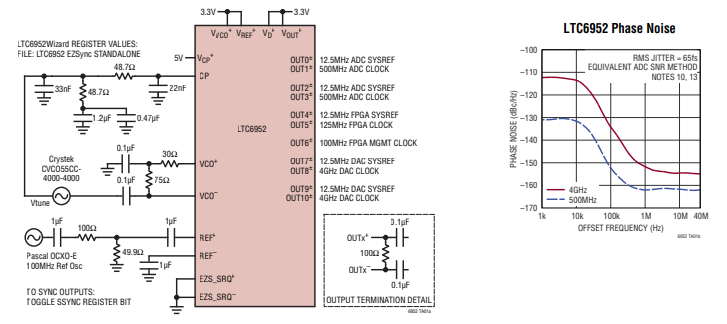

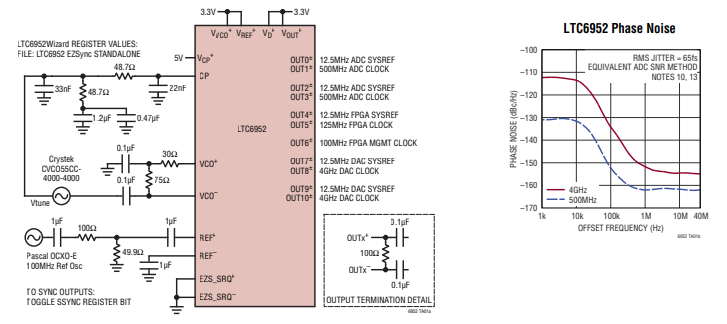

LTC6952 是一款高性能、超低抖动 JESD204B/C 时钟生成和分配 IC。该器件包括一个锁相环 (PLL) 内核,由基准分频器、具有锁相指示器的相位频率检波器 (PFD)、超低噪声充电

2025-04-09 17:26:48 830

830

电子发烧友网站提供《ESD5B5CU SOD-523塑料封装ESD保护二极管规格书.pdf》资料免费下载

2025-03-13 16:33:31 1

1 电子发烧友网站提供《ESD5B5CM SOD-523塑料封装ESD保护二极管规格书.pdf》资料免费下载

2025-03-13 16:31:37 0

0 电子发烧友网站提供《ESD5B5CL SOD-523塑料封装ESD保护二极管规格书.pdf》资料免费下载

2025-03-13 16:29:50 0

0 电子发烧友网站提供《ESD5B3CM SOD-523塑料封装ESD保护二极管规格书.pdf》资料免费下载

2025-03-13 16:23:56 0

0 电子发烧友网站提供《ESD3B3CM SOD-323塑料封装ESD保护二极管规格书.pdf》资料免费下载

2025-03-13 16:15:01 0

0 电子发烧友网站提供《ESD3B5CM SOD-323塑料封装ESD保护二极管规格书.pdf》资料免费下载

2025-03-13 16:06:16 0

0 /Theonesssssssss/Documents/VivadoData/project_1/project_1.srcs/sources_1/new/jesd204b_base.v\":159]

* [Synth

2025-03-12 22:21:51

在追求更快、更稳的无线通信路上,传统射频架构深陷带宽-功耗-成本的“不可能三角”: 带宽每翻倍,系统复杂度与功耗增幅远超线性增长 。传统方案通过“分立式功放+多级变频链路+JESD204B 接口

2025-03-12 17:57:31 1150

1150

随着高速AD/DA接口在数字接口中越来越广泛的运用,204B协议作为重要的通讯协议,目前已经发挥出越来越重要的作用。

2025-03-07 13:43:25 1110

1110

地,只要导电部分(体表皮肤、ESD脚垫、设备机壳、操作部件等)是等势的,ESD(泄放电荷)就不会发生,大地很适合作基准电压,如果你确认所有导电部分都连到地,那么就保证了这些导电部分均处于相同的电位,一旦

2025-03-03 16:42:36

其实使用到ADI的东西,基本也就没有太去关注协议这些东西,只是简简单单的有个了解就行,在实际调试的时候,用的也是Xilinx的评估版的JESD的IP,基本不需要自己做什么工作就能够把整个系统运行起来了。

2025-02-08 13:45:55 3989

3989

请问各位大侠:JESD204B专用于ADC/DAC和FPGA或ASIC的接口吗,该接口同Rapid/PCIe的物理层Serdes接口有何区别,谢谢!

2025-02-08 09:10:29

谁可以帮忙解释下在ADC对应不同的通道数以及分辨率时,各种接口形式所需要的引脚数是如何计算出的?

2025-02-06 06:52:05

Hi~,我想请问一下204B接口的各个层次,例如transport layer,link layer...里面的8B/10B,scrambler...的内建测试模式和测试模板(test parten)方面的资料,应该参考什么呢?

2025-01-20 09:05:37

大家好,近来接触JESD204B接口协议,采用SUBCLASS1方案,在系统设计上遇到诸多问题。首先SYSREF和DEVICE CLK 一般有不同的电气特性,一个可能是TTL的,另一个是CML

2025-01-10 07:25:47

最近在使用JESD204B协议,遇到一下问题。我使用的是FPGA与DAC38J84。

1:有关SYSREF时钟问题,DAC的时钟为1.2GHz, FPGA中JESD204B IP核配置为发射

2025-01-06 08:08:15

JESD204B Setting Value

Line Rate : 1500Mbps

SYSREF : 7.5M

DACCLK : 1200M

LMFK :L=8, M=4, F=1, S=1, K

2025-01-06 06:36:56

电子发烧友App

电子发烧友App

评论