来源:数字积木

概述

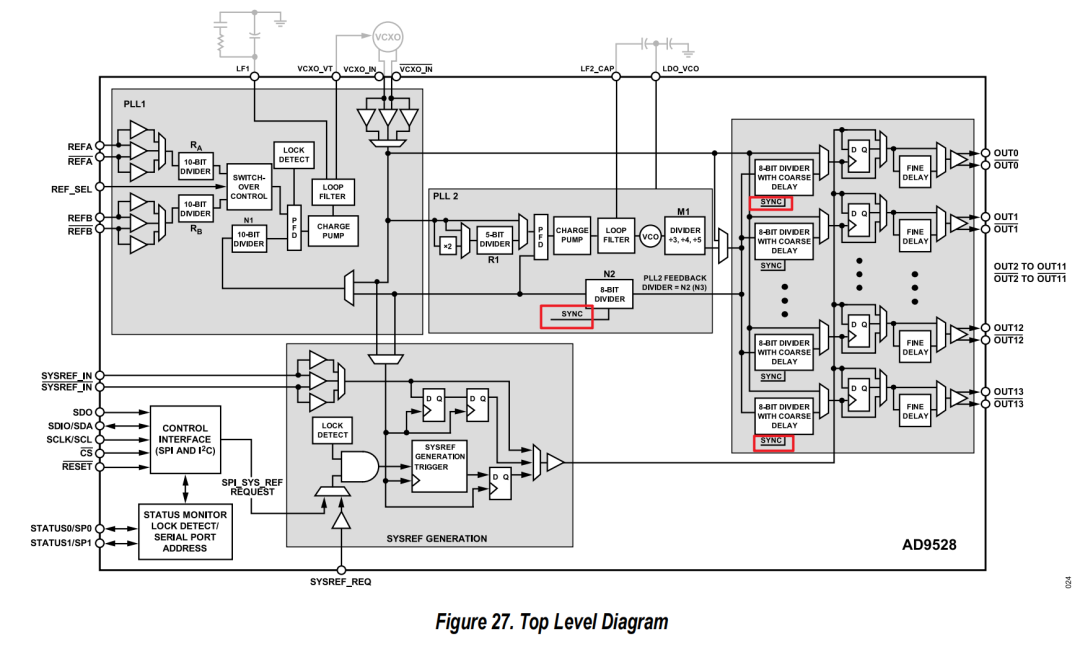

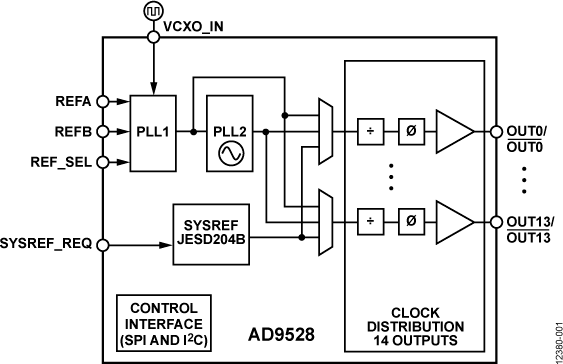

AD9528是一款双级PLL,集成JESD204B SYSREF发生器,可用于多器件同步。

AD9528产生最高频率为1.25 GHz的六路输出(输出0至输出3、输出12和输出13),以及最大频率高达1 GHz的八路输出。每一路输出均可配置为直接从PLL1、PLL2或内部SYSREF发生器输出。14路输出通道的每一路都包含一个带数字相位粗调功能的分频器,以及一个模拟微调相位延迟模块,允许全部14路输出具有时序对齐的高度灵活性。AD9528还可用作灵活的双通道输入缓冲器,以便实现14路器件时钟和/或SYSREF信号的分配。启动时,AD9528直接向输出12和输出13发送VCXO信号,用作启动就绪时钟。

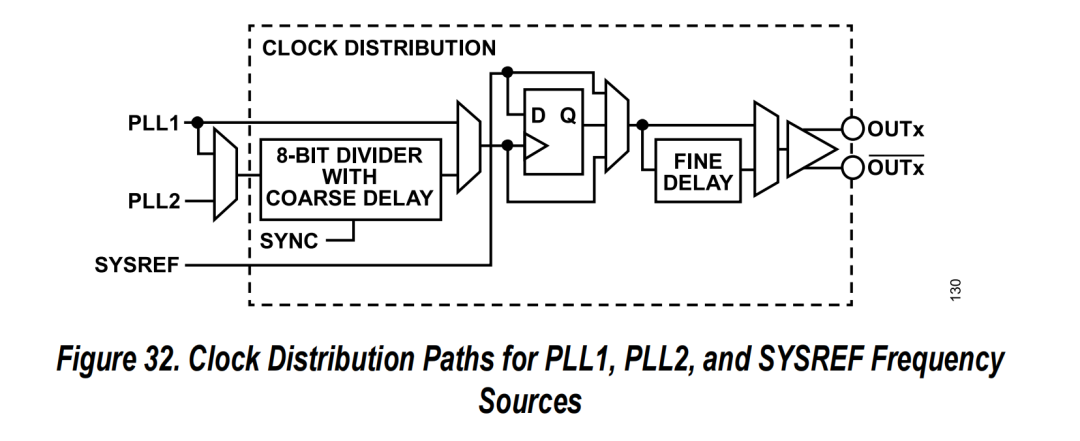

时钟分配器由14个独立通道(OUT0到OUT13)组成。每个通道输出的输入频率源可选择为PLL1输出、PLL2输出或SYSREF。如图32所示,每个输出通道还包括一个专用8位分频器、两个专用相位延迟元件和一个输出驱动器。

以下是根据通道配置的不同而产生的各种通道限制:

所有通道均支持模拟精细延迟,与所选输入频率源无关

仅当使用通道分频器时,才支持数字粗延迟。当SYSREF用作频率源时,必须通过通道分频器的输出对信号进行重新计时,才能使用数字粗延迟

输出通道同步通过寄存器 0x032A 第0位的输出信号来同步复位8位通道分频器来实现。因此,必须使用8位分频器路径来支持同步。如果SYSREF是输出的频率源,则必须由通道分频器的输出时钟对SYSREF信号进行重采样以实现同步。

时钟分频

输出时钟分布分频器被称作D0到D13,分别对应于输出通道OUT0至OUT13。每个分频器均可编程设置,精度为8位,相当于1到256之间的任意数值。分频器的占空比校正设置为提供标称50%的占空比,即使进行奇数分频也是如此。请注意,在更改分频值后必须发出同步输出命令,以确保在通道输出处产生预期的分频比的时钟。

数字粗延迟

AD9528芯片支持通过已 VCXO分频器输出频率的半周期为增量,实现0到63个步进(6位)的可编程相位偏移。

需要注意的是,在完成新相位偏移值的编程后,必须发出同步输出指令才能确保目标相位偏移值准确出现在通道输出端。具体操作流程是:先编程设定新相位偏移值,再通过寄存器0x032A的第0位发送同步指令。在同步指令激活期间,所有输出功能将暂时禁用,除非通道被设置为忽略同步指令。各通道的同步忽略控制则由寄存器0x032B和寄存器0x032C共同控制。

模拟精密延迟

每个通道均配备一个4位精密模拟延迟模块,其延迟步长显著小于 VCXO分频器输出频率的半周期。当四个延迟位均为0000时,各通道的精密模拟延迟使能位将激活微调延迟路径,此时最小插入延迟约为425皮秒。若将所有延迟位设为1111,则会额外增加496皮秒的延迟量。该精密延迟模块的平均分辨率步长约为31皮秒。

输出通道断电

每个输出通道通过寄存器0x0501和寄存器0x0502进行独立的断电控制。当每个通道被断电时,设备总功率随之降低,保持输出静止,直到用户准备禁用该通道的断电控制。此外,寄存器0x0503和寄存器0x0504还通过LDO断电控制为每个通道输出提供额外的节能功能。

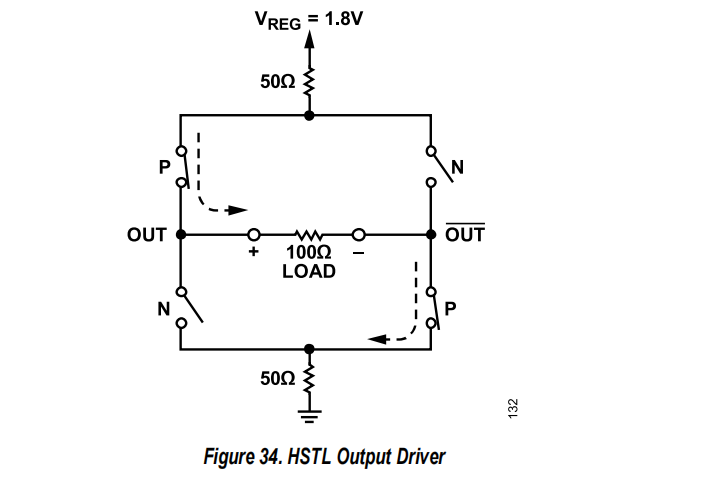

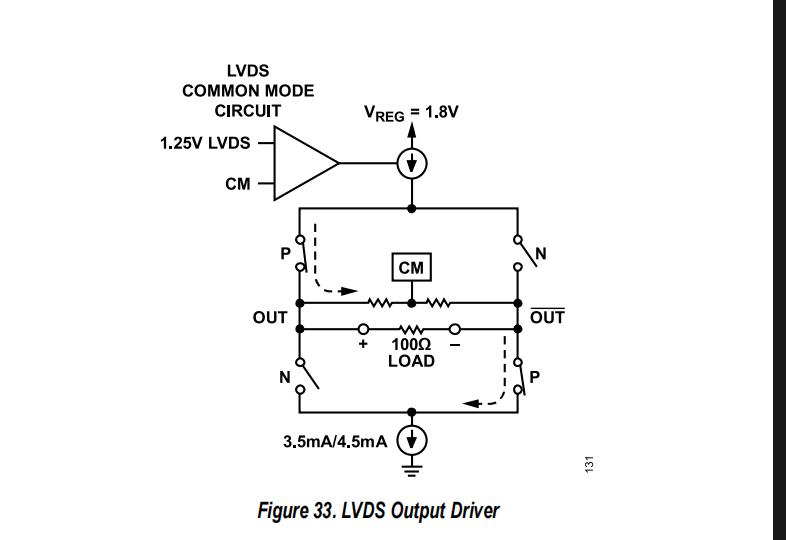

输出驱动

每个通道及其对应的输出驱动器都配备专用内部低压差稳压器(LDO),可同时为通道和驱动器供电。等效的输出驱动电路设计如图33和图34所示。该设计支持通用外部100 Ω差分电阻,适用于HSTL和LVDS两种驱动模式。在LVDS模式下,3.5 mA电流会在100 Ω负载电阻上产生350 mV峰值电压;LVDS升压模式下,4.5 mA电流则会在同一电阻上形成450 mV峰值电压。同理,在HSTL模式中,9 mA电流同样会在100 Ω负载电阻上产生900 mV峰值电压。

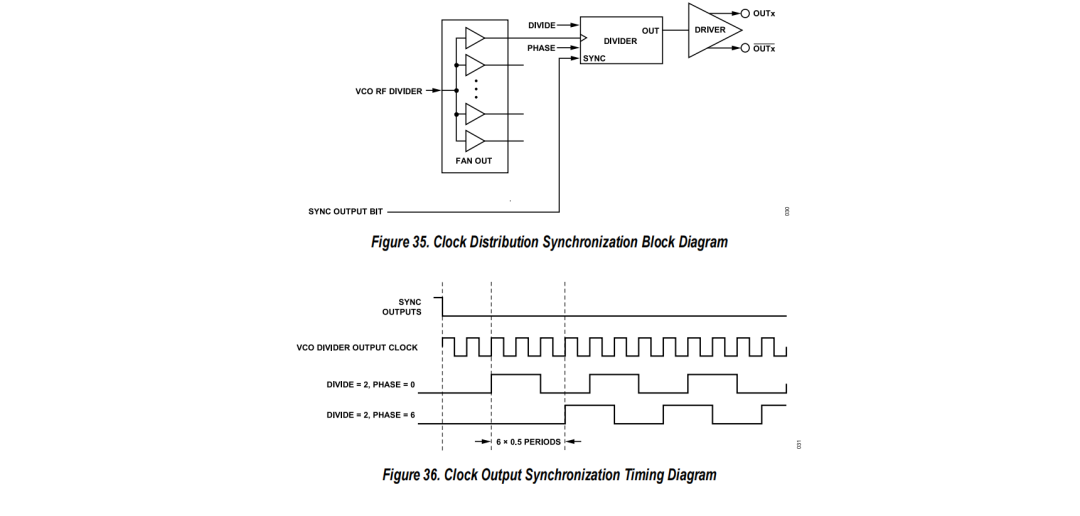

时钟分配同步

图35展示了时钟分配同步功能的框图。同步功能通过边沿对齐技术实现所有输出信号的同步,或在输出边沿之间施加所需的相位偏移。当锁相环2(PLL2)首次在上电或复位后完成锁定时,系统会自动启动通道分频器的同步机制。后续的锁定与解锁操作不会触发重新同步,除非设备处于断电或复位状态。

当寄存器0x032A第0位的同步输出位处于激活状态时,所有输出将被暂时禁用,除非通道被编程为忽略同步输出命令。每个通道对同步命令的忽略控制由寄存器0x032B和寄存器0x032C控制。

使用同步输出位同步输出时,应首先设置该位,然后将其清除。同步事件是清除操作(即该位的逻辑1到逻辑0的转换)。当PLL2就绪时,通道分频器彼此自动同步 。

在正常工作状态下,通道的相位偏移参数会在AD9528开始输出信号前,通过SPI/I2C接口完成预设。虽然分频器运行时无法调整数字粗相位偏移量,但无需关闭PLL1和PLL2即可实现所有输出信号间的相对相位调节。具体操作是:首先通过时钟分配寄存器的[5:0]位设置新相位偏移参数,随后利用同步输出寄存器(寄存器0x032A的第0位)发出输出同步指令。

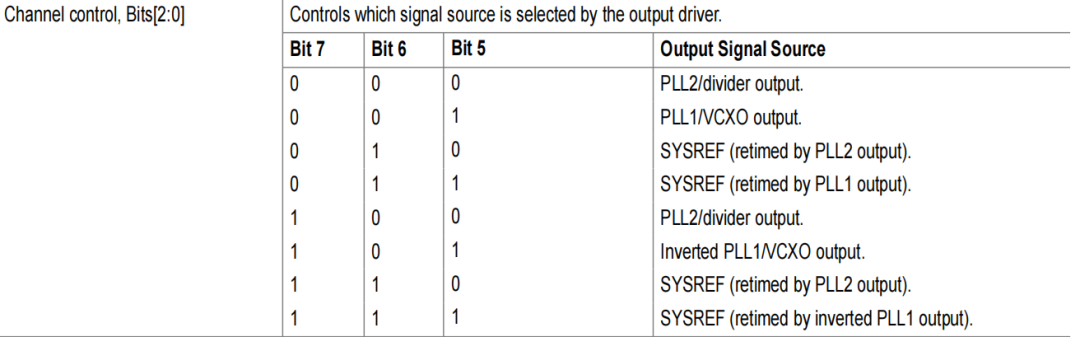

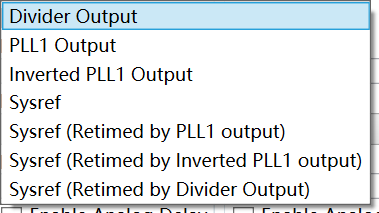

通道输出选择

输出通道寄存器控制如下表:

有效的配置输出如下列表:

配置SYSREF输出重定时时钟时,对重定时时钟的选择一般遵循如下原则,原则的重定时的时钟和对应输出通道的选择时钟源一致。如对应时钟通道的时钟源为PLL1(VCXO)输出,则SYSREF输出重定时时钟同样选择为PLL1(VCXO)输出 。

注意 : 配置为SYSREF输出时 , SYSREF输出信号跳过时钟重采样 ,需要在 0X032D-0X032E 寄存器中,将对应通道的 SYSREF 重采样设置为bypassed (跳过)模式。一般不使用该模式。

-

发生器

+关注

关注

4文章

1423浏览量

64405 -

pll

+关注

关注

6文章

976浏览量

137580 -

时钟

+关注

关注

11文章

1953浏览量

134539 -

ad9528

+关注

关注

1文章

5浏览量

2958

原文标题:AD9528的时钟分布特性

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

请问AD9528芯片IIC无法寻址到是什么问题

AD9528锁相环芯片无输出

ad9528上电后out13没有输出vcxo频率

AD9528是什么?有何特点

LED光源光强空间分布特性的快速测试

JESD204B时钟发生器14输出ad9528数据表LVDS技术

AD9528 提供14路LVDS/HSTL输出的JESD204B时钟发生器

AD9528:具有14个LVDS/HSTL输出的JESD204B时钟发生器数据表

AD9528提供14路LVDS/HSTL输出的JESD204B/JESD204C时钟发生器技术手册

AD9528双级PLL的时钟分布特性

AD9528双级PLL的时钟分布特性

评论