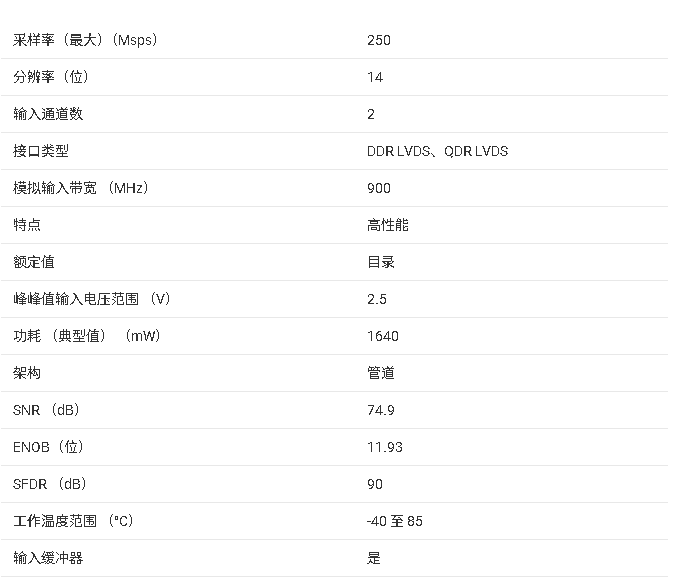

ADS42JB69和ADS42JB49是高线性度、双通道、16位和14位、250MSPS、模数转换器(ADC)。这些器件支持数据速率高达

3.125 Gbps 的JESD204B串行接口。缓冲模拟输入在很宽的频率范围内提供均匀的输入阻抗,同时最大限度地减少采样保持毛刺能量,从而可以轻松地将模拟输入驱动到非常高的输入频率。采样时钟分频器为系统时钟架构设计提供了更大的灵活性。这些器件采用内部抖动算法,在较大的输入频率范围内提供出色的无杂散动态范围 (SFDR)。

*附件:ads42jb69.pdf

特性

- 双通道ADC

- 14 位和 16 位分辨率

- 最大时钟速率:250 MSPS

- JESD204B串行接口

- 符合 0、1、2 子类标准

- 高达 3.125 Gbps

- 支持双通道和四通道

- 具有高阻抗输入的模拟输入缓冲器

- 灵活的输入时钟缓冲器:

1分频、-2和-4分频 - 差分满量程输入:2 V

聚丙烯和 2.5 V聚丙烯

(寄存器可编程) - 封装:9 毫米× 9 毫米 VQFN-64

- 功耗:850 mW/通道

- 孔径抖动:85 f

S均方根 - 内部抖动

- 信道隔离度:100 dB

- 性能:

- f

在= 170 MHz(2 V时)聚丙烯, –1 dBFS- 信噪比:73.3 dBFS

- SFDR:HD2、HD3 为 93 dBc

- SFDR:非 HD2、HD3 为 100 dBc

- f

在= 170 MHz(2.5 V时)聚丙烯, –1 dBFS- 信噪比:74.7 dBFS

- SFDR:HD2、HD3 为 89 dBc,

非 HD2、HD3 为 95 dBc

- f

参数

方框图

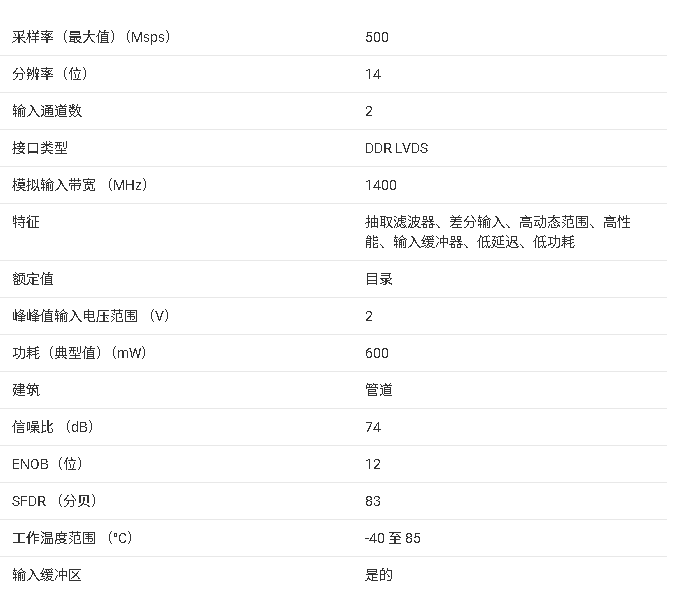

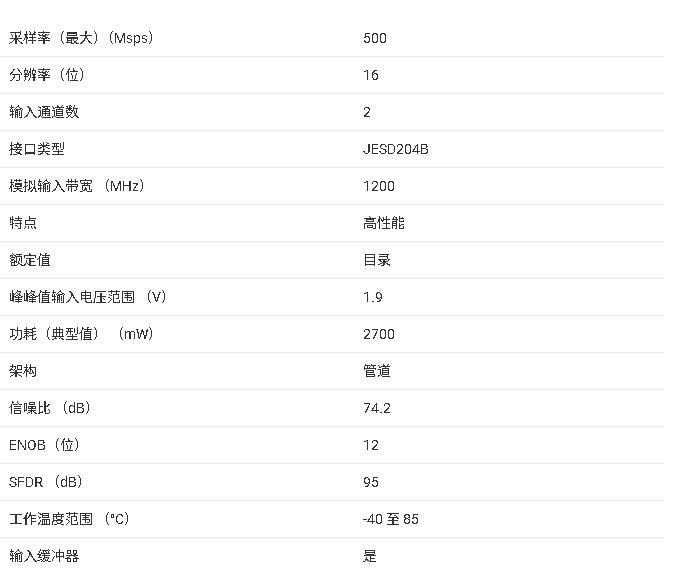

ADS42JBx9 系列是双通道高速模数转换器(ADC)家族,包含 14 位(ADS42JB49)与 16 位(ADS42JB69)分辨率型号,最高采样率 250 MSPS,支持 JESD204B 串行接口,具备高线性度与低抖动特性,专为通信基础设施、雷达、测试测量等高精度高频场景设计。

核心参数与性能

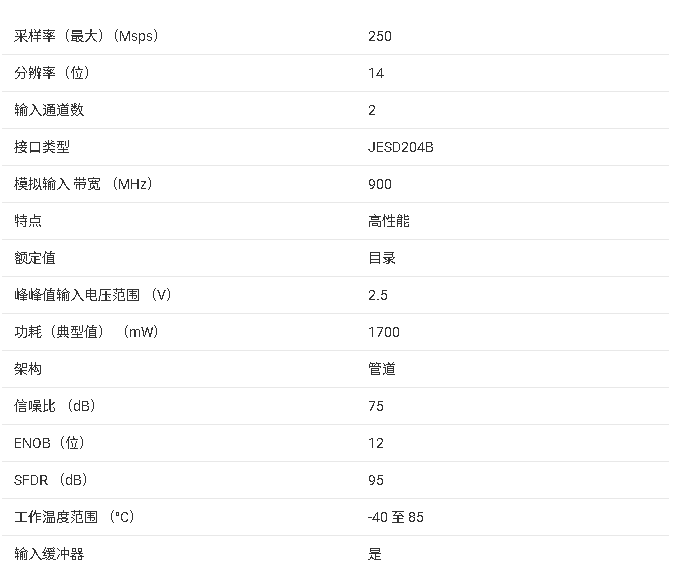

- 分辨率与采样率 :ADS42JB49(14 位)、ADS42JB69(16 位);最高采样率 250 MSPS,时钟输入支持 10 MHz-1 GHz,内置 1/2/4 分频器,适配灵活系统时钟架构。

- 动态性能 :170 MHz 输入、2 VPP 量程下,SNR 分别为 73.3 dBFS(ADS42JB69)、72.8 dBFS(ADS42JB49);SFDR≥89 dBc(谐波)、≥95 dBc(非谐波),孔径抖动仅 85 fs rms,通道隔离度 100 dB。

- 输入与输出 :差分模拟输入量程可编程(2 VPP/2.5 VPP),输入带宽 900 MHz;JESD204B 接口支持 2/4 通道,最高数据率 3.125 Gbps,兼容子类 0/1/2,输出 CML 逻辑电平。

- 功耗与工作条件 :模拟电源(AVDD)1.7 V-1.9 V、模拟缓冲电源(AVDD3V)3.15 V-3.45 V,数字电源(DRVDD/IOVDD)1.7 V-1.9 V;单通道功耗 850 mW,全局掉电模式功耗 160 mW,工作温度 - 40°C 至 + 85°C。

封装与引脚

- 采用 9 mm×9 mm 64 引脚 VQFN(RGC)封装,含裸露热焊盘(需焊接至 PCB 接地平面优化散热)。

- 关键引脚包括差分模拟输入(INAP/INAM、INBP/INBM)、差分时钟输入(CLKINP/CLKINM)、JESD204B 输出引脚(DA [1:0] P/M、DB [1:0] P/M)、串行配置接口(SCLK/SDATA/SEN/SDOUT)及同步控制(SYNC~/SYSREF)引脚。

核心功能与特性

- 灵活接口与同步 :JESD204B 接口支持 2/4 通道配置,支持码组同步(CGS)与初始通道对齐(ILA);SYSREF/SYNC~ 引脚实现多器件精准同步,适配子类 1(SYSREF)与子类 2(SYNC~)同步模式。

- 增益与过载控制 :数字增益可编程(-2 dB 至 6 dB,0.5 dB 步进),量程随增益比例调整;支持正常(14 时钟周期)与快速(9 时钟周期)过载指示,阈值可编程,通过 OVRA/OVRB 引脚输出。

- 低噪声与测试模式 :内置抖动算法优化 SFDR,模拟输入缓冲器隔离采样噪声;支持多种测试模式(伪随机码、斜坡、自定义 Pattern 等),可通过寄存器配置验证数据完整性。

典型应用场景

- 通信与有线电视基础设施、多载波蜂窝接收机、雷达与智能天线阵列、宽带无线系统、测试测量仪器、软件定义无线电、功率放大器线性化系统。

设计要点

- 电源与去耦 :模拟电源(AVDD/AVDD3V)与数字电源(DRVDD/IOVDD)需独立供电,就近配置去耦电容,建议通过 LDO 稳压,减少噪声耦合。

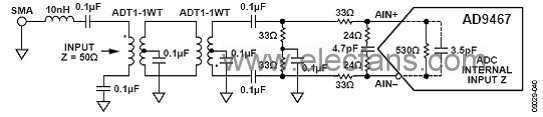

- 输入与时钟设计 :模拟输入推荐差分驱动,串联 5 Ω-10 Ω 电阻抑制寄生振荡,高频场景(>250 MHz)采用背靠背变压器优化谐波性能;时钟输入优先差分驱动(LVPECL/LVDS),严格控制抖动,推荐使用低抖动时钟源(如 LMK04828)。

- 布局规范 :差分信号线长度匹配(误差≤2 mil),模拟地与数字地分离且不重叠;热焊盘充分覆铜并通过过孔接地,JESD204B 高速走线尽量短直,避免锐角弯折。

- 配置要点 :上电后需通过 RESET 引脚硬件复位(最小 10 ns 低脉冲);通过 SPI 接口配置增益、JESD204B 模式、过载阈值等参数,未使用引脚需按规格连接(如 SEN 上拉、RESET 下拉)。

产品型号与供货

- 在售型号包括卷盘装(2000 片 / 卷:ADS42JB49IRGCR、ADS42JB69IRGCR)与小卷盘装(250 片 / 卷:ADS42JB49IRGCT、ADS42JB69IRGCT),符合 RoHS 标准,MSL 等级 3(260°C 回流焊,168 小时湿度敏感)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

adc

+关注

关注

100文章

7946浏览量

556883 -

分频器

+关注

关注

43文章

537浏览量

53742 -

串行接口

+关注

关注

3文章

523浏览量

45330 -

模数转换器

+关注

关注

26文章

4104浏览量

130262 -

数据速率

+关注

关注

0文章

60浏览量

12313

发布评论请先 登录

相关推荐

热点推荐

TI推出双通道16位ADC与时钟抖动清除器

日前,德州仪器 (TI) 宣布推出两款支持数据转换器 JEDEC JESD204B 串行接口标准的器件,其中 ADS42JB69是业界首款采用 JESD204B 接口、支持250 MSPS

发表于 11-05 09:21

•6356次阅读

MAX1121 1.8V、8位、250Msps模数转换器,L

MAX1121 1.8V、8位、250Msps模数转换器,LVDS输出,适用于宽带系统

MAX1121是单片、8位、250Msps

发表于 09-22 22:37

•1290次阅读

AD9467设计的16位250MSPS模数转换技术

本文介绍了AD9467主要特性, 功能方框图, 差分变压器耦合配置图以及AD9467用户评估板电路图和材料清单.

AD9467是ADI公司的16位取样频率200MSPS/

发表于 09-29 16:58

•6546次阅读

ADS42LB49/69双通道模数转换器的功能特点及应用范围

ADS42LB49 和 ADS42LB69 是高线性度、双通道、14 和 16 位 250MSPS

发表于 10-26 11:08

•3539次阅读

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V双通道模数转换器(ADC)

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V双通道

发表于 03-21 16:00

•6次下载

ADS54J69双通道、16位、500MSPS模数转换器数据表

电子发烧友网站提供《ADS54J69双通道、16位、500MSPS模数转换器数据表.pdf》资料

发表于 07-26 17:22

•2次下载

ADS42JBx9双通道、14和16位、250MSPS模数转换器数据表

电子发烧友网站提供《ADS42JBx9双通道、14和16位、250MSPS模数转换器数据表.pd

发表于 07-30 09:43

•0次下载

ADS42JBx9 14位和16位250MSPS模数转换器数据表

电子发烧友网站提供《ADS42JBx9 14位和16位250MSPS模数转换器数据表.pdf》资

发表于 07-30 09:45

•0次下载

ADS42JB46双通道、14位、160MSPS模数转换器数据表

电子发烧友网站提供《ADS42JB46双通道、14位、160MSPS模数转换器数据表.pdf》资料免费下载

发表于 07-30 09:27

•0次下载

ADS42JB69 双通道、16位、250MSPS模数转换器(ADC)技术手册

ADS42JB69 双通道、16位、250MSPS模数转换器(ADC)技术手册

评论