1. JESD204B 基本协议

其实使用到ADI的东西,基本也就没有太去关注协议这些东西,只是简简单单的有个了解就行,在实际调试的时候,用的也是Xilinx的评估版的JESD的IP,基本不需要自己做什么工作就能够把整个系统运行起来了。

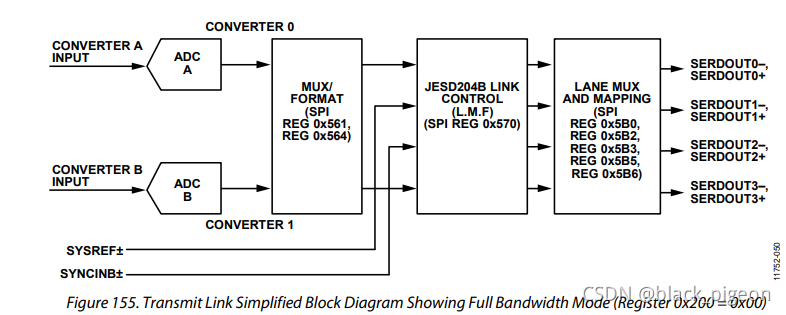

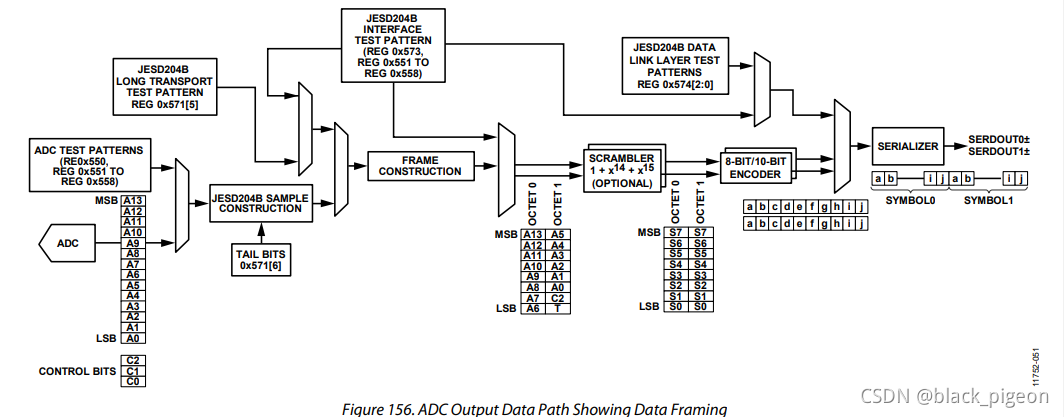

下面这个图是AD9680的一个基本的结构框图,可以看到这个ADC的作用就对输入的信号进行采集量化,在JESD204B链路建立之后,按照特定的格式组成数据帧,然后将数据帧通过JESD的接口将数据发送到FPGA上。其实基于JESD 204B的ADC和DAC在使用的时候,只需要去弄清楚链路是如何建立的就基本宣告JESD的驱动成功了。

1.1 JESD204B链路参数

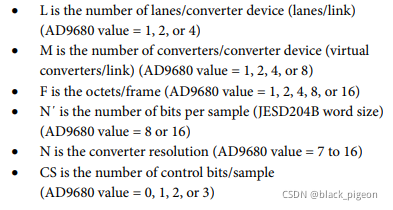

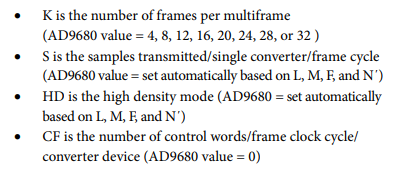

在JESD 204B的链路建立的过程中,最重要就是需要去关注链路所需要的参数,这些参数是后面对FPGA当中JESD IP的配置和对AD9680配置十分重要的,JESD IP的手册可以参考PG066和PG198这两个手册。

无论是JESD的发送还是接收,关于链路建立的关键参数都是一致的,如下面从AD9680的手册当中截取出来的一些参数。

通过这些参数能够确定JESD链路当中所需要使用到的LANE的数量,JESD该如何来进行组帧,组成的数据帧当中哪些位是数据位哪些位是控制位,组成的数据帧是对应哪一个ADC当中的哪一个转换器的。举个基于AD9680和FPGA进行全带宽传输的简单的例子,

L=4,M=2,F=2, N’=16, N=14, CS=2, K=32对应到JESD的链路当中就是

L=4需要4个lane来建立JESD 204链路,从FPGA角度来看就是需要使用到4个高速收发器接口。

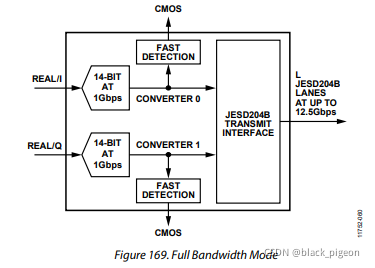

M=2产生ADC数据的数据来源有两个,如下面的图中所示

N’=16表示一个采样点中包含16bit数据,N=14表示ADC的采样精度为14bit,CS=2表示在传输JESD的数据的时候有两位的控制位,这样就能够很好地理解N’,N和CS的关系了。一般情况下一个采样点包含了具体的数据和控制位。

F=2表示一个数据帧当中有两个字节的数据,这两个字节刚好能够表示一个采样点。

K=32表示一个多帧当中有32个数据帧,通过前面的F参数,不难计算出一个多帧包含有64个字节的数据。

上面只是一个对JESD链路当中参数的一个简单的介绍,在实际的使用的时候,就是多看手册,弄清楚每个参数在具体的应用当中的作用就OK了。

下图是一个ADC采样点经采样后从传输层经过数据链路层,最终经过物理层进行传输的过程,在这个过程中,可以看到在具体的数据帧党总,上面介绍的一些关键的参数的具体的表现形式。

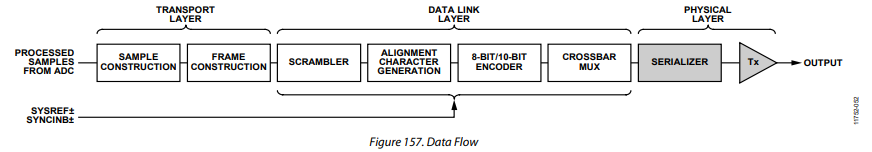

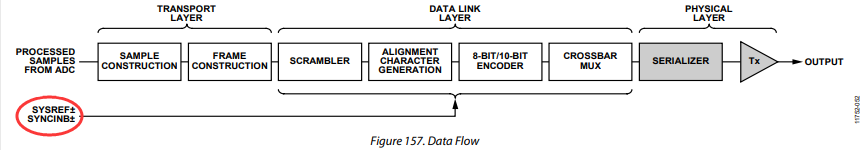

1.2 JESD 204B的分层

就像学习以太网的时候,要先了解一下OSI的涉及参考模型一样,在JESD当中,也有一个参考的数据分层的物理模型,下图所示的就是一个简单的JESD 204B的分层。主要有三个层级,分别是传输层,数据链路层和物理层。

传输层:传输层负责将庶几乎打包映射到有字节组成的JESD204B数据帧当中。传输层的映射关系是由链路层的设置的参数来决定的。

数据链路层:数据链路层负责数据传输的底层的功能,这些功能包括对数据进行加扰,插入用于多芯片同步,通道对齐等控制字符,完成8B10B转换,发送初始通道对齐序列(ILAS)等。ILAS是一个比较重要的序列,这个序列当中包含了链路的一些信息,在接收方当中,可以通过这个序列来知道当前链路的一个配置的状态。

物理层:物理层就是负责将数据进行传输的层,在我这里也就是指的FPGA和AD9680之间具体的高速接口了。

1.3 链路建立的过程

在我进行JESD204B的调试过程中,我认为最重要的一步就是链路建立的过程,只要能够正确地建立起JESD204B链路的link,那么后续的工作就比较简单了。因此首先需要弄清楚链路建立的一个过程。

在JESD204B subclass1中链路的建立主要包含一下几个步骤:

Code Group Synchronization (CGS) and SYNCINB±

Initial Lane Alignment Sequence (ILAS)

User Data and Error Detection

1.3.1 CGS & SYNC

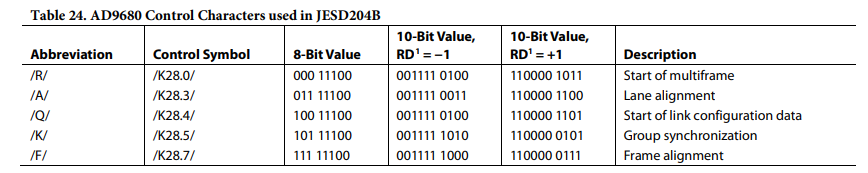

在CSG阶段,简而言之就是一个同步的阶段,如果对Xilinx的高速接口有一定的了解的话,就知道高速接口当中是如何实现数据和时钟的恢复和数据的对齐的,在CSG阶段,JESD的发送器会不停的发送/K28.5/字符。在JESD的接收器当中,就会根据所接收到的数据来检测是否接收到了/K28.5/字符,如果检测到了,就会使SYNC信号拉高,从而提示JESD发送器,当前已经检测到了/K28.5/也即已经同步上了。

这里需要提一下SYNC信号,在前面数据链路层当中,我们可以在数据链路层当中,有两个用于控制数据链路层的信号,分别是sysref和sync。JESD204B子类1是否同步上,跟这两个信号有着很紧密的关系。

举个简单的例子,ADC 转换器AD9680作为JESD的发送方,FPGA作为JESD的接收方,两者一个共同的参考信号sysref,链路是否建立是根据LMFC与sysref共同来决定的,作为数据的接收方,FPGA若成功检测到当前已经同步上,需要拉高sync,告诉AD9680当前FPGA已经能够同步了,数据的发送方才会进行下一步的操作。若sync一直不拉高,那么链路的建立将会一直处于CGS阶段,在JESD当中也就只能接收到/K28.5/(0xBC).

JESD常用的字符如下:

1.3.2 ILAS 阶段

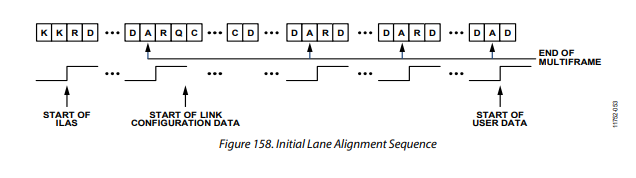

在这个阶段当中,JESD的发送方,会发送JESD链路的配置信息。ILAS阶段一般包含4个多帧。每个多帧以/R/字符表示开始,以/A/字符表示多帧结束。

在第一个多帧当中,填充的主要是0~255的递增数。

在第二个多帧当中,以/R/字符表示开始,然后发送一个Q字符,用于表示开始发送链路配置数据,从第三个字符开始发送链路配置数据,链路配置数据一共14个字符,其余地方用递增数进行填充。

第三个和第四个多帧,结构和第一个多帧一致。

1.3.3 用户数据

在ILAS阶段完成之后,就可以进行用户数据传输了。这些东西在JESD的IP里面都已经集成地很好了,在使用IP地时候,能够大大地减轻设计的难度。

-

接口

+关注

关注

33文章

9446浏览量

156146 -

dac

+关注

关注

44文章

2695浏览量

196408 -

链路

+关注

关注

1文章

77浏览量

14405 -

JESD204B

+关注

关注

6文章

83浏览量

19837

原文标题:JESD204B接口简介

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

jesd204b

JESD204B的系统级优势

JESD204B串行接口时钟的优势

JESD204B协议有什么特点?

JESD204B协议介绍

JESD204B的优势

JESD204B协议概述

JESD204B SystemC module 设计简介(一)

JESD204B标准及演进历程

JESD204B使用说明

一文详解JESD204B协议

一文详解JESD204B协议

评论