概述

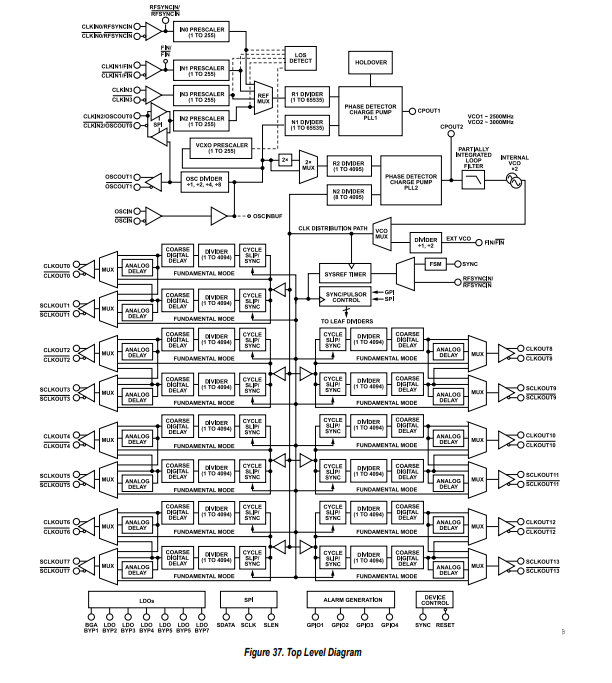

HMC7044B 是 [HMC7044]的修订版本,是一款高性能、双环路、整数 N 抖动衰减器,能够为具有并行或串行(JESD204B 和 JESD204C 类型)接口的高速数据转换器执行参考选择和超低相位噪声频率生成。在 HMC7044B 中,温度和电源电压等边缘情况下的输出相位对齐得到了改善。HMC7044B 具有两个整数模式 PLL 和重叠片上 VCO,它们可通过 SPI 选择,具有分别约 2.5 GHz 和 3 GHz 的宽调谐范围。该设备旨在满足 GSM 和 LTE 基站设计的要求,并提供广泛的时钟管理和分配功能,以简化基带和无线电卡时钟树设计。HMC7044B 提供 14 个低噪声和可配置输出,可灵活地与许多不同的组件(包括数据转换器、现场可编程门阵列 (FPGA) 和混频器本振 (LO))连接。

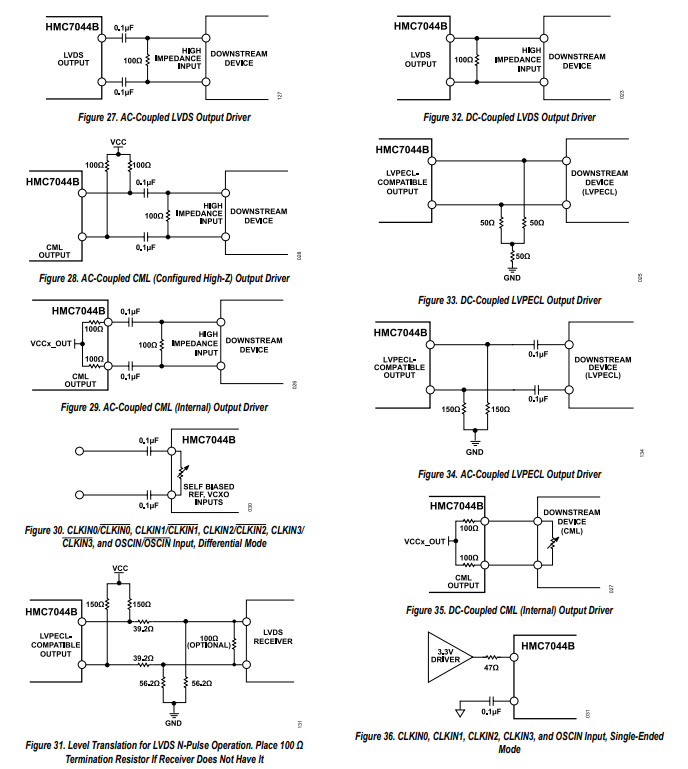

HMC7044B 的 DCLK 和 SYSREF 时钟输出可配置为支持信号标准,例如 CML、LVDS、LVPECL 和 LVCMOS,以及不同的偏置设置,以抵消不同的电路板插入损耗。

数据表:*附件:HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14输出抖动衰减器技.pdf

应用

- JESD204B 和 JESD204C 时钟产生

- 蜂窝基础设施(多载波 GSM、LTE、W-CDMA)

- 数据转换器时钟同步

- 微波基带卡

- 相位阵列参考分布

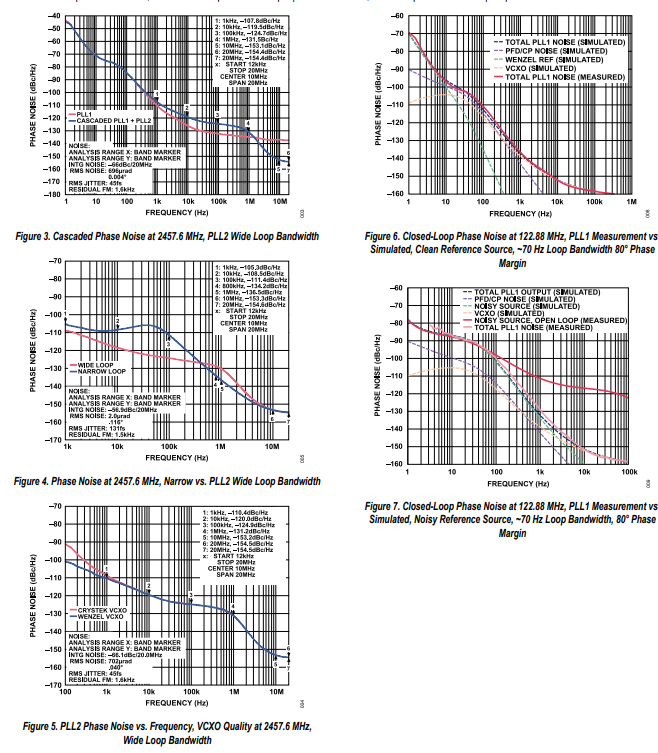

特性 - 超低均方根抖动:2457.6 MHz 时典型值为 44 fs(12 kHz 至 20 MHz)

- 本底噪声:2457.6 MHz 时为 −156 dBc/Hz

- 低相位噪声:800 kHz、983.04 MHz 输出时为 −141.7 dBc/Hz

- 来自 PLL2 的最多 14 个 LVDS、LVPECL 或 CML 类型设备时钟 (DCLK)

- 最大 CLKOUTx 和 SCLKOUTx 频率高达 3200 MHz

- JESD204B 和 JESD204C 兼容系统参考 (SYSREF) 脉冲

- 窄带,双核心 VCO

- 25 ps 模拟和 ½ VCO 周期数字延迟,可在每个 14 个时钟输出通道上独立编程

- SPI 可编程相位噪声与功耗

- SYSREF 有效中断可简化 JESD204B 和 JESD204C 同步

- 最多 2 个缓冲压控晶体振荡器 (VCXO) 输出

- LVDS、LVPECL、CMOS 和 CML 模式下最多 4 个输入时钟

- 频率保持模式可维持输出频率

- 信号丢失 (LOS) 检测和无中断参考切换

- 4× GPIO 警报/状态指示器,用于确定系统的健康状况

- 外部 VCO 输入支持高达 6000 MHz

- 板载调节器可实现优秀的 PSRR

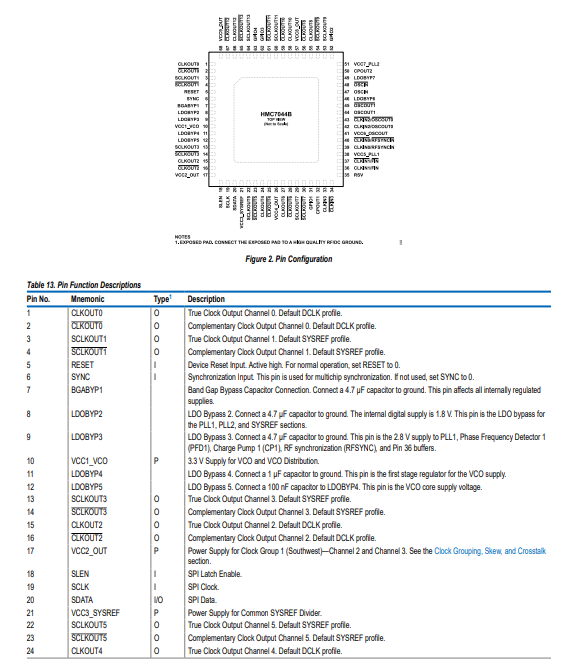

- 10 mm × 10 mm 68 引脚 LFCSP 封装

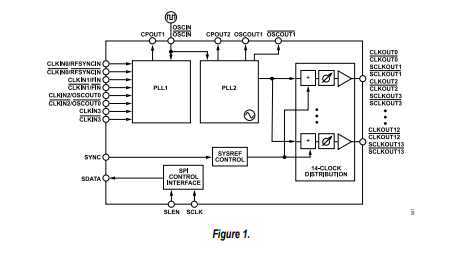

框图

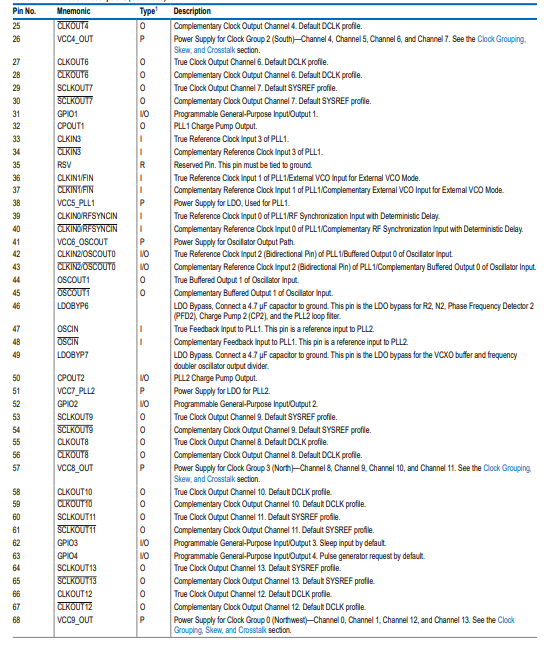

引脚配置描述

典型性能特征

典型应用电路

详细框图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

衰减器

+关注

关注

4文章

734浏览量

36584 -

数据转换器

+关注

关注

1文章

401浏览量

30756 -

环路

+关注

关注

0文章

51浏览量

12463

发布评论请先 登录

相关推荐

热点推荐

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

1. 概述PC7044是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B型)接口的高速数据转换

发表于 05-08 15:57

JESD204B的系统级优势

JESD204B产品组合的更多详情,其中包括 12 位、4GSPS ADC12J4000 模数转换器 (ADC);16 位、双通道、250MSPS ADS42JB69 ADC;16 位、4 通道、2.5GSPS DAC38J84 数模转换

发表于 09-18 11:29

JESD204B串行接口时钟的优势

多地数模转换器接口是JESD204B subclass1。其最大传输速率可达12.5Gbps,支持多链路和多器件的同步以及固定时差的测量。下表是各版本之间的差异: 在JESD204 接

发表于 06-19 05:00

JESD204C的标准和新变化

的应用的更高带宽需求。该标准的最新版本JESD204C于2017年底发布,以继续支持当前和下一代多千兆数据处理系统性能要求的上升趋势。JESD204C 小组委员会为该标准的新修订版制定

发表于 01-01 07:44

如何采用系统参考模式设计JESD204B时钟

LMK04821系列器件为该话题提供了很好的范例研究素材,因为它们是高性能的双环路抖动清除器,可在具有器件和SYSREF时钟的子类1时钟方案里驱动多达七个JESD204B转换

发表于 11-18 06:36

HMC7044: 带 JESD204B 接口的高性能、3.2 GHz、14 路输出抖动衰减器

HMC7044: 带 JESD204B 接口的高性能、3.2 GHz、14 路

发表于 03-21 11:14

•13次下载

LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表

LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持

发表于 04-22 15:52

•9次下载

LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持数据表

LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持

发表于 05-19 15:23

•14次下载

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

电子发烧友网为你提供ADI(ADI)AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet相关产品参数、数据手册,更有AD9207

发表于 10-16 19:02

从JESD204B升级到JESD204C时的系统设计注意事项

电子发烧友网站提供《从JESD204B升级到JESD204C时的系统设计注意事项.pdf》资料免费下载

发表于 09-21 10:19

•6次下载

JESD204B使用说明

JESD204B IP核作为接收端时,单独使用,作为发送端时,可以单独使用,也可以配合JESD204b phy使用。 JESD204B通常配合AD或DA使用,替代LVDS,提供更高的通讯速率,抗干扰

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册

LTC6953 是一款高性能、超低抖动的 JESD204B/JESD204C 时钟分配 IC。LTC6953 的 11 个输出可配置为最多

高性能时钟管理利器:HMC7044B深度解析

高性能时钟管理利器:HMC7044B深度解析 在电子设计领域,时钟管理对于保证系统的稳定运行和高性能表现至关重要。HMC7044B作为一款高性能

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14输出抖动衰减器技术手册

HMC7044B支持JESD204B和JESD204C的高性能、3.2GHz、14输出抖动衰减器技术手册

评论