Texas Instruments LMX1204 JESD缓冲器/多路复用器/分频器具有高频能力和极低抖动。这一特性可在不降低信噪比的情况下,很好地解决时钟精度、高频数据转换器问题。四个高频时钟输出中的每一个输出以及具有更大分频器范围的附加LOGICLK输出都与SYSREF输出时钟信号配对。JESD接口的SYSREF信号可以在内部生成,也可以作为输入传入,并重新计时为器件时钟。对于数据转换器时钟应用,务必使时钟的抖动小于数据转换器的孔径抖动。在需要对四个以上数据转换器进行时钟控制的应用中,可以使用多个器件开发各种级联架构,以分配所需的所有高频时钟和SYSREF信号。凭借其低抖动和低本底噪声,Texas Instruments LMX1204可与超低噪声基准时钟源相结合,是时钟控制型数据转换器的典型解决方案,尤其是以高于3GHz的频率采样时。

数据手册:*附件:Texas Instruments LMX1204 JESD缓冲器,多路复用器,分频器数据手册.pdf

特性

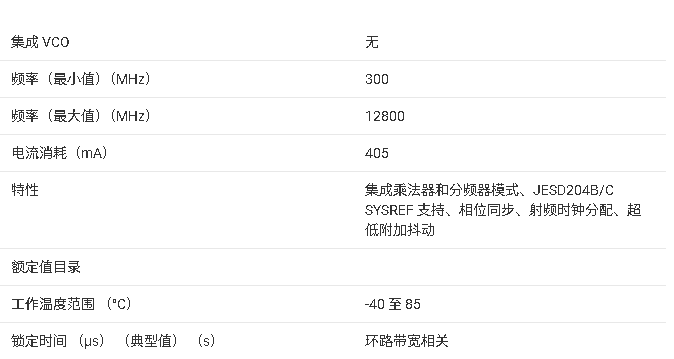

- 输出频率:300 MHz至12.8 GHz

- 超低噪声

- 6GHz输出时,本底噪声为–161dBc/Hz

- 6GHz输出、10kHz偏移时,1/f噪声为–154dBc/Hz

- 抖动:5fs(12kHz至20MHz)

- 附加抖动:<30fs(DC至fCLK)

- 四个具有相应SYSREF输出的高频时钟

- 共享分频器,支持÷1(缓冲器模式)、÷2、3、4、5、6、7和8

- 基于PLL的共享倍频器,支持x1(滤波器模式)、x2、x3和x4

- LOGICLK和相应的SYSREF输出

- 基于单独的分频组

- ÷1、2、4预分频器

- ÷1(旁路)、2、…、1023后分频器

- 八个可编程输出功率级别

- 同步SYSREF时钟输出

- 在12.8GHz下,508次延迟步长调整,每次小于2.5ps

- 发生器和中继器模式

- SYSREFREQ引脚的窗口化功能,以优化计时

- 针对所有分频和倍频器件的同步功能

- 工作电压:2.5V

- 工作温度:-40ºC至85ºC

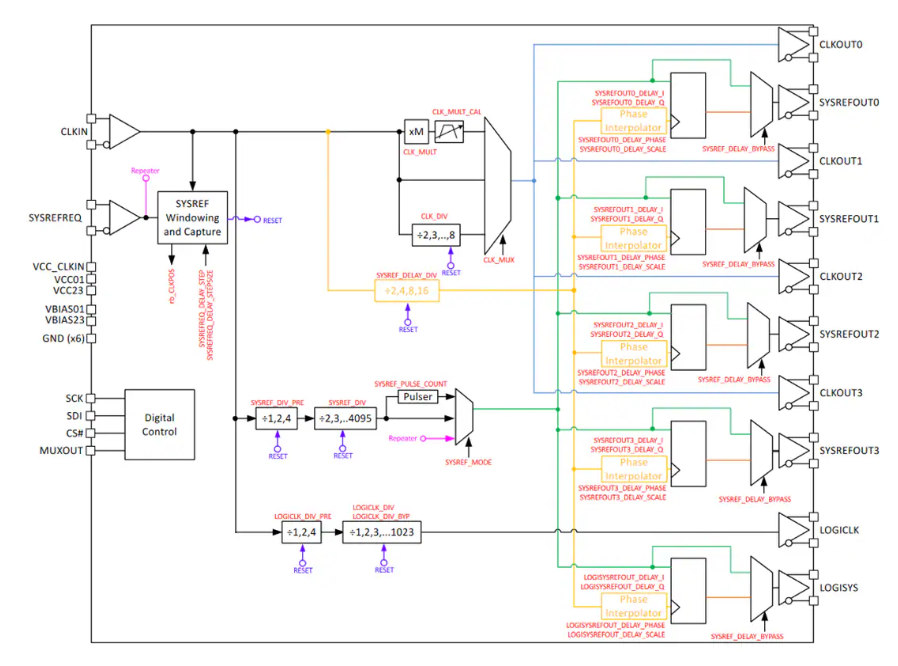

功能框图

LMX1204高性能JESD缓冲器/乘法器/分频器技术解析与应用指南

一、核心特性概述

LMX1204是德州仪器(TI)推出的超低噪声高频时钟管理芯片,具有以下突出特性:

- 超宽频率范围:支持300MHz至12.8GHz输出频率

- 卓越的噪声性能:

- -161dBc/Hz噪声基底(6GHz输出时)

- 仅5fs抖动(12kHz-20MHz积分带宽)

- <30fs附加抖动(DC至fCLK)

- 多功能时钟处理:

- 4路高频时钟输出+对应SYSREF输出

- 可配置为缓冲/分频(÷1-8)/倍频(×1-4)模式

- 独立逻辑时钟输出(LOGICLK)支持分频比1-1023

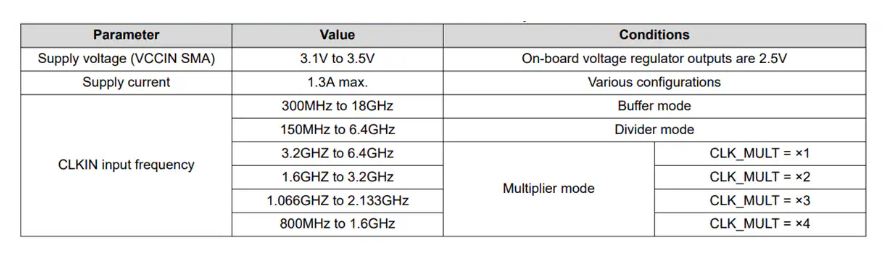

二、关键参数详解

2.1 电气特性

| 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 工作电压 | VDD | 2.4 | 2.5 | 2.6 | V |

| 输入频率 | CLKIN | 0.3 | - | 12.8 | GHz |

| 附加抖动 | 缓冲模式 | - | 5 | - | fs |

| 相位噪声 | 6GHz输出,10kHz偏移 | - | -154 | - | dBc/Hz |

| 电源电流 | 所有输出开启 | - | 1050 | - | mA |

2.2 封装特性

- 封装类型:40引脚VQFN (6mm×6mm)

- 热阻参数:

- θJA=24.8°C/W(4层板)

- θJB=6.9°C/W(优化布局)

三、架构与功能解析

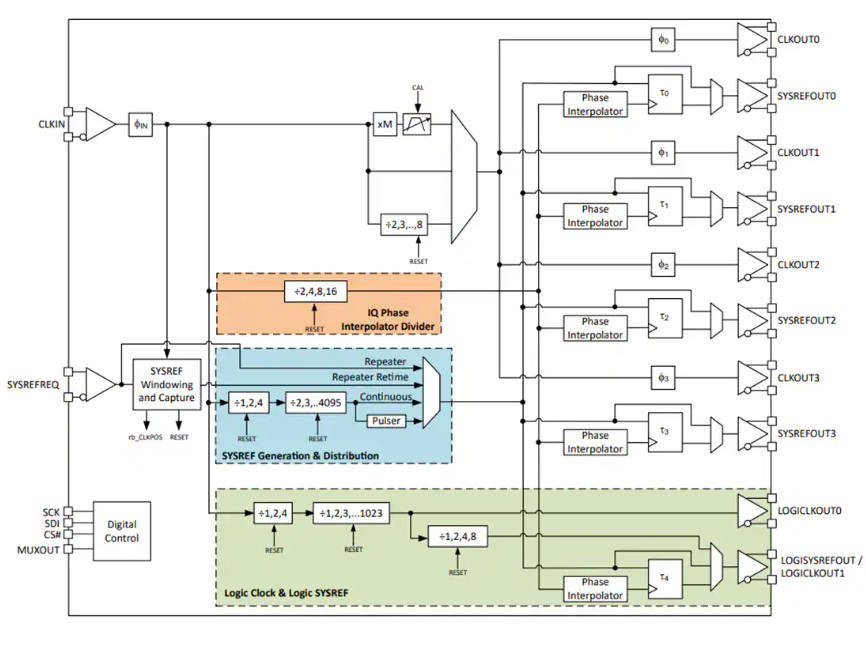

3.1 时钟通道架构

- 主时钟路径:

- 四通道独立输出(CLKOUT0-3)

- 每通道支持:

- 直通模式(缓冲)

- 分频模式(÷2-8)

- 倍频模式(×1-4 PLL)

- 可编程输出功率(8级调节)

- 逻辑时钟路径:

- 独立分频器(÷1-1023)

- 支持LVDS/LVPECL/CML输出格式

- 可调共模电压(0.9-1.2V)

3.2 SYSREF子系统

- 工作模式:

- 发生器模式(内部生成)

- 脉冲模式(1-16个脉冲)

- 中继模式(外部信号再生)

- 精密延时控制:

- 508步进可调延时

- 步进精度<2.5ps@12.8GHz

- 支持多器件同步

四、典型应用设计

4.1 高速数据转换器时钟方案

设计参数:

- 参考时钟:3.2GHz LVDS

- 目标频率:6.4GHz(×2倍频)

- SYSREF频率:100MHz

- 输出配置:4路CML输出

关键配置:

- 倍频器设置:

- CLK_MUX=3(倍频模式)

- CLK_MULT=2(×2)

- SMCLK_DIV=32(状态机时钟≤30MHz)

- SYSREF生成:

- SYSREF_DIV=32(100MHz输出)

- 延时校准:SYSREFOUTx_DELAY_I=0x7F

4.2 布局要点

- 电源处理:

- 每VCC引脚配置0.1μF+1μF去耦电容

- 关键电源线宽≥20mil

- 信号布线:

- 差分对长度匹配<5mil

- 避免90°转角,采用圆弧走线

- 热管理:

- 使用4×4阵列散热过孔

- 最大功耗区铜箔面积≥100mm²

五、行业应用场景

六、设计注意事项

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

缓冲器

+关注

关注

6文章

2236浏览量

49059 -

分频器

+关注

关注

43文章

537浏览量

53782 -

多路复用器

+关注

关注

9文章

1065浏览量

66839

发布评论请先 登录

相关推荐

热点推荐

Texas Instruments LMX1205 JESD缓冲器/乘法器/除法器数据手册

Texas Instruments LMX1205 JESD缓冲器/乘法器/分频器具有高频能力、极低抖动以及可编程时钟输入和输出延迟。得益于

Texas Instruments LMX1860SEPEVM评估模块数据手册

Texas Instruments LMX1860SEPEVM评估模块配置用于评估LMX1860-SEP的运行和性能。LMX1860-SEP是一款四输出、超低附加抖动射频 (RF)

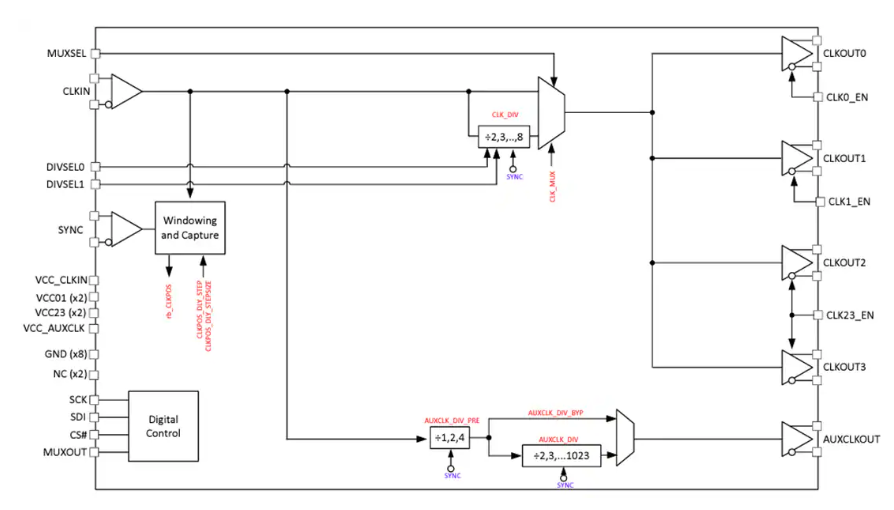

德州仪器LMX1214射频缓冲器与分频器技术解析

Texas Instruments LMX1214射频缓冲器和分频器具有高输出频率、超低噪声基底和极低偏斜时钟分布。该设备有四个高频输出时钟和一个低频辅助时钟输出。Texas Instruments

LMX1204低噪声高频JESD缓冲器/倍频器/分频器技术解析

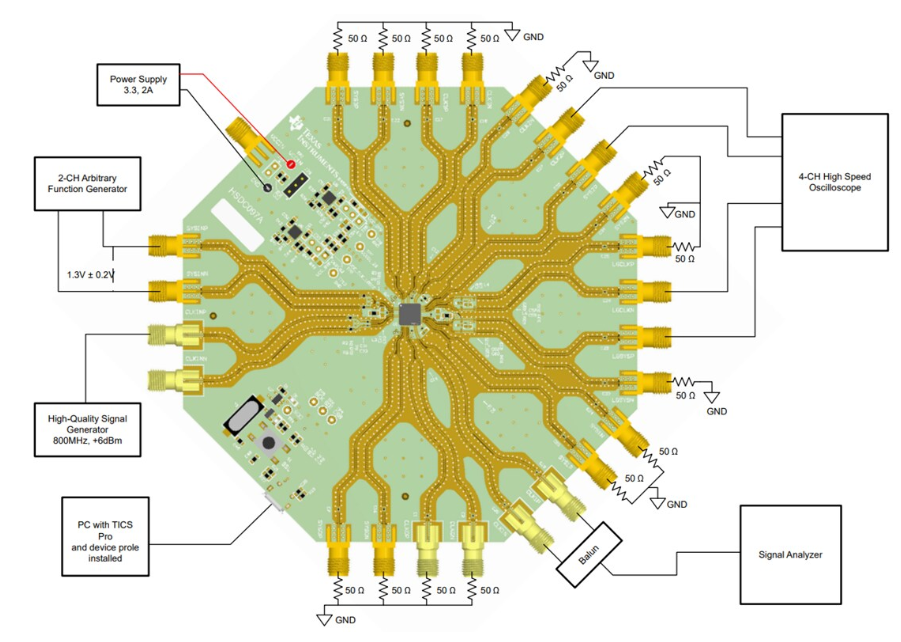

Texas Instruments LMX1204EVM评估模块 (EVM) 设计用于评估LMX1204的性能,LMX1204是一款四路输出、超低附加抖动射频 (RF)

LMX1204 低噪声高频 JESD 缓冲器/乘法器/分频器技术文档总结

该器件的高频能力和极低抖动,是时钟精度、高频数据转换器的绝佳方法,而不会降低信噪比。四个高频时钟输出中的每一个,以及具有更大分频器范围的附加 LOGICLK 输出,都与一个 SYSREF 输出时钟

LMX1205-EP:低噪声、高频JESD缓冲器/乘法器/分频器的深度解析

LMX1205-EP:低噪声、高频JESD缓冲器/乘法器/分频器的深度解析 在电子设计领域,时钟

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析

LMX1214:高性能低噪声时钟缓冲与分频器的深度解析 在电子设计领域,时钟信号的处理至关重要,它直接影响着系统的

LMX1204:低噪声、高频JESD缓冲器/倍增器/分频器的卓越之选

LMX1204:低噪声、高频JESD缓冲器/倍增器/分频器的卓越之选 在电子设计领域,时钟信号的精确性和稳定性对于系统

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析

LMX1214:高性能低噪声时钟缓冲及分频器的技术剖析 在电子设计领域,时钟信号的处理至关重要,它直接影响着整个系统的

LMX1204:高性能低噪声时钟利器的深度剖析

LMX1204:高性能低噪声时钟利器的深度剖析 引言 在当今高速电子系统设计中,时钟信号的质量对系统性能起着至关重要的作用。低噪声、高频率的时钟缓冲器、

汽车级时钟缓冲器与乘法器 CDCS504-Q1 设计指南

汽车级时钟缓冲器与乘法器 CDCS504-Q1 设计指南 引言 在汽车电子应用中,时钟信号的精准处理至关重要。CDCS504-Q1 作为一款专为汽车应用设计的时钟缓冲器和时钟

LMX1204高性能JESD缓冲器/乘法器/分频器技术解析与应用指南

LMX1204高性能JESD缓冲器/乘法器/分频器技术解析与应用指南

评论