概述

LTC6953 是一款高性能、超低抖动的 JESD204B/JESD204C 时钟分配 IC。LTC6953 的 11 个输出可配置为最多 5 个 JESD204B/JESD204C subclass 1 器件时钟 / SYSREF 对以及一个通用输出,或者就是 11 个面向非 JESD204B/JESD204C 应用的通用时钟输出。每个输出都有自己的可个别编程分频器和输出驱动器。所有输出也可以采用个别的粗略半周期数字延迟和精细模拟时间延迟实现同步,并设定为精确的相位对齐。

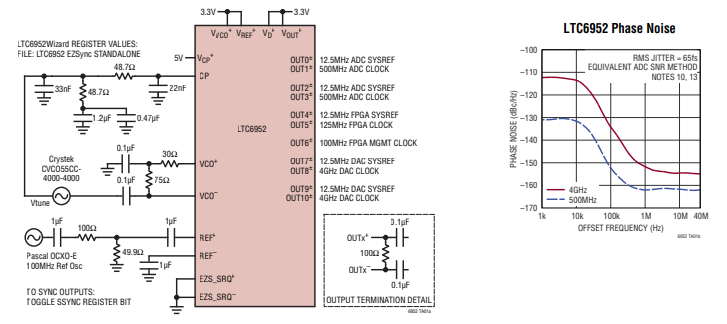

对于需要 11 个以上总输出的应用,可以使用 EZSync 或 ParallelSync 同步协议将多个 LTC6953 与 LTC6952 和 LTC6955 连接在一起。

数据表:*附件:LTC6953具有11个输出并支持JESD204B JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册.pdf

应用

- 高性能数据转换器时钟

- 无线基础设施

- 测试和测量

特性

- JESD204B/JESD204C,子类 1 SYSREF 信号生成

- 附加输出抖动 < 6fs

RMS(集成带宽 = 12kHz 至 20MHz,f = 4.5GHz) - 附加输出抖动 65fs

RMS(ADC SNR 方法) - EZSync ^™^ 、ParallelSync^™^ 多芯片同步

- 11 个独立低噪声输出,具有可编程粗数字延迟和精细模拟延迟

- 灵活的输出可以用作套件时钟或 SYSREF 信号

- LTC6952Wizard 软件设计工具支持

- 工作温度范围为 –40°C 至 125°C

应用电路

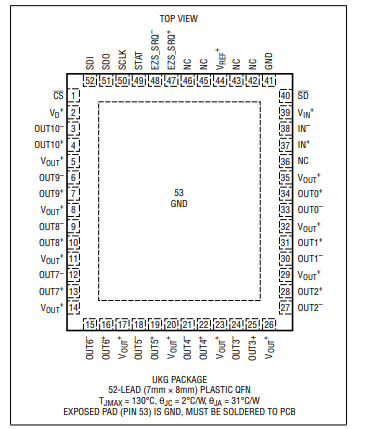

引脚配置描述

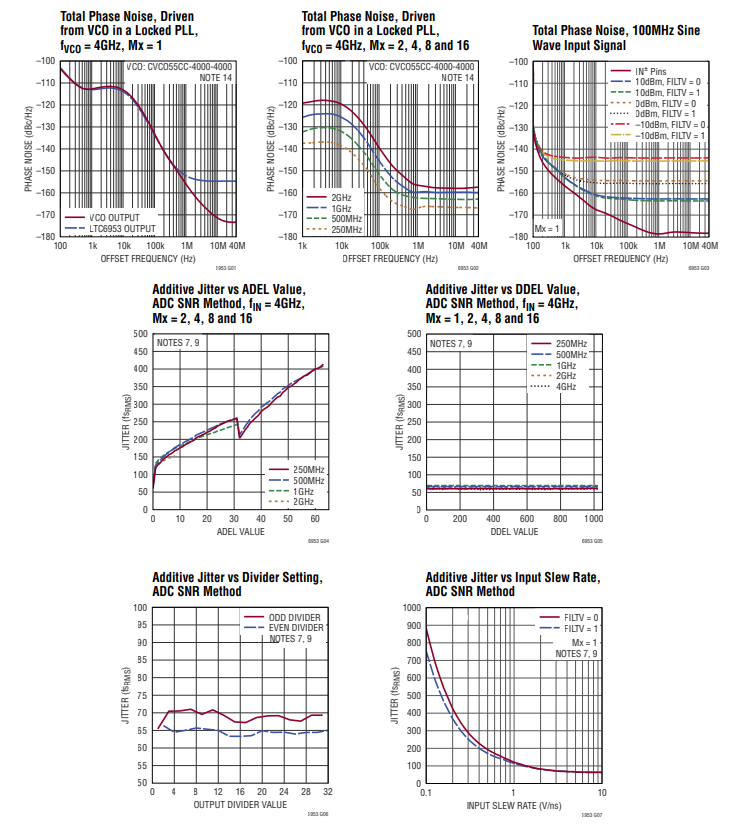

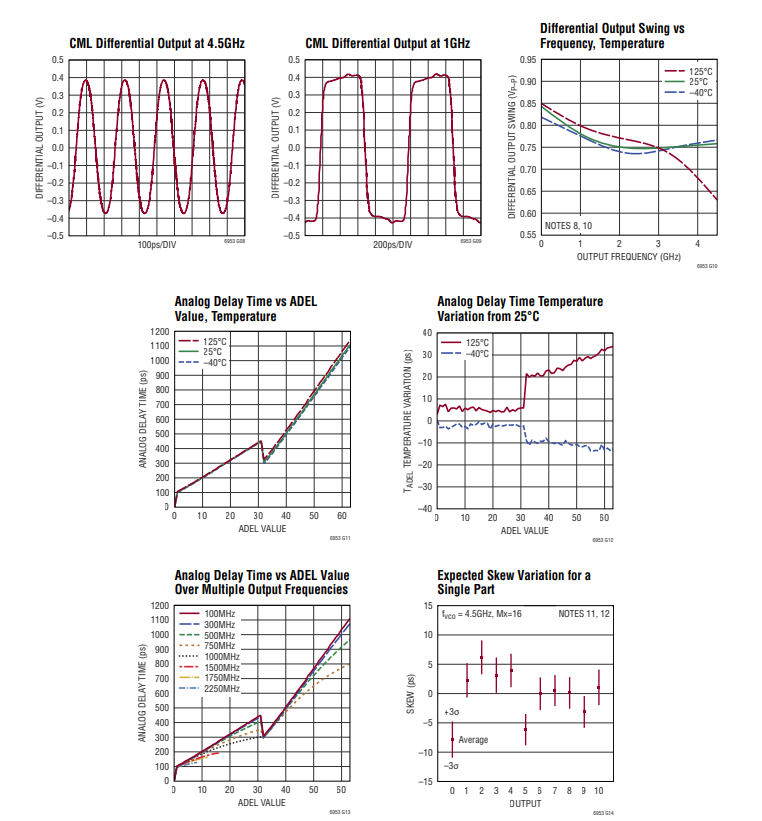

典型性能特征

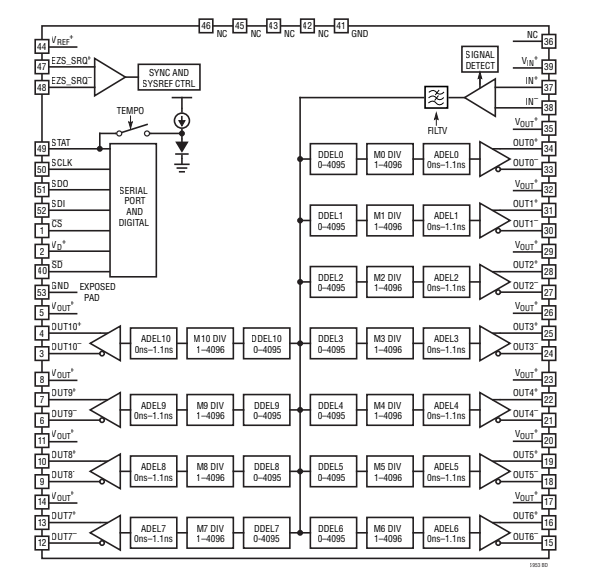

框图

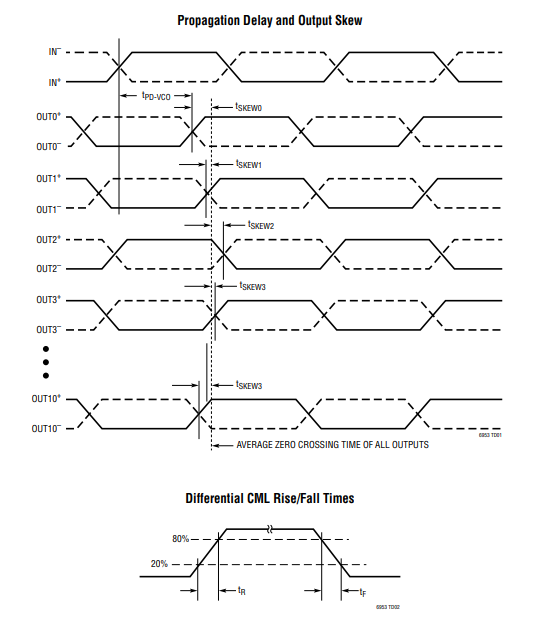

时序图

操作

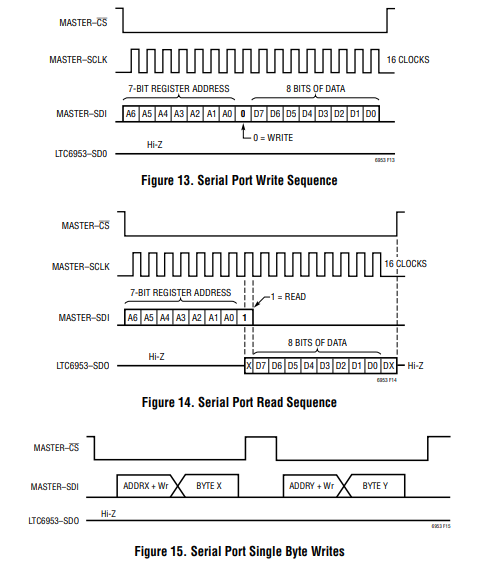

第一个字节的高7位是寄存器地址,最低有效位(LSB)为“1”表示从器件读取数据 ,LSB为“0”表示向器件写入数据。随后的一个或多个字节是来自或写入指定寄存器的地址数据。图13为详细写序列示例,图14为读序列示例。

图15展示了两次写通信突发的示例。第一次突发的第一个字节包含来自串行总线主机的目标寄存器地址(ADDRX),LSB为“0”表示写操作。下一个字节是要写入ADDRX寄存器的数据。随后将片选信号(CS)拉高,以终止传输。第二次突发的第一个字节包含目标寄存器地址(ADDRY),LSB指示写操作。串行数据输入(SDI)上的下一个字节是要写入ADDRY寄存器的数据。然后将CS拉高,以终止传输。

多字节传输

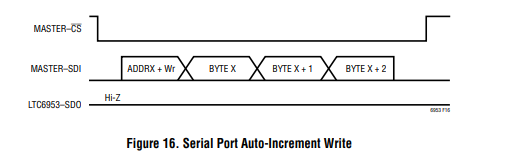

如图16所示,利用LTC6953的寄存器地址自动递增功能,可实现更高效的多字节数据传输。串行端口主机先发送目标寄存器地址,第一个字节按常规方式写入数据 ,第二个字节及后续字节也按此方式操作。

并继续发送后续寄存器的数据字节。第一个字节的地址为ADDRX + 1,第二个字节的地址为ADDRX + 2,依此类推。如果寄存器地址指针试图递增超过56(十六进制h38 ),它会自动重置为0。

图17展示了从器件自动递增读取的示例。第一次突发的第一个字节包含来自串行总线主机的目标寄存器地址(ADDRX),最低有效位(LSB)为“1”表示读操作。LTC6953检测到读突发后,将数据从其高阻抗(Hi-Z)状态输出到串行数据输出(SDO),并顺序发送多个字节,从ADDRX寄存器的数据开始。在突发结束前,器件会忽略串行数据输入(SDI)上的所有其他数据。

多点配置

多个LTC6953器件可以共享串行总线。在这种多点配置中,所有器件的串行时钟(SCLK)、串行数据输入(SDI)和串行数据输出(SDO)都是共用的。串行总线主机必须为每个器件使用单独的片选信号(CS),并确保在任何时候只有一个器件的CS被置为有效。建议连接一个高阻值电阻到SDO,以确保在高阻抗状态下线路能回到已知电平。

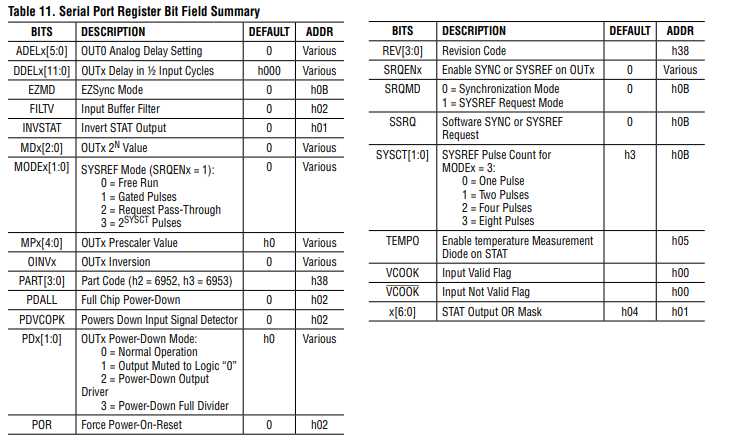

串行端口寄存器

LTC6953的内存映射见表10,详细的位描述见表11。寄存器地址列以十六进制格式显示,在“ADDR”下。每个寄存器标记为只读(R)或读写(RW)。寄存器的默认值在器件上电或复位后显示。

地址为h00的只读寄存器用于确定不同的状态标志。这些标志可通过配置状态寄存器h01立即输出到STAT引脚。有关更多信息,请参见“输出”部分。

地址为h38的寄存器是一个用于器件识别的只读字节。

-

时钟

+关注

关注

11文章

1999浏览量

135239 -

分配器

+关注

关注

0文章

216浏览量

27431 -

JESD204B

+关注

关注

6文章

86浏览量

19951

发布评论请先 登录

替代HMC7044超低噪高性能时钟抖动消除器支持JESD204B

JESD204B串行接口时钟的优势

JESD204C的标准和新变化

如何采用系统参考模式设计JESD204B时钟

JESD204B协议介绍

LTC6953 具有 11 个输出并支持 JESD204B/JESD204C 协议的超低抖动、4.5GHz 时钟分配器

LTC6952:超低抖动、4.5 GHz PLL,带11个输出和JESD204B/JESD204C支持数据表

LTC6953:超低抖动、4.5 GHz时钟分配器,带11个输出和JESD204B/JESD204C支持数据表

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

从JESD204B升级到JESD204C时的系统设计注意事项

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册

LTC6953具有11个输出并支持JESD204B/JESD204C协议的超低抖动、4.5GHz时钟分配器技术手册

评论