近日,全球晶圆代工龙头台积电宣布推出4nm制程工艺——N4P,希望借此赢得明年苹果公司A16处理器代工订单。台积电表示,凭借5nm(N5)、4nm(N4)、3nm(N3)、以及最新的N4P制程,将能

2021-10-28 08:05:11 18894

18894 新思科技公司(Synopsys, Inc., 纳斯达克股票市场代码:SNPS)日前宣布: 该公司针对多家领先的晶圆代工厂优化的28纳米工艺DesignWare IP已赢得第100项设计。

2012-09-20 10:11:40 1485

1485 美国高通公司与台积电公司今日共同宣布,美国高通公司的全资子公司美国高通技术公司将率先采用台积电公司28纳米高性能移动(28HPM)制程生产芯片。

2013-02-26 17:20:20 1427

1427 微处理器设计公司ARM与台积电今天共同宣布,首个采用台积电下下代16nm工艺制程FinFET技术生产的ARM Cortex-A57处理器已成功流片。Cortex-A57处理器为ARM旗下性能最高的处理器。

2013-04-03 09:05:05 1484

1484 半导体设计公司新思科技 (Synopsys) 17 日宣布,将与晶圆代工龙头台积电合作推出针对高效能运算 (High Performance Compute) 平台的创新技术,而这些新技术是由新思科技与台积电合作的 7 纳米制程 Galaxy 设计平台的工具所提供。

2016-10-18 10:55:37 1097

1097 新思科技接口和基础 IP 组合已获多家全球领先企业采用,可为 ADAS 系统级芯片提供高可靠性保障 摘要: 面向台积公司N5A工艺的新思科技IP产品在汽车温度等级2级下符合 AEC-Q100 认证

2023-10-23 15:54:07 1964

1964 芯片PMIC 5即将问世,由于改为BCD制程,台积电凭借先进制程技术优势,可望拿下高通新一代PMIC 5订单约70~80%数量,并牵动高通电源管理芯片代工厂大洗牌。 业界推估高通各种用途电源管理芯片的年

2017-09-22 11:11:12

越来越先进,台积电的5nm制程成本也水涨船高,开发一款芯片的费用将达到5.4亿美元,台积电5nm全掩模流片费用大概要3亿人民币,而且还不包含IP授权费用。如此高的门槛,大部分公司都会选择观望。目前,也

2020-03-09 10:13:54

Kochpatcharin表示:“台积公司与新思科技等开放创新平台(OIP)合作伙伴紧密合作,助力我们的客户在执行定制及模拟模块的工艺制程设计迁移时,提高生产效率并加快设计收敛。现在,通过全新的新思科技AI驱动型模

2023-04-03 16:03:26

10nm将会流片,而张忠谋更是信心十足,他直言不讳地表示10nm量产后将会抢下更高的份额。台积电联席CEO刘德音此前也曾在一次投资人会议上透露,公司计划首先让自己的10纳米芯片产线在今年底前全面展开

2016-01-25 09:38:11

台积电称其已解决造成40nm制程良率不佳的工艺问题

据台积电公司高级副总裁刘德音最近在一次公司会议上表示,台积电40nm制程工艺的良率已经提升至与现有65nm制程

2010-01-21 12:22:43 1259

1259 新思科技完整实施流程助力英飞凌在中国成功实现首款40纳米3G基带处理器芯片设计和一次流片成功

中国北京和西安,2010年8月9日—全

2010-08-11 14:39:39 773

773 Cadence设计系统公司日前宣布展讯通信有限公司实现了其首款40纳米低功耗GSM/GPRS/EDGE/TD-SCDMA/HSPA商用无线通信芯片的一次性流片成功。

2011-01-22 10:04:17 1235

1235 联电(2303-TW)(UMC-US)与全球半导体设计制造软体暨IP领导厂商新思科技(Synopsys)昨日共同宣布,双方已扩展夥伴关系,将于联电28奈米HLP Poly SiON制程平台上开发新思科技的DesignWare IP。 联电表

2011-10-13 09:41:08 992

992 新思科技公司日前宣布:该公司与三星在FinFET技术上的多年合作已经实现了一个关键性的里程碑,即采用三星的14LPE工艺成功实现了首款测试芯片的流片

2013-01-09 12:11:31 1469

1469 领先的韩国半导体公司TLi采用Arasan的通用闪存(UFS)知识产权(IP)产品实现了芯片设计的出货,该公司之前获得了Arasan的UFS设备控制器IP及支持高达Gear 3速率的MPHY等产品的授权。TLi是最新一家使用Arasan的UFS Total IP解决方案成功实现芯片设计的公司。

2016-01-06 17:46:12 6084

6084 ASIC的复杂性不断提高,同时工艺在不断地改进,如何在较短的时间内开发一个稳定的可重用的ASIC芯片的设计,并且一次性流片成功,这需要一个成熟的ASIC的设计方法和开发流程。

2016-12-12 14:07:46 4384

4384 在晶圆代工市场,台积电与三星的竞争始终是大家关心的戏码。三星虽然有高通等VIP客户,但在7纳米制程节点,高通预计会转投台积电,三星要想受更多客户的青睐,只能从制程技术着手了。这也是三星为什么跳过非

2018-06-19 15:06:00 5263

5263 Mali-G76处理器)的初期采用者实现了成功的流片。采用Fusion技术的新思科技设计平台、Verification Continuum Platform和DesignWare接口IP互相配合,提供了优化的性能、功耗和面积,并加速了基于Arm的产品上市时间。

2018-07-28 11:17:00 1833

1833 日前,才在英国伦敦发布会上展出4款Mate 20系列手机,以及新款麒麟980处理器的华为,根据外电报导,更新一代的麒麟990处理器也已经发展到一个阶段。这款预计采用台积电内含EUV技术,7纳米+加强版制程的处理器,预计将在2019年的第1季进行流片。

2018-10-22 14:48:20 9144

9144 台积电总裁魏哲家昨(6)日在一年一度的供应链论坛中透露,台积电将在南科六厂旁,新建一座8英寸厂,满足客户对特殊制程要求。这是2003年台积电在上海松江8英寸厂成立后,台积电15年来第一次新建8英寸厂。

2018-12-07 15:06:32 2888

2888 4月4日消息,据Digitimes报道,台积电宣布在开放创新平台之下推出5nm设计架构的完整版本,协助客户实现支持下一代高效能运算应用产品的5nm系统单芯片设计,目标锁定拥有广阔发展前景的5G与人

2019-04-04 11:16:02 3456

3456 就在16日一早,韩国晶圆代工厂三星宣布发展完成 5 纳米制程,并且推出 6 纳米制程,并准备量产 7 纳米制程的同时,晶圆代工龙头台积电也在傍晚宣布,推出 6 纳米 (N6) 制程技术,除大幅强化

2019-04-17 16:42:50 3248

3248 新思宣布,其用于台积电7纳米制程技术的DesignWare逻辑库、嵌入式存储器、界面和类比IP已获得超过250个设计的选用(design wins),目前已经有近30家半导体厂商选择了新思7纳米

2019-05-14 16:25:27 3405

3405 新思科技近日宣布与GLOBALFOUNDRIES (GF)合作,针对GF的12纳米领先性能(12LP) FinFET工艺技术,开发覆盖面广泛的DesignWare® IP组合,包括多协议25G

2019-07-05 09:13:13 3813

3813 台积电宣布,其领先业界导入极紫外光(EUV)微影技术的7纳米强效版(N7+)制程已协助客户产品大量进入市场。导入EUV微影技术的N7+奠基于台积电成功的7纳米制程之上,也为明年首季试产6纳米和更先进制程奠定良好基础。

2019-10-08 16:11:37 3646

3646 就在晶圆代工龙头台积电之前宣布旗下6纳米制程将在2020年第1季推出,而更新的5纳米制程也将随之在后的情况下,半导体模拟软件大厂ANSYS于16日宣布,旗下的半导体套件解决方案已获台积电最新版N5

2019-10-17 16:19:11 4053

4053 根据台积电总裁魏哲家日前在法人说明会中的说法指出,台积电的5纳米制程(N5)已进入风险试产阶段,并有不错的良率表现。对此,根据供应链的消息指出,目前已经进入风险试产阶段的5纳米制程其良率达到了50%,而且月产能可上看8万片的规模。

2019-10-28 16:32:41 3576

3576 关于台积电的N5流程,ChainNews通过RetiredEngineer报告称,苹果迅速介入以弥补华为削减开支所带来的损失。它补充说,苹果还要求台积电在第四季度每月为其下一代iDevices增加近10,000个晶圆。

2020-04-25 10:14:49 3246

3246 6月11日消息,Moortec今天宣布其深度嵌入式监控产品组合再添新成员 -- 基于台积电N5工艺技术的分布式热传感器(DTS)。Moortec高度微粒化DTS的面积只有一些标准芯片内热传感器

2020-06-15 15:04:32 2766

2766 Moortec宣布其深度嵌入式监控产品组合再添新成员 -- 基于台积电N5工艺技术的分布式热传感器(DTS)。Moortec高度微粒化DTS的面积只有一些标准芯片内热传感器解决方案的七分之一,还支持

2020-08-04 15:00:02 1076

1076 据珠海特区报近日报道称,中国领先的一站式IP和定制芯片领军企业——芯动科技发布消息称,该公司已完成全球首个基于中芯国际FinFET N+1先进工艺的芯片流片和测试,所有IP全自主国产,功能一次测试通过,为国产半导体生态链再立新功。

2020-10-12 09:46:18 7398

7398 我国一站式IP定制芯片企业芯动科技(INNOSILICON)近日宣布:已完成全球首个基于中芯国际FinFET N+1先进工艺的芯片流片和测试,所有IP全自主国产,功能一次测试通过。 芯动科技拥有自主

2020-10-13 17:33:19 3784

3784 、DDR5、LPDDR5、MIPI、OTP NVM等 ●新思科技与GF的长期合作,成功实现了DesignWare IP核从180nm到12nm的开发,并可应用于广泛领域 新思科技(Synopsys)近日宣布

2020-11-03 16:48:08 2984

2984 当下的半导体界,最值钱的非晶圆代工产能莫属了。而作为行业龙头,台积电的产能,特别是先进制程的,几乎呈现被“疯抢”的状态,这也成为了该公司幸福的烦恼。就在不久前,台积电宣布取消未来一段时间内12英寸晶

2021-01-12 14:55:48 2719

2719 DesignWare HBM2E PHY IP 可提供每秒 460 GB 的聚合带宽,能够满足先进 FinFET 工艺 SoC 对海量计算性能的要求。HBM2E IP 是新思科技全面内存接口 IP

2021-02-14 09:22:00 1151

1151 SoC 设计与应用技术领导厂商Socionext Inc.(以下“Socionext”)宣布,公司将采用台积电最新5nm制程工艺(N5P)用于下一代汽车定制芯片业务。Socionext汽车定制芯片

2021-02-05 11:50:27 2701

2701 最大的RISC-V架构厂商SiFive近日宣布,其OpenFive部门已成功采用台积电(TSMC)的N5工艺技术流片公司首个SoC,采用2.5D封装HBM3存储单元,带宽7.2Gbps。在半导体行业中,流片意味着芯片设计大功告成,一般会在一年内投入商用。

2021-05-01 09:33:00 3547

3547

据外媒最新报道,三星宣布,3nm制程技术已经正式流片! 据悉,三星的3nm制程采用的是GAA架构,性能上完胜台积电的3nm FinFET架构! 据报导,三星在3nm制程的流片进度是与新思科技合作完成

2021-07-01 15:27:44 4638

4638 电子发烧友网报道(文/吴子鹏)近日,全球晶圆代工龙头台积电宣布推出4nm制程工艺——N4P,希望借此赢得明年苹果公司A16处理器代工订单。台积电表示,凭借5nm(N5)、4nm(N4)、3nm(N

2021-10-30 11:25:16 9826

9826 通过与台积公司在早期的持续合作,我们为采用台积公司先进的N3制程技术的设计提供了高度差异化的解决方案,让客户更有信心成功设计出复杂的SoC。

2021-11-02 09:24:25 687

687 双方拓展战略合作,提供全面的3D系统集成功能,支持在单一封装中集成数千亿个晶体管 新思科技3DIC Compiler是统一的多裸晶芯片设计实现平台,无缝集成了基于台积公司3DFabric技术

2021-11-05 15:17:19 6382

6382 双方合作涵盖新思科技的Interface IP、基于TSMC 3DFabric™的设计解决方案以及针对台积公司N4制程技术的PPA优化。

2021-11-08 11:54:45 781

781 技(Synopsys)近日宣布其数字定制设计平台已获台积公司N3制程技术认证,双方将共同优化下一代芯片的功耗、性能和面积(PPA)。基于多年的密切合作,本次经严格验证的认证是基于台积公司最新版本的设计规则手册(DRM)和制程设计套件(PDK)。此外,新思科技

2021-11-16 11:06:32 2326

2326 新思科技(Synopsys)近日推出面向台积公司N6RF工艺的全新射频设计流程,以满足日益复杂的射频集成电路设计需求。

2022-06-24 14:30:13 1700

1700 新思科技数字和定制设计流程获得台积公司的N3E和N4P工艺认证,并已推出面向该工艺的广泛IP核组合。

2022-07-12 11:10:51 1780

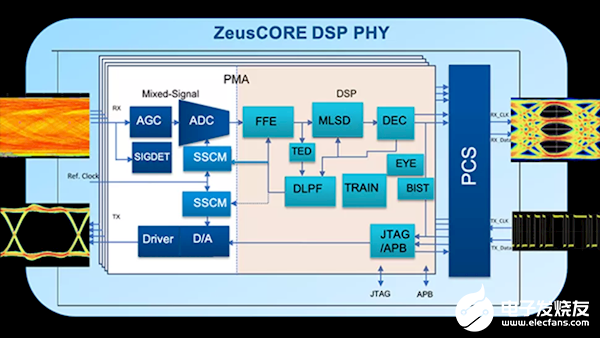

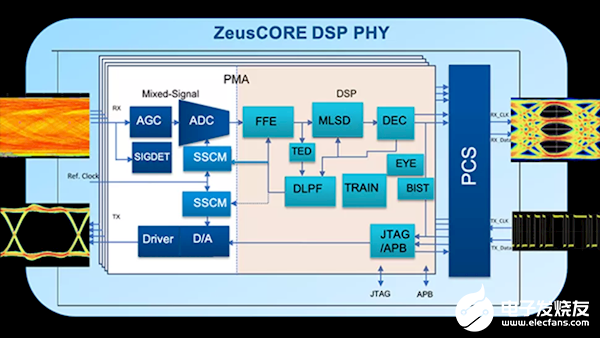

1780 日前,Alphawave公司宣布,其成为台积电N3E工艺首批流片的客户。相关产品会在本周晚些时候的台积电OIP论坛上公布详情。 据悉,这是一款DSP PHY串行控制芯片,IP核

2022-10-27 10:03:56 2099

2099

,纳斯达克股票代码:SNPS )近日宣布,得益于与台积公司的长期合作,新思科技针对台积公司N3E工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的

2022-11-08 13:37:19 1951

1951 3E工艺技术取得了多项关键成就,共同推动先进工艺节点的持续创新。新思科技经产品验证的数字和定制设计流程已在台积公司N3E工艺上获得认证。此外,该流程和新思科技广泛的基础IP、接口IP组合已经在台积公司N3E工艺上实现了多项成功流片,助力合

2022-11-10 11:15:22 1158

1158 为满足客户对异构计算密集型应用的复杂要求,新思科技(Synopsys,Inc.,纳斯达克股票代码:SNPS)近日宣布,推出业界领先的全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N

2022-11-16 16:25:43 1653

1653 新思科技(Synopsys, Inc.)近日宣布,推出全面EDA和IP解决方案,面向采用了台积公司先进N7、N5和N3工艺技术的2D/2.5D/3D多裸晶芯片系统。基于与台积公司在

2022-12-01 14:10:19 991

991 )设计流程是双方合作中的亮点之一 新思科技(Synopsys)近日宣布,连续第12年被评选为“台积公司OIP开放创新平台年度合作伙伴”(OIP,Open Innovation Platform)并斩获六个奖项,充分彰显了双方长期合作在 多裸晶芯片系统、 加速高质量接口IP、射频设计、云解决方案

2022-12-14 18:45:02 1339

1339 摘要: 新思科技连续12年被评为“台积公司OIP年度合作伙伴” 该合作推动了多裸晶芯片系统的发展和先进节点设计 奖项涵盖数字和定制设计、IP、以及基于云的解决方案 推出毫米波(mmWave)射频

2022-12-15 10:48:45 542

542

的先进设计。另一款 CPU 设计采用 AI 赋能的 Cadence Cerebrus Intelligent Chip Explorer 和完整的数字设计流程,借助台积电 N5 制程工艺,成功让功耗降低 8%,设计面积缩小 9%,同时显著提升了工程效率。

2023-02-06 15:02:48 2008

2008 屡获殊荣的新思科技DSO.ai解决方案通过大幅提高芯片设计效率、性能和云端扩展性,助力客户实现新突破 摘要: 新思科技携手芯片设计生态系统,通过DSO.ai率先实现100次流片,覆盖一系列前沿

2023-02-10 10:56:07 721

721 新 思科 技携手芯片设计生态系统,通过DSO.ai率先实现100 次流片,覆盖一系列前沿应用和不同先进工艺节点 意法半导体首次使用云端人工智能设计实现流片,通过DSO.ai以3倍的设计效率达成更高

2023-02-14 15:15:04 1359

1359 来源:Cadence楷登 2023年4月26日,楷登电子近日宣布基于台积电 3nm(N3E)工艺技术的 Cadence® 16G UCIe™ 2.5D 先进封装 IP 成功流片。该 IP 采用台积电

2023-04-27 16:35:40 1377

1377

该 IP 采用台积电 3DFabric™ CoWoS-S 硅中介层技术实现,可提供超高的带宽密度、高效的低功耗性能和卓越的低延迟

2023-04-28 15:14:12 1709

1709 股票代码:SNPS)近日宣布,携手台积公司和Ansys持续加强多裸晶芯片系统设计与制造方面的合作,助力加速异构芯片集成以实现下一阶段的系统可扩展性和功能。得益于与台积公司在3DFabric™技术和3Dblox™标准中的合作,新思科技能够为台积公司先进的7纳米、5纳米和3纳米工艺技

2023-05-17 15:43:06 450

450 新思科技(Synopsys, Inc.)近日宣布,携手台积公司和Ansys持续加强多裸晶芯片系统设计与制造方面的合作,助力加速异构芯片集成以实现下一阶段的系统可扩展性和功能。得益于与台积公司在

2023-05-18 16:04:08 1365

1365 集成以实现下一阶段的系统可扩展性和功能。得益于与台积公司在3DFabric技术和3Dblox标准中的合作,新思科技能够为台积公司先进的7纳米、5纳米和3纳米工艺技术上的多裸晶芯片系统设计,提供业界领先的全方位EDA和IP解决方案。台积公司先进工

2023-05-22 22:25:02 875

875

新思科技一直与台积公司保持合作,利用台积公司先进的FinFET工艺提供高质量的IP。近日,新思科技宣布在台积公司的N3E工艺上成功完成了Universal Chiplet Interconnect

2023-05-25 06:05:02 1446

1446 Labs实现光学DSP SoC设计的一次性流片成功。2021年,Banias Labs采用了新思科技的IP,以充分利用该IP在低延迟、传输长度灵活性、以及在5纳米工艺技术上的成熟度等方面的技术

2023-06-19 18:05:01 642

642

的“耳目”。 新思科技一直走在芯片监控解决方案的前沿,而这些解决方案是新思科技芯片生命周期管理(SLM)系列的一部分。最近, 新思科技在台积公司N5和N3E工艺上完成了PVT监控IP测试芯片的流片 。这是一个里程碑式的成功。从此,那些准备在这些先进节点

2023-07-11 17:40:01 1828

1828 基于台积公司N3E工艺技术的新思科技IP能够为希望降低集成风险并加快首次流片成功的芯片制造商建立竞争优势

2023-08-24 17:37:47 1737

1737 MediaTek 与台积公司今日共同宣布,MediaTek 首款采用台积公司 3 纳米制程生产的天玑旗舰芯片开发进度十分顺利,日前已成功流片,预计将在明年量产。MediaTek 与台积公司

2023-09-07 09:30:01 868

868

2023 年9月7日 – MediaTek与台积公司今日共同宣布,MediaTek首款采用台积公司3纳米制程生产的天玑旗舰芯片开发进度十分顺利,日前已成功流片,预计将在明年量产。MediaTek

2023-09-07 10:14:48 611

611 已成功流片。 3NM制程天玑旗舰芯片量产时间预计在2024年,2024年下半年会正式上市。业内估计3NM的MediaTek旗舰芯片型号应该不是今年上市的天玑9300,天玑9300可能采用的是台积电

2023-09-08 12:36:13 2932

2932 内容提要 ● 经过验证的接口 IP,可显著提升 TSMC N3E 制程节点的性能和能效 ● 224G-LR SerDes PHY IP 在 TSMC N3E 制程上实现一次性流片成功

2023-09-26 10:10:01 1655

1655 苹果已经发布了基于台积电3nm制程的A17 Pro处理器。最近,有消息称,高通的下一代5G旗舰芯片也将采用台积电3nm制程,并预计会在10月下旬公布,成为台积电3nm制程的第三个客户,可能是高通骁龙8 Gen3。

2023-09-26 16:51:31 2546

2546 《半导体芯科技》编译 来源:EENEWS EUROPE 新思科技(Synopsys)表示,其客户已在台积电2nm工艺上流片了多款芯片,同时对模拟和数字设计流程进行了认证。 新思科技表示,台积电2nm

2023-10-08 16:49:24 930

930 多个设计流程在台积公司N2工艺上成功完成测试流片;多款IP产品已进入开发进程,不断加快产品上市时间 摘要: 新思科技经认证的数字和模拟设计流程可提高高性能计算、移动和AI芯片的产品质量

2023-10-19 11:44:22 918

918 作为Synopsys.ai EDA整体解决方案的一部分,由AI驱动的模拟设计迁移流可助力提升模拟和混合信号 SoC 的设计生产率 摘要 : 新思科技AI驱动的设计解决方案可实现电路优化,在提高

2023-10-24 11:41:37 962

962 新思科技近日宣布,其数字和定制/模拟设计流程已通过台积公司N2工艺技术认证,能够帮助采用先进工艺节点的SoC实现更快、更高质量的交付。新思科技这两类芯片设计流程的发展势头强劲,其中数字设计流程已实现

2023-10-24 16:42:06 1394

1394 新思科技(Synopsys, Inc.)近日宣布,面向台积公司N5A工艺推出业界领先的广泛车规级接口IP和基础IP产品组合,携手台积公司推动下一代“软件定义汽车”发展,满足汽车系统级芯片(SoC)的长期可靠性和高性能计算需求。

2023-10-24 17:24:56 1694

1694 和 M-PHY ,以及 USB IP 产品都遵循了 TSMC N5A 工艺领先的车载等级设计规则。 新思科技宣布面向台积公司N5A工艺推出业界领先的广泛车规级接口IP和基

2023-10-31 09:18:44 1918

1918 、汽车和高性能计算设计的开发和硅片成功。在2023年台积公司北美OIP生态系统论坛上,新思科技展示的解决方案数量远超从前,进一步突显了新思科技与台积公司及其合作伙伴面向台积公司先进工艺和3DFabric技术的成熟解决方案方面的紧密合作。

2023-11-14 10:31:46 1202

1202 据悉,台积电近期发布的2023年报详述其先进制程与先进封装业务进展,包括N2、N3、N4、N5、N6e等工艺节点,以及SoIC CoW、CoWoS-R、InFO_S、InFO_M_PoP等封装技术。

2024-04-25 15:54:58 1797

1797 套件赋能可投产的数字和模拟设计流程能够针对台积公司N3/N3P和N2工艺,助力实现芯片设计成功,并加速模拟设计迁移。 新思科技物理验证解决方案已获得台积公司N3P和N2工艺技术认证,可加速全芯片物理签核。 新思科技3DIC Compiler和光子集成电路(PIC)解决方案与台

2024-05-11 11:03:49 695

695

新思科技EDA事业部战略与产品管理副总裁Sanjay Bali表示:“新思科技在可投产的EDA流程和支持3Dblox标准的3DIC Compiler光子集成方面的先进成果,结合我们广泛的IP产品组合,使得我们与台积公司能够助力开发者基于台积公司先进工艺加速下一代芯片设计创新。

2024-05-11 16:25:42 1016

1016 新思科技近日与台积公司宣布,在先进工艺节点设计领域开展了广泛的EDA和IP合作。双方的合作成果已经成功应用于一系列人工智能、高性能计算和移动设计领域,取得了显著成效。

2024-05-13 11:04:48 931

931 由Synopsys.ai EDA套件赋能可投产的数字和模拟设计流程能够针对台积公司N3/N3P和N2工艺,助力实现芯片设计成功,并加速模拟设计迁移。

2024-05-14 10:36:48 1197

1197

在近期举行的2024年欧洲技术研讨会上,台积电透露了即将用于HBM4制造的基础芯片的部分新信息。据悉,未来HBM4将采用逻辑制程生产,而台积电计划利用其N12和N5制程的改良版来完成这一任务。

2024-05-20 09:14:11 1792

1792 在近日举行的2024年欧洲技术研讨会上,台积电透露了关于HBM4基础芯片制造的新进展。据悉,未来HBM4将采用逻辑制程进行生产,台积电计划使用其N12和N5制程的改良版来完成这一任务。

2024-05-21 14:53:14 1442

1442 在半导体行业的最新动态中,台积电再次展示了其在制程技术和封装技术方面的领先地位。本周,台积电宣布其2nm制程工艺即将进入试产阶段,而苹果公司则独占了这一先进制程的首批产能,计划用于制造备受期待

2024-07-16 10:28:58 1698

1698 在半导体技术日新月异的今天,SK海力士再次引领行业潮流,宣布将采用台积电先进的N5工艺版基础裸片来构建其新一代HBM4内存。这一举措不仅标志着SK海力士在高性能存储解决方案领域的持续深耕,也预示着HBM内存技术即将迈入一个全新的发展阶段。

2024-07-18 09:47:53 1328

1328 据业界最新消息,AMD即将成为台积电位于美国亚利桑那州菲尼克斯附近的Fab 21工厂的第二大知名客户,该工厂已经开始试产包括N5、N5P、N4、N4P及N4X在内的一系列5nm节点制程。

2024-10-08 15:37:03 840

840 半导体技术领域的发展速度十分惊人,新思科技与台积公司(TSMC)始终处于行业领先地位,不断突破技术边界,推动芯片设计的创新与效率提升。我们与台积公司的长期合作催生了众多行业进步,从更精细的工艺节点到更高层次的系统集成,创造了无限可能。

2024-10-31 14:28:17 1022

1022 在音视频行业追求高画质、低延时、高效率的传输制作环境中,技术创新始终是驱动进步的核心力量。千视秉承“以用户为中心”的理念,再次从市场痛点出发,为用户提供更优质的解决方案。这一次,我们推出了针对N

2024-12-18 10:02:51 1679

1679

工艺——N3P。与前代工艺相比,N3P在性能上实现了约5%的提升,同时在功耗方面降低了5%至10%。这一显著的进步意味着,搭载M5芯片的设备将能够提供更强大的处理能力,同时拥有更出色的电池续航能力。 除了制程工艺的提升,苹果M5系列芯片还采用了台积电

2025-02-06 14:17:46 1313

1313 在分享中表示,OPPO工程师在折叠屏技术上取得了重大突破,成功解决了折叠屏手机普遍存在的折痕问题。为了实现这一目标,工程师们在Find N5的30个关键部件上采用了20种新材料,这些创新材料的应用使得Find N5在不牺牲耐用性的前提下,实现了无与伦比的轻薄设计。

2025-02-07 10:59:45 1067

1067 代号为“Venice”的新一代AMD EPYC CPU是首款基于台积电新一代N2制程的高性能计算产品。 AMD表示,其代号为“Venice”的新一代AMD EPYC™处理器是业界首款完成流片并

2025-05-06 14:46:20 637

637

新思科技近日宣布持续深化与台积公司的合作,为台积公司的先进工艺和先进封装技术提供可靠的EDA和IP解决方案,加速AI芯片设计和多芯片设计创新。

2025-05-27 17:00:55 1040

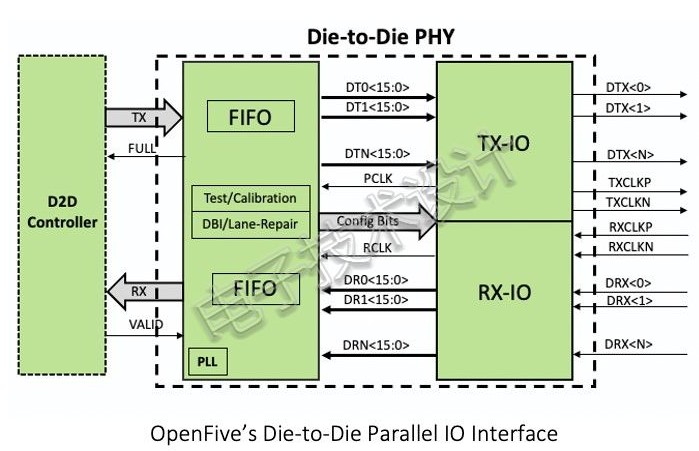

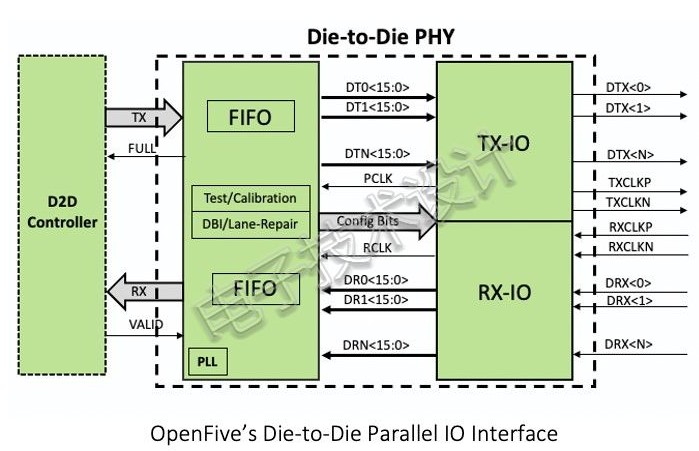

1040 我们很高兴展示基于台积电成熟 N4 工艺打造的 Gen1 UCIe IP 的 16GT/s 眼图。该 IP 一次流片成功且眼图清晰开阔,为寻求 Die-to-Die连接的客户再添新选择。

2025-08-25 16:48:05 1780

1780

MediaTek 今日宣布,MediaTek 首款采用台积电 2 纳米制程的旗舰系统单芯片(SoC)已成功完成设计流片(Tape out),成为首批采用该技术的公司之一,并预计明年底进入量产。双方

2025-09-16 16:40:31 978

978 给大家分享两个热点消息: 台积电2纳米N2制程吸引超15家客户 此前有媒体爆出苹果公司已经锁定了台积电2026年一半以上的2nm产能;而高通和联发科等其他客户难以获得足够多的台积电2nm制程的产能

2025-09-23 16:47:06 752

752 台积电2nm 制程试产成功 近日,晶圆代工龙头台积电(TSMC)正式宣布其2纳米制程技术试产成功,这一重大里程碑标志着全球半导体产业正式迈入全新的制程时代。随着试产工作的顺利推进,2纳米芯片距离量产

2025-10-16 15:48:27 1090

1090 还就面向TSMC-COUPE平台的AI辅助设计流程开展了合作。新思科技与台积公司共同赋能客户有效开展芯片设计,涵盖AI加速、高速通信和先进计算等一系列应用。

2025-10-21 10:11:05 434

434 新思科技近期宣布,其LPDDR6 IP已在台积公司 N2P 工艺成功流片,并完成初步功能验证。这一成果不仅巩固并强化了新思科技在先进工艺节点 IP 领域的领先地位,同时也为客户提供可信赖的、经硅片验证的IP选择,可满足移动通讯、边缘 AI 及高性能计算等更高存储带宽需求的应用场景。

2025-10-30 14:33:48 1873

1873

为推动小芯片创新的下一波浪潮,Cadence 成功流片其第三代通用小芯片互连技术(UCIe)IP 解决方案,在台积电先进的 N3P 工艺上实现了业界领先的每通道 64Gbps 速率。随着行业向日

2025-12-26 09:59:44 168

168

电子发烧友App

电子发烧友App

评论