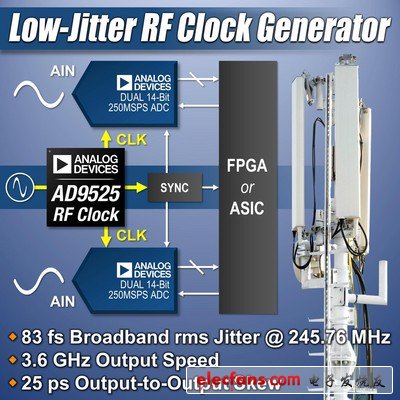

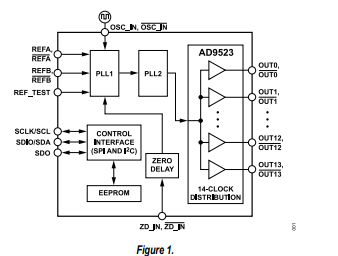

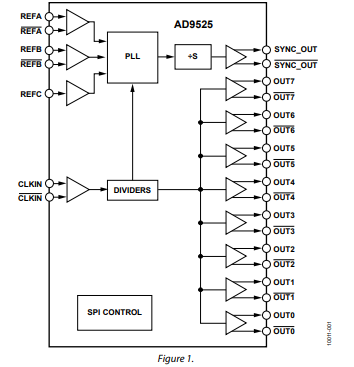

北京2012年11月2日电 /美通社/ -- Analog Devices, Inc. (NASDAQ: ADI) 全球领先的高性能信号处理解决方案供应商,最近推出一款具有业界最低抖动特性的 RF 时钟 IC(射频时钟集成电路)AD9525,适合要求高速数据转换和最佳信噪比 (SNR) 性能的通信和仪器设备应用。AD9525 RF 时钟IC在 245.76 MHz 时具有 83 fs(1 kHz 至 100 MHz 失调范围)的绝对宽带 rms(均方根)抖动,包括外部 VCO(压控振荡器)的抖动贡献。该新型 RF 时钟 IC 支持高达 3.6 GHz 的输出速度,比同类时钟快将近三倍。高速和低抖动的结合对于仪器仪表和防务电子应用尤为重要,此类应用需要极其干净的时钟合成来实现 GSPS(每秒数十亿的采样)范围的数据转换操作。

ADI推出RF时钟IC具有最佳抖动性能和最快输出速度

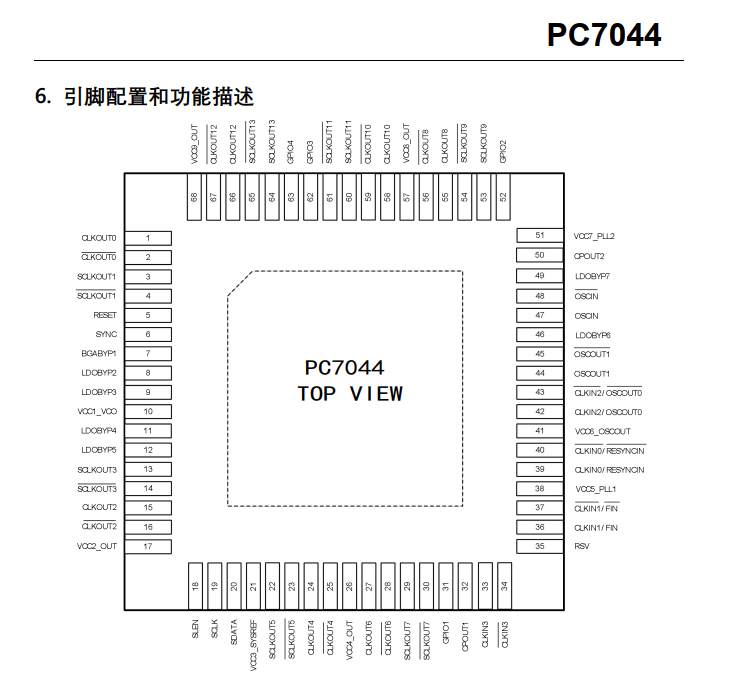

AD9525 RF 时钟 IC 的主要特性

RMS 抖动:

83 fs @ 245.76 MHZ(1 kHz至100 MHz)

46 fs @ 245.76 MHz(12 kHz至20 MHz)

最大输出速度:3.6 GHz

输出间偏斜:25 ps

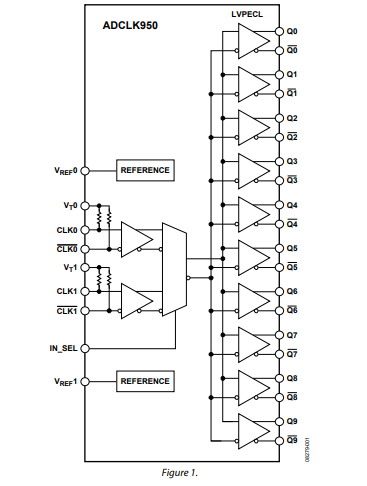

输出数:8个 LVPECL 和1个 LVPECL SYNC

电源电压:3.3 V

AD9525英文数据资料下载:AD9525英文数据手册

电子发烧友App

电子发烧友App

评论