Texas Instruments LMKDB1超低抖动时钟缓冲器是一系列超低抖动LP-HCSL缓冲器和MUX,支持PCIe Gen 1至Gen 6,符合DB2000QL标准。这些器件具有灵活的上电序列、故障安全输入、独立的输出启用和禁用引脚、输入信号丢失 (LOS) 检测和自动输出禁用功能,以及出色的电源噪声抑制性能。支持1.8V和3.3V两种电源电压。对于Texas Instruments LMKDB1120,与3.3V相比,1.8V电源可节省250mW功率。

数据手册:*附件:Texas Instruments LMKDB1超低抖动时钟缓冲器数据手册.pdf

特性

- LP-HCSL时钟缓冲器和时钟MUX支持

- PCIe Gen 1至Gen 6

- CC(通用时钟)和IR(独立参考)PCIe架构

- 带或不带SSC的输入时钟

- 符合 DB2000QL

- 所有设备均符合DB2000QL规范

- LMKDB1120引脚兼容DB2000QL

- 超低附加抖动:

- 156.25MHz时最大31fs 12kHz至20MHz RMS附加抖动

- PCIe Gen 4的最大附加抖动为13fs

- PCIe Gen 5的最大附加抖动为5fs

- PCIe Gen 6的最大附加抖动为3fs

- 故障安全输入

- 灵活的上电序列

- 自动输出禁用

- 单独输出使能

- 用于启用或禁用高速输出的SBI(边带接口

- LOS(信号丢失)输入检测

- 输出阻抗:85Ω或100Ω

- 电源:1.8V/3.3V (±10%)

- 环境温度范围:-40 °C至105 °C

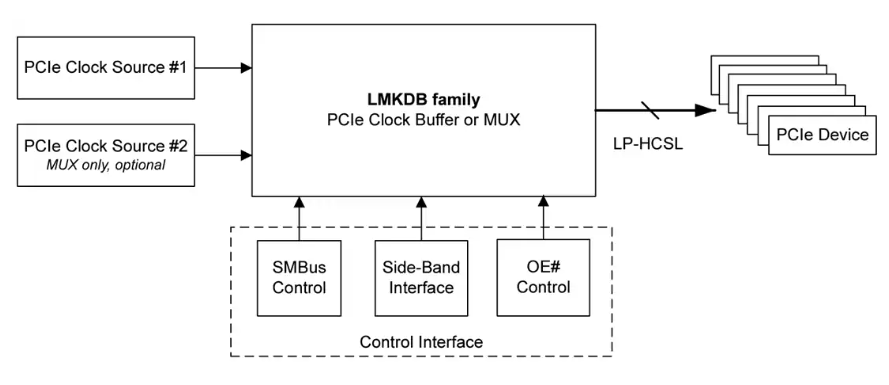

典型应用

德州仪器LMKDB11xx超低抖动时钟缓冲器技术解析

概述

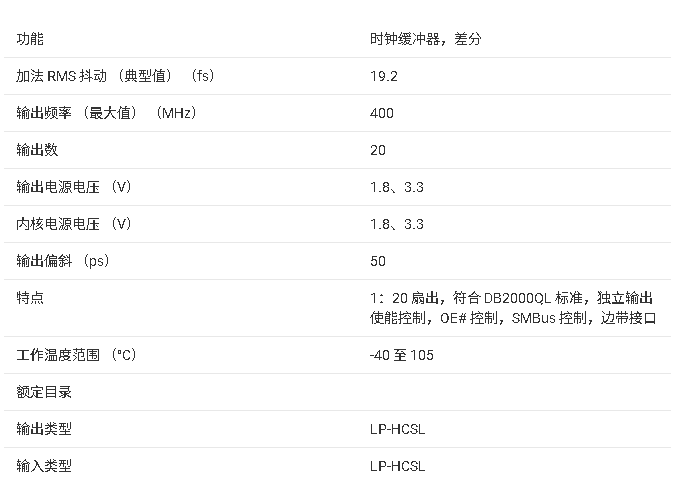

德州仪器(TI)的LMKDB11xx系列是专为PCIe Gen 1至Gen 7应用设计的超低抖动LP-HCSL时钟缓冲器家族,符合DB2000QL规范。该系列产品在高性能计算、服务器主板、NIC/SmartNIC和硬件加速器等领域有广泛应用。其主要特点包括极低的附加抖动、灵活的电源上电序列、故障安全输入/输出、独立输出使能控制等。

关键特性

超低抖动性能

- PCIe Gen 5附加抖动:仅5fs(最大值)

- PCIe Gen 6附加抖动:仅3fs(最大值)

- PCIe Gen 7附加抖动:仅2.1fs(最大值)

- 156.25MHz下12kHz-20MHz RMS附加抖动:31fs(最大值)

灵活配置选项

- 支持1.8V和3.3V双电源电压

- 85Ω或100Ω可编程输出阻抗(LMKDB1102)

- 可编程输出摆幅(600mV至975mV,25mV/步进)

- 可编程输出斜率(16种可选设置)

系统可靠性

- 故障安全输入(所有型号)

- 故障安全输出(带"FS"后缀型号)

- 自动输出禁用功能

- 输入信号丢失检测(LOS)

产品系列与选型

LMKDB11xx系列包含多种型号,主要区分如下:

| 型号 | 输出数量 | 封装尺寸 | 特殊功能 |

|---|---|---|---|

| LMKDB1120/FS | 20 | 6mm×6mm (NPP) | 故障安全输出(FS型号) |

| LMKDB1108/FS | 8 | 5mm×5mm (RKP) | 故障安全输出(FS型号) |

| LMKDB1104/FS | 4 | 4mm×4mm (REX) | 故障安全输出(FS型号) |

| LMKDB1102 | 2 | 3mm×3mm (REY) | 可编程输出阻抗 |

应用设计要点

电源设计

布局建议

时钟输入配置

支持四种输入配置方式:

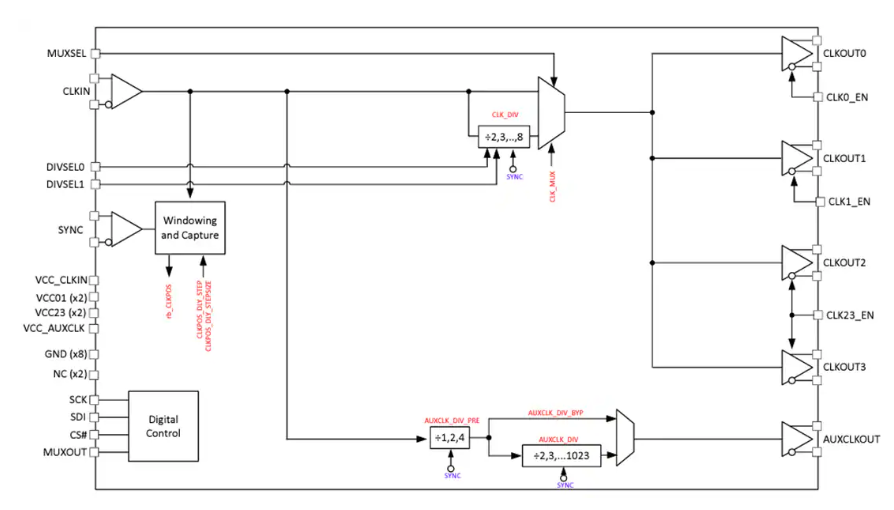

控制接口

LMKDB11xx提供三种控制方式,可同时使用:

1. SMBus模式

- 通过SMB_DATA和SMB_CLK引脚进行寄存器读写

- 支持块读写操作

- 可配置器件地址(通过SADR1和SADR0引脚设置)

2. 边带接口(SBI)模式

- 3线或4线串行接口(SHFT_LD#、SBI_IN、SBI_CLK和可选的SBI_OUT)

- 比SMBus更快的输出使能/禁用速度(最高25MHz)

- 支持星型和菊花链拓扑

3. 引脚模式

- 通过专用OE#引脚直接控制输出使能

- 当不使用SMBus或SBI时,相关引脚可悬空

典型应用示例

PCIe时钟分配系统:

- 输入:100MHz PCIe时钟源

- 输出:15路PCIe Gen5时钟

- 选用LMKDB1120(20输出)

- 计算抖动预算:sqrt(50² - 45²) = 21fs

- 器件实际附加抖动:13fs(满足要求)

以太网时钟分配系统:

- 输入:156.25MHz以太网时钟

- 输出:7路以太网时钟

- 选用LMKDB1108(8输出)

- 计算抖动预算:sqrt(100² - 90²) = 43fs

- 器件实际附加抖动:31fs(满足要求)

-

时钟缓冲器

+关注

关注

2文章

221浏览量

51801 -

Mux

+关注

关注

0文章

44浏览量

24033 -

低抖动

+关注

关注

0文章

46浏览量

5987

发布评论请先 登录

测量时钟缓冲器的附加抖动

TI推出正弦至正弦波时钟缓冲器

德州仪器推出超低噪声底限及附加抖动时钟缓冲器

LMK0033x:最低抖动的PCIe时钟扇形缓冲器

LMKDB1120和LMKDB1108超低抖动PCIe第1代到第6代LP-HCSL时钟缓冲器数据表

德州仪器LMX1214射频缓冲器与分频器技术解析

LMKDB11xx系列PCIe时钟缓冲器技术文档总结

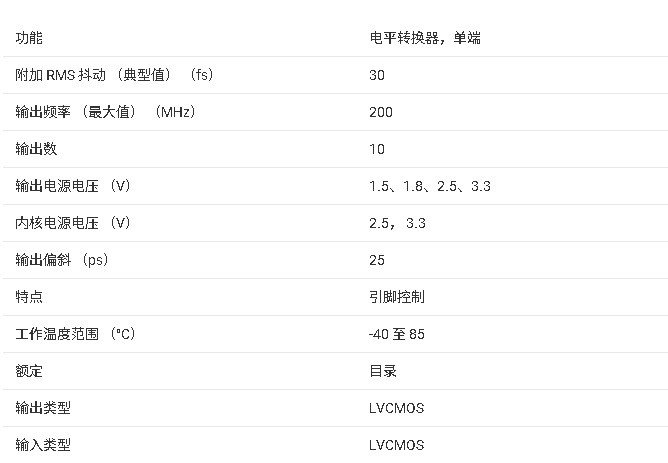

LMK00101 超低抖动LVCMOS扇出缓冲器/电平转换器技术手册

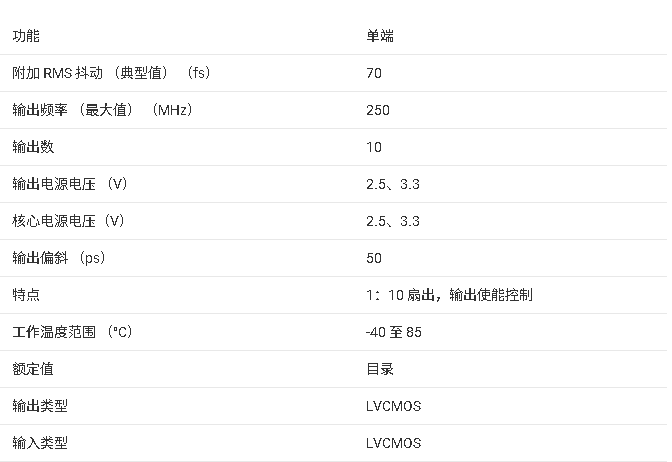

CDCLVC1110 低抖动、1:10 LVCMOS 扇出时钟缓冲器技术手册

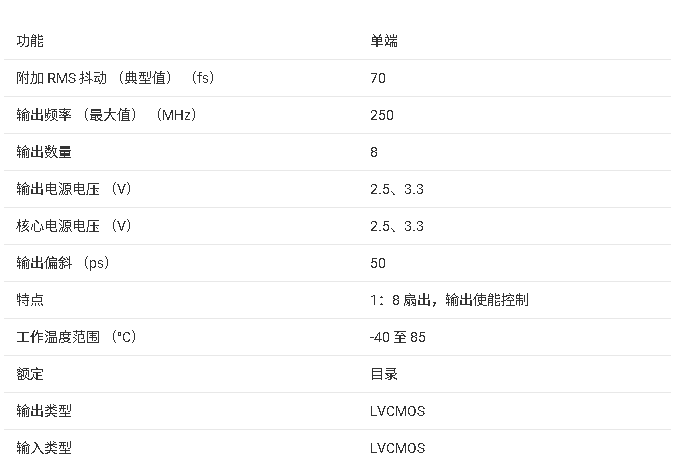

CDCLVC1108 低抖动、1:8 LVCMOS 扇出时钟缓冲器技术手册

德州仪器LMKDB11xx超低抖动时钟缓冲器技术解析

德州仪器LMKDB11xx超低抖动时钟缓冲器技术解析

评论