该CDCM61002是一款高度通用的低抖动频率合成器,可从低频晶体或LVCMOS输入生成两个低抖动时钟输出,可在低压正发射极耦合逻辑(LVPECL)、低压差分信号(LVDS)或低压互补金属氧化物半导体(LVCMOS)输出之间进行选择,适用于各种有线和数据通信应用。该CDCM61002具有板载PLL,只需通过控制引脚即可轻松配置。整体输出随机抖动性能小于 1ps、RMS(从 10 kHz 到 20 MHz),使该器件成为 SONET、以太网、光纤通道和 SAN 等要求苛刻应用的完美选择。该CDCM61002采用小型32引脚、5mm×5mm QFN封装。

*附件:cdcm61002.pdf

该CDCM61002是一款高性能、低相位噪声、全集成压控振荡器(VCO)时钟合成器,具有两个通用输出缓冲器,可配置为与LVPECL、LVDS或LVCMOS兼容。每个通用输出也可以转换为两个LVCMOS输出。此外,LVCMOS 旁路输出时钟可在输出配置中提供,有助于晶体负载,以实现精确所需的输入频率。它有一个完全集成、低噪声、基于LC的VCO,工作频率范围为1.75 GHz至2.05 GHz。

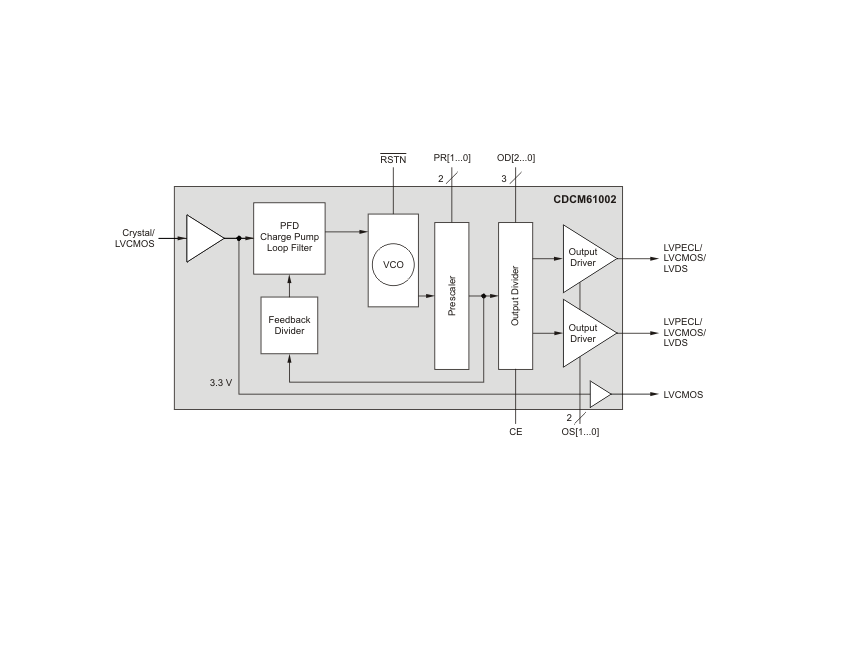

锁相环 (PLL) 使 VCO 相对于输入同步,输入可以是低频晶体。输出共享一个来自VCO内核的输出分压器。所有器件设置都通过控制引脚结构进行管理,该结构有两个控制预分频器和反馈分频器的引脚,三个控制输出分频器的引脚,两个控制输出类型的引脚,以及一个控制输出使能的引脚。每当PLL设置(包括输入频率、预分频器分频器或反馈分频器)发生变化时,都必须通过Reset控制引脚发出复位(器件复位为低电平有效)。复位启动 PLL 重新校准过程以确保 PLL 锁定。当器件处于复位状态时,输出和分频关闭。

输出频率(f 外 )与输入时钟的频率成正比(f 在 ).反馈分频器、输出分频器和VCO频率集f外关于 f 在 .有关常见有线和数据通信应用程序的配置设置,请参阅。对于其他应用,用于计算所需输出所需的精确晶体振荡器频率。

通过使用控制引脚,可以从 1、2、3、4、6 或 8 中选择输出分压器。反馈分频器和预分频器分频器组合可以分别从 25 和 3、24 和 3、20 和 4 或 15 和 5 中进行选择,也可以使用控制引脚。显示了CDCM61002的高级框图。

该器件在3.3 V电源环境中工作,工作温度范围为–40°C至+85°C。

特性

- 一个晶体/LVCMOS基准输入,包括24.8832 MHz、25 MHz和

26.5625 MHz - 输入频率范围:21.875 MHz 至

28.47 MHz - 片上VCO工作频率范围为1.75 GHz至2.05 GHz

- 2 个输出可用:

- 引脚可选择 LVPECL、LVDS 或 2-LVCMOS;工作电压为 3.3 V

- 提供LVCMOS旁路输出

- 输出频率可通过单个输出分频器的 /1、/2、/3、/4、/6、/8 选择

- 支持常见的 LVPECL/LVDS 输出频率:

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

150 兆赫、155.52 兆赫、156.25 兆赫、159.375 兆赫、187.5 兆赫、200 兆赫、212.5 兆赫、

250 兆赫、311.04 兆赫、312.5 兆赫、622.08 兆赫、625 兆赫

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

- 支持常见的LVCMOS输出频率:

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

150 兆赫、155.52 兆赫、156.25 兆赫、159.375 兆赫、187.5 兆赫、200 兆赫、212.5 兆赫、

250 兆赫

- 62.5 兆赫、74.25 兆赫、75 兆赫、77.76 兆赫、100 兆赫、106.25 兆赫、125 兆赫、

- 输出频率范围:43.75 MHz 至 683.264 MHz

- 内部PLL环路带宽:400 kHz

- 高性能 PLL 内核:

- 相位噪声通常为–146 dBc/Hz,5 MHz失调,625 MHz LVPECL输出

- 随机抖动通常为 0.509 ps,RMS(10 kHz 至 20 MHz),适用于 625 MHz LVPECL 输出

- 输出占空比校正至 50% (± 5%)

- LVPECL输出上的低输出偏斜为20 ps

- 使用控制引脚进行分频器编程:

- 两个引脚,用于预分频器/反馈分频器

- 三个用于输出分压器的引脚

- 两个用于输出选择的引脚

- 提供芯片使能控制引脚

- 3.3V 内核和 I/O 电源

- 工业温度范围:–40°C 至 +85°C

- 5mm × 5mm、32引脚、QFN (RHB) 封装

- ESD 保护超过 2 kV (HBM)

参数

方框图

1. 产品概述

CDCM61002是德州仪器(TI)推出的高性能、低抖动时钟发生器,集成电压控制振荡器(VCO),支持多种输出配置(LVPECL/LVDS/LVCMOS)。主要特性包括:

- 输入频率范围:21.875 MHz至28.47 MHz(支持晶体/LVCMOS参考输入)。

- VCO频率范围:1.75 GHz至2.05 GHz。

- 输出频率范围:43.75 MHz至683.264 MHz(通过分频器可调)。

- 低抖动性能:随机抖动典型值0.509 ps(RMS,10 kHz–20 MHz)。

- 输出类型:2路可配置输出(LVPECL/LVDS/2-LVCMOS)和1路LVCMOS旁路输出。

2. 关键特性

- 灵活配置:通过控制引脚设置分频比(/1至/8)、输出类型及使能状态。

- 低相位噪声:典型值-146 dBc/Hz(625 MHz LVPECL输出,5 MHz偏移)。

- 应用场景:SONET、以太网、光纤通道、SATA、HDTV等高速数据通信系统。

- 封装与工作条件:5 mm × 5 mm 32引脚QFN封装,工业级温度范围(-40°C至+85°C)。

3. 功能模块

- PLL核心:集成400 kHz带宽锁相环,支持快速锁定。

- VCO校准:上电或复位时自动校准,确保频率稳定性。

- 电源管理:3.3 V供电,内置LDO稳压器,需外接10 μF电容(REG_CAP1/2引脚)。

4. 设计注意事项

- 热管理:需将封装底部散热焊盘焊接至PCB以降低结温。

- 电源滤波:建议使用铁氧体磁珠隔离模拟与数字电源,减少噪声干扰。

- 输出端接:

- LVPECL:150 Ω终端电阻至VCC-2 V。

- LVDS:100 Ω差分终端。

- LVCMOS:串联22 Ω电阻匹配传输线阻抗。

5. 典型配置示例

- 输入25 MHz,输出312.5 MHz(LVPECL) :功耗约432.3 mW(含外部电阻损耗)。

- 输入26.5625 MHz,输出212.5 MHz(LVCMOS) :功耗约405.24 mW(驱动5 pF负载)。

6. 文档附加信息

结论

CDCM61002是一款高集成度、低抖动的时钟解决方案,适用于对时序要求严苛的通信和数据处理系统,其灵活的配置和优异的性能使其成为替代传统晶体振荡器的理想选择。

-

合成器

+关注

关注

0文章

314浏览量

27660 -

pll

+关注

关注

6文章

976浏览量

137568 -

数据通信

+关注

关注

2文章

504浏览量

34964 -

时钟发生器

+关注

关注

1文章

268浏览量

69876 -

LVCMOS

+关注

关注

1文章

142浏览量

11939

发布评论请先 登录

请问CDCM61002配置出来的时钟有偏差怎么解决?

评估低抖动PLL时钟发生器的电源噪声抑制性能

MAX3625B 抖动仅为0.36ps的PLL时钟发生器

评估低抖动PLL时钟发生器的电源噪声抑制

CDCM6208V2G具有小数分频器的2:8时钟发生器/抖动消除器数据表

CDCM61004四路输出、集成VCO、低抖动时钟发生器数据表

CDCM61002两路输出、集成VCO、低抖动时钟发生器数据表

CDCM9102低噪声双通道100MHz时钟发生器技术文档总结

CDCE62002 四输出时钟发生器/抖动清除器技术文档总结

CDCM61002 低抖动时钟发生器技术文档总结

CDCM61002 低抖动时钟发生器技术文档总结

评论