LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVPECL格式的低抖动时钟。

*附件:lmk04131.pdf

特性

- 级联 PLLatinum PLL 架构

- PLL1冗余基准输入信号丢失

检测自动和手动选择

基准时钟输入 - PLL2相位检测器速率高达100 MHz输入

倍频器集成VCO

- PLL1冗余基准输入信号丢失

- 输出

- LVPECL/2VPECL、LVDS 和

LVCMOS 格式 - 支持高达 1080 MHz 的时钟速率

- 五个专用通道分频器模块

- 支持的常见输出频率:

30.72 MHz、61.44 MHz、62.5 MHz、

74.25 MHz、75 MHz、77.76 MHz、100 MHz、

106.25 MHz、125 MHz、122.88 MHz、

150 MHz、155.52 MHz、156.25 MHz、159.375 MHz、

187.5 MHz、200 MHz、

212.5 MHz、245.76 MHz、250 MHz、311.04 MHz、

312.5 MHz、368.64 MHz、

491.52 MHz、622.08 MHz、625 MHz、983.04 MHz

- LVPECL/2VPECL、LVDS 和

- MICROWIRE (SPI) 编程接口

- 工业温度范围:–40 至 85 °C

- 3.15 V 至 3.45 V 工作电压

- 封装:48 引脚 WQFN(7.0 × 7.0 × 0.8 mm)

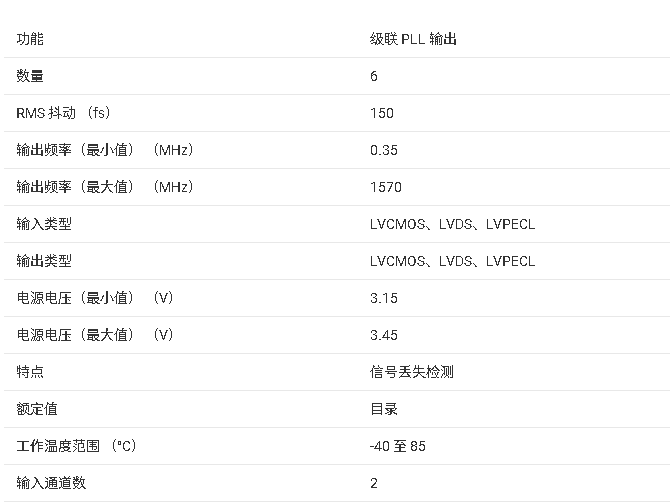

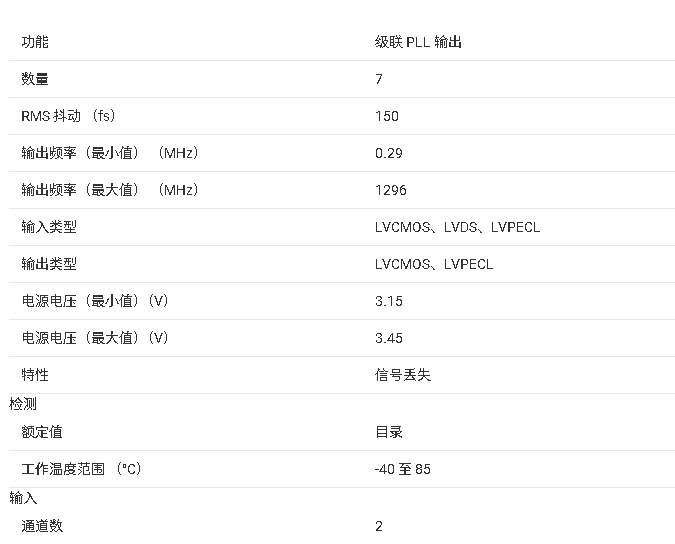

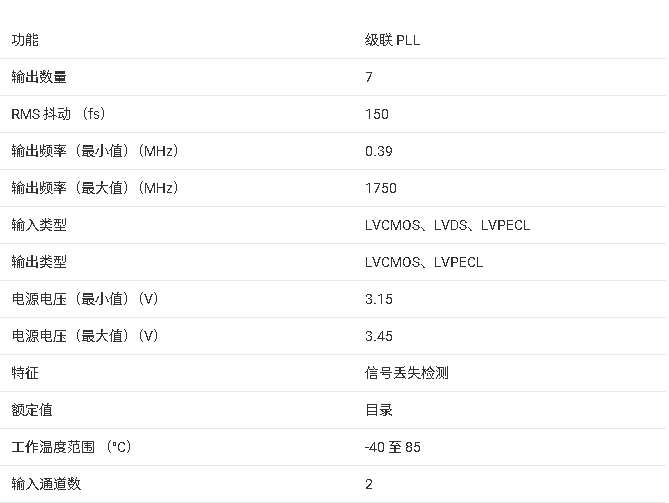

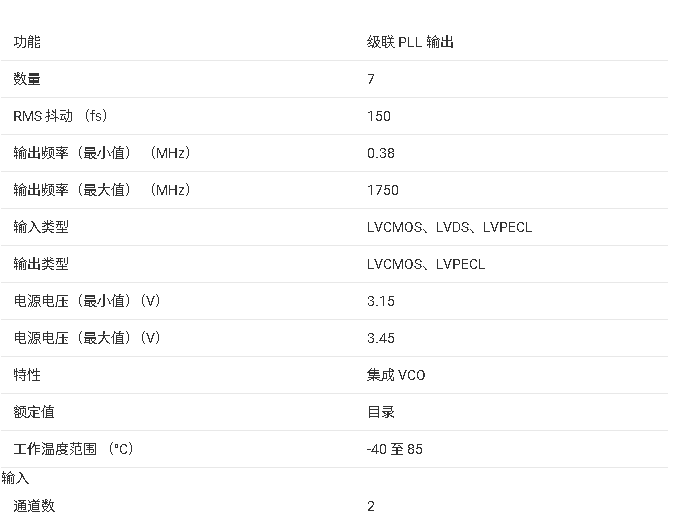

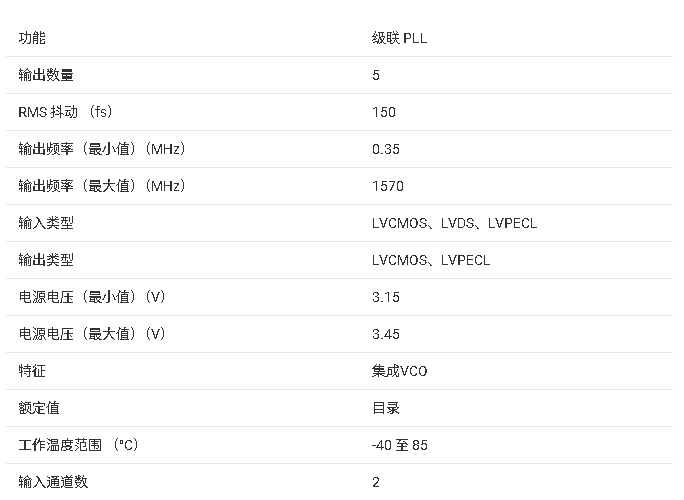

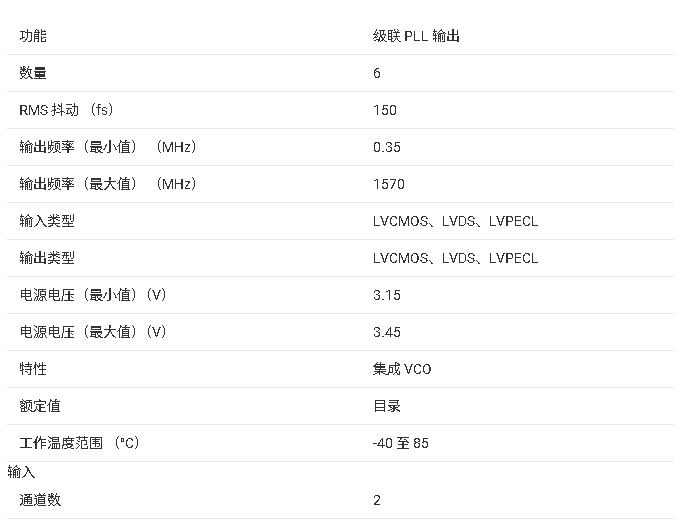

参数

方框图

1. 产品概述

LMK04100系列(含LMK04100/01/02/10/11/31/33)是德州仪器(TI)推出的精密时钟调理芯片,采用级联PLL架构,专为低抖动时钟生成、乘法及分配设计。核心特点包括:

- 双PLL架构:PLL1支持冗余参考输入(CLKin0/1)和信号丢失检测,PLL2集成VCO,相位检测速率达100MHz。

- 多格式输出:支持LVPECL/2VPECL、LVDS、LVCMOS格式,最高输出频率1080MHz,提供5通道可编程分频器。

- 应用场景:2G/3G/4G基站、高速ADC时钟、光传输网络、广播视频等。

2. 关键特性

- 输入灵活性:

- 输出配置:

- 每通道独立分频(2-510偶数分频)、同步控制(SYNC*引脚)。

- 可编程输出电平(如2VPECL模式提升摆幅至2Vpp)。

- 低抖动性能:

- 集成RMS抖动低至140fs(12kHz-20MHz带宽,122.88MHz输出)。

3. 功能模块详解

- PLL1:

- PLL2:

- 宽带宽(50-200kHz)频率合成,内置VCO(1185-2160MHz)。

- 集成3/4阶环路滤波器选项,支持频率倍增模式(EN_PLL2_REF2X)。

- 控制接口:

- MICROWIRE(SPI兼容)编程接口,32位寄存器配置。

4. 电气特性

- 工作电压:3.15-3.45V,工业温度范围(-40至85°C)。

- 功耗:典型值380-435mA(全输出使能),支持全局省电模式。

- 封装:48引脚WQFN(7x7mm),带裸露焊盘增强散热。

5. 设计支持

- 热管理:建议PCB布局采用多通孔连接接地层,θJA为27.4°C/W。

- 晶体振荡器设计:提供参考电路及负载电容计算指南(如12.288MHz晶体示例)。

- 扩展输出:可通过LVDS/LVPECL分路或级联LMK01000系列芯片实现。

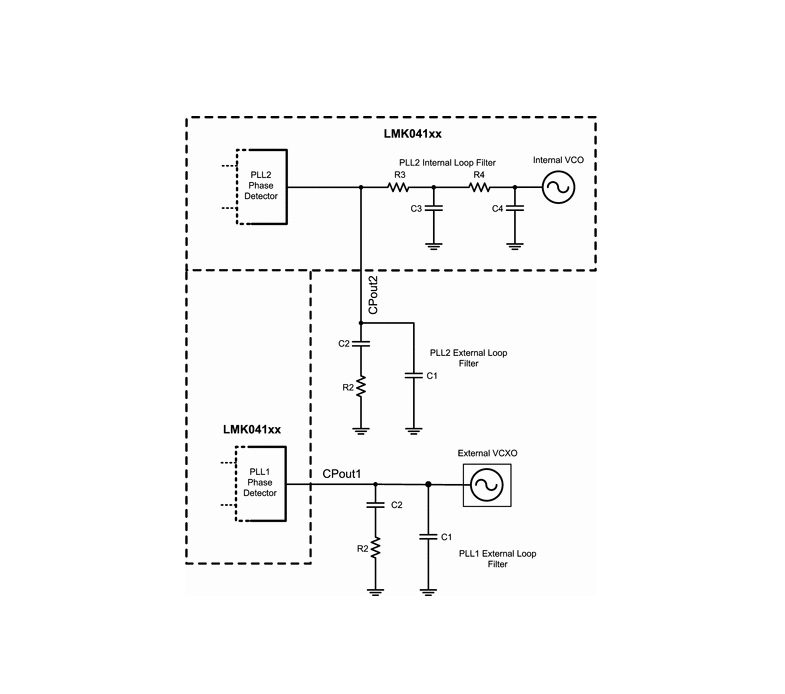

6. 典型应用图

- 外部VCXO通过PLL1锁定参考时钟,PLL2生成低抖动输出。

- 环路滤波器设计示例(如PLL2的R3=600Ω、C3=50pF)。

- 输出端推荐AC耦合(0.1μF电容)及匹配电阻(如LVPECL用120Ω)。

7. 文档结构

- 寄存器映射表(R0-R15)详细说明配置位域。

- 时序图(如uWire接口)、引脚描述及绝对最大额定值。

- 性能曲线(如VCO调谐灵敏度、相位噪声)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟

+关注

关注

11文章

1999浏览量

135228 -

调节器

+关注

关注

5文章

916浏览量

49631 -

清除器

+关注

关注

0文章

56浏览量

6112 -

LVCMOS

+关注

关注

1文章

142浏览量

12031

发布评论请先 登录

相关推荐

热点推荐

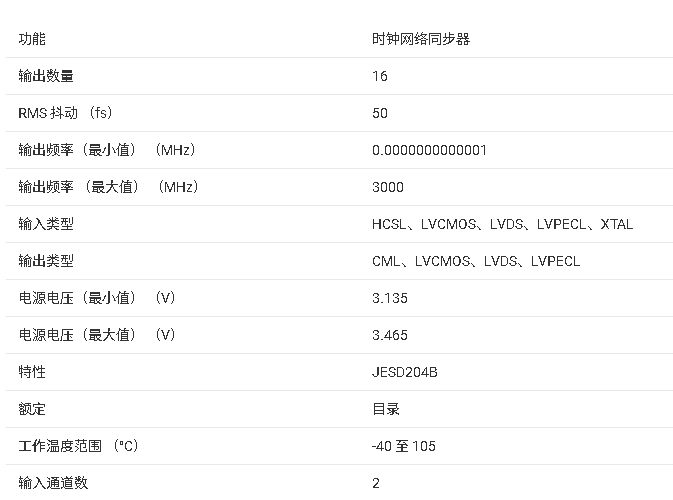

LMK04832-SP时钟抖动清除器

SYSREF分频器SYSREF时钟的25ps步进模拟延迟设备时钟和SYSREF的数字延迟和动态数字延迟PLL1的保持模式PLL1或PLL2的0延迟环境温度范围:–55°C至125°CLMK5C33216LMK04816LMK04808LMK04832-SPLMK04906LMK

发表于 03-24 16:13

LMK5C33216A 网络同步器与抖动清除器总结

LMK5C33216A是一款高性能网络同步器和抖动清除器,旨在满足无线通信和基础设施应用的严格要求。

该器件集成了三个 DPLL 和三个 APLL,通过可编程环路带宽 (LBW)

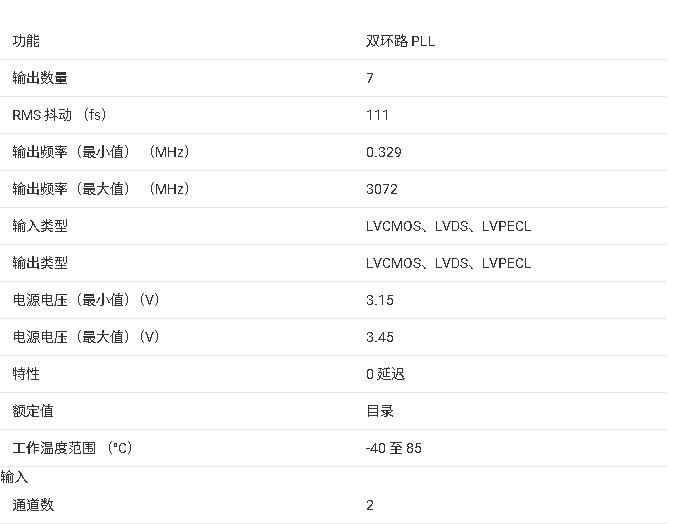

LMK04208低噪声时钟抖动清除器技术文档总结

LMK04208是一款高性能时钟调节器,具有卓越的时钟抖动清除功能, 生成和分发具有高级功能,以满足下一代系统要求。 双环路PLLatinum™架构能够 使用低噪声VCXO模块的RMS

LMK04100系列时钟抖动清除器技术文档总结

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVP

LMK04102 抖动清除器技术文档总结

LMK04100系列精密时钟调节器无需高性能VCXO模块即可提供抖动清除、时钟倍增和分配。

当连接到恢复的系统基准时钟和VCXO时,该器件可生成5个LVCMOS、LVDS或LVP

LMK5C33414A:高性能网络同步器与抖动清除器的深度剖析

LMK5C33414A:高性能网络同步器与抖动清除器的深度剖析 在无线通信和基础设施应用领域,时钟同步和抖动控制至关重要。TI推出的

低噪声时钟抖动清除器LMK04610:技术拆解与应用设计

低噪声时钟抖动清除器LMK04610:技术拆解与应用设计 在电子设备的世界里,时钟信号就如同心脏的跳动,稳定而精准的时钟对于各类系统的正常运行至关重要。今天,我们要深入探讨的就是一款在

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析 在电子设计领域,时钟信号的稳定性和低抖动对于系统性能至关重要。LMK0482x系

探索LMK04100系列时钟抖动清除器:特性、应用与设计要点

探索LMK04100系列时钟抖动清除器:特性、应用与设计要点 引言 在电子设计领域,时钟信号的稳定性和低抖动特性对于众多应用至关重要。德州仪器(TI)的

深入解析LMK04100系列时钟抖动清除器:从特性到应用

深入解析LMK04100系列时钟抖动清除器:从特性到应用 在电子设计领域,时钟信号的稳定性和低抖动对于系统性能至关重要。TI的LMK0410

LMK04000 系列低噪声时钟抖动清除器:功能、应用与设计指南

LMK04000 系列低噪声时钟抖动清除器:功能、应用与设计指南 在电子设计领域,时钟抖动的控制至关重要,它直接影响着系统的性能和稳定性。TI 的

LMK04131 抖动清除器技术文档总结

LMK04131 抖动清除器技术文档总结

评论