近日,核芯互联正式推出新一代高性能时钟抖动消除器——CLF7044。作为一款专为高速数据转换与精密时钟管理设计的核心器件,CLF7044在硬件架构、封装规格及关键性能指标上全面兼容行业标杆HMC7044,采用全国产化纯CMOS工艺设计,为通信基站、微波基带、波束成形、软件定义无线电等领域提供了无缝替代方案,助力客户在保持系统设计一致性的同时,实现性能升级与成本优化。

一、全兼容设计:无缝衔接HMC7044生态,降低迁移成本

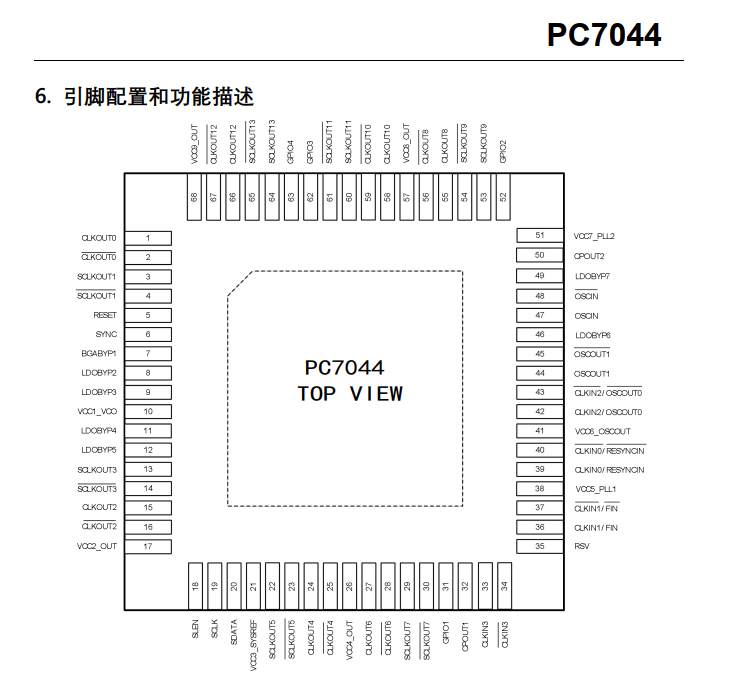

CLF7044采用与HMC7044完全一致的QFN68封装及引脚定义,支持即插即用式替换,无需重新设计PCB布局。在硬件兼容性上,其输入输出接口全面适配LVDS、LVPECL、CML等多种标准,支持4路差分/单端时钟输入与14路可配置时钟输出,完美兼容现有HMC7044系统的外围电路。

性能层面,CLF7044继承了HMC7044的核心优势并实现突破:

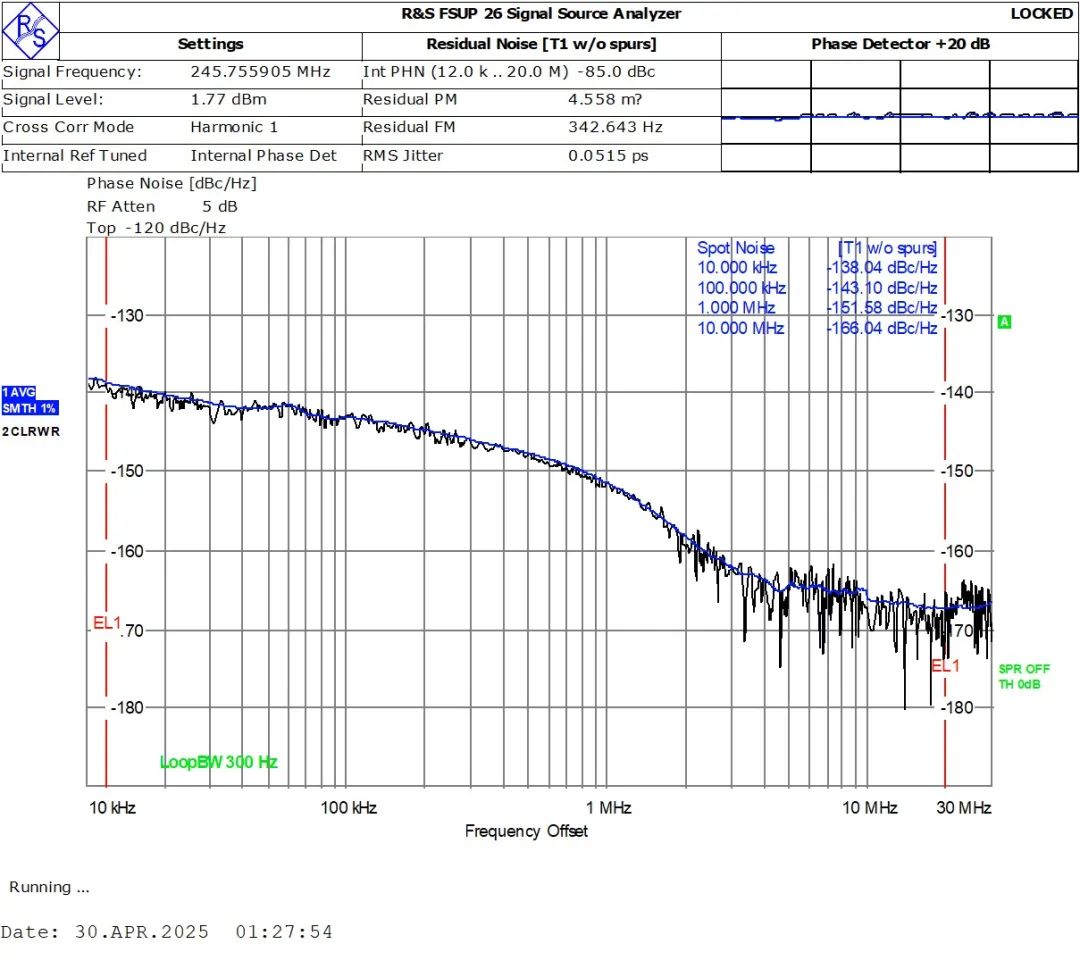

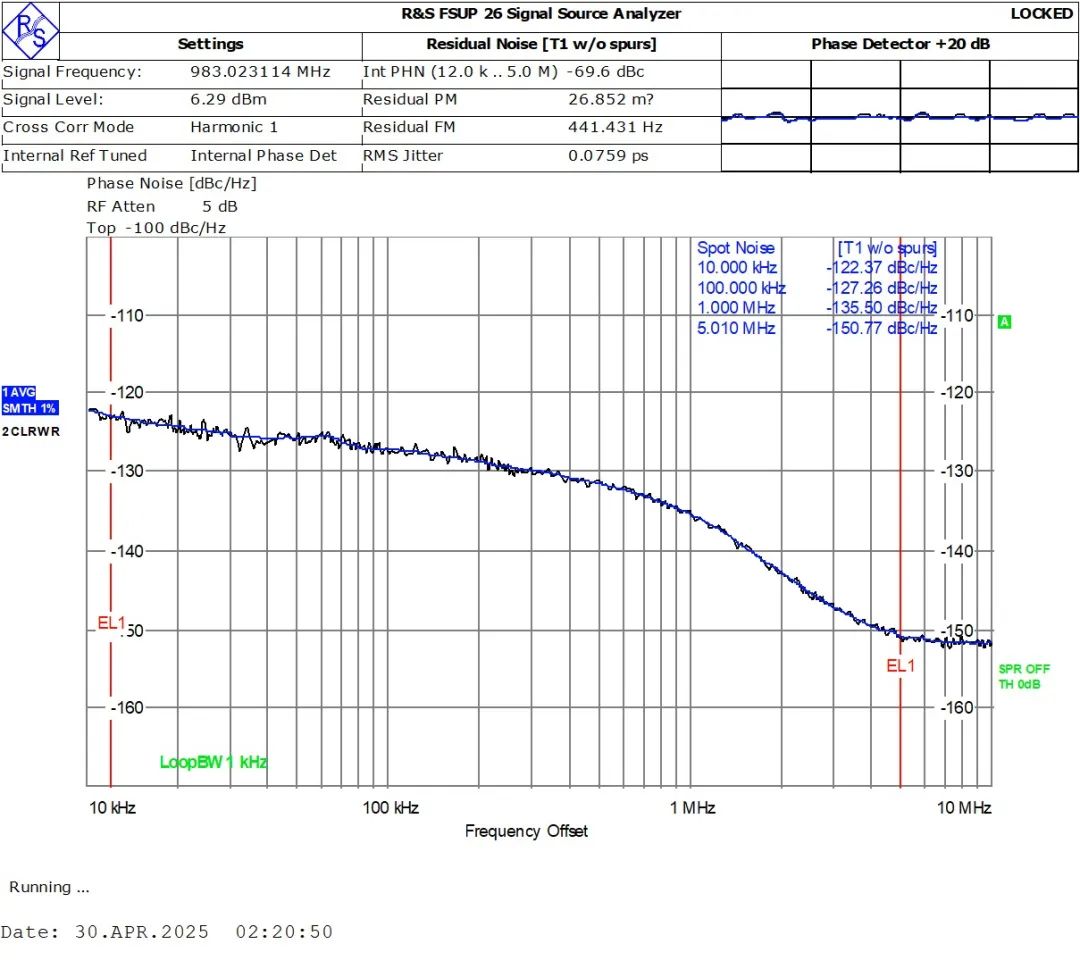

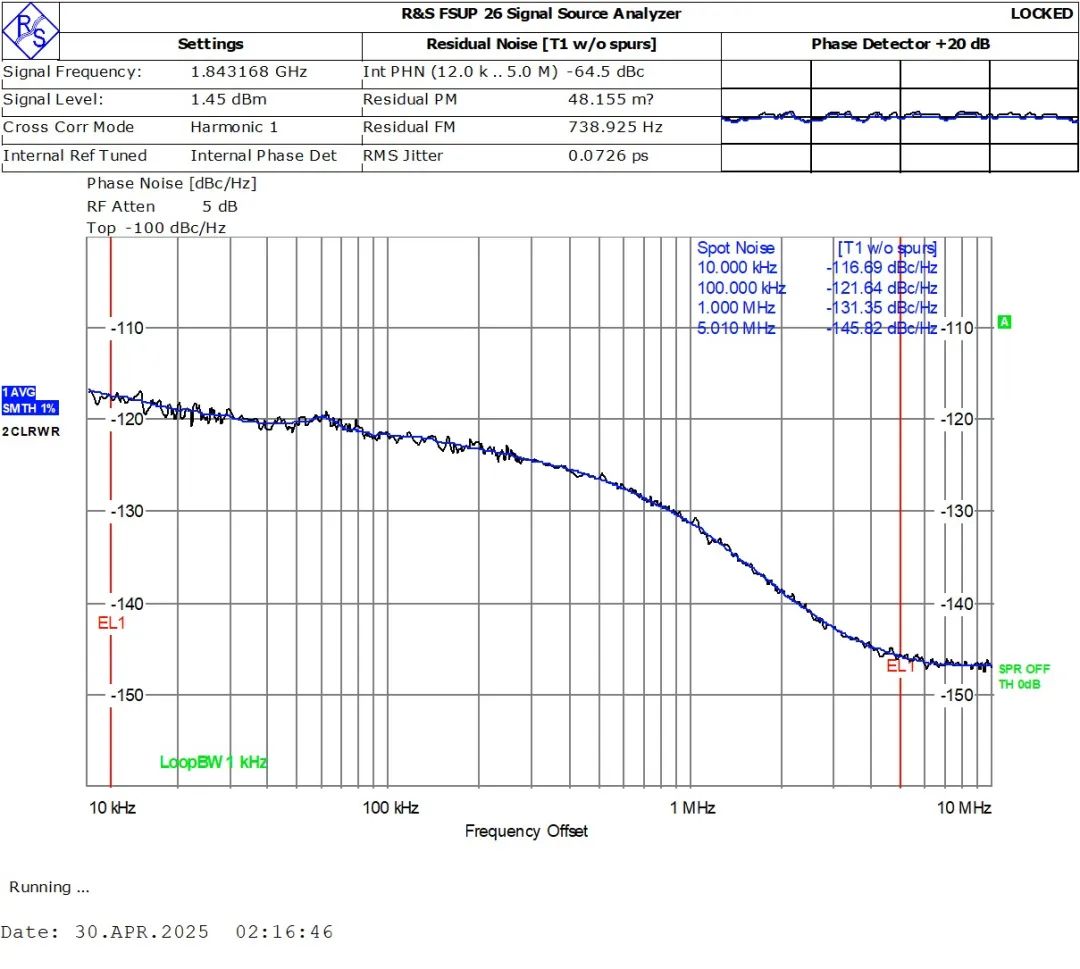

超低RMS抖动:在245.76 MHz频率下,12kHz-20MHz带宽内抖动低至51.5fs RMS,满足高精度数据转换器对参考时钟的严苛要求;

底噪性能:噪声基底达-161dBc/Hz,有效抑制相位噪声对信号链的干扰;

频率范围:支持最高3200MHz输出频率及宽范围VCO调谐,适配多代通信协议的频率需求。

对于正在使用HMC7044的客户,CLF7044只需要略微调整原有驱动代码与控制逻辑,即可通过SPI接口实现参数无缝迁移,大幅缩短产品迭代周期。

二、双环路架构:重构时钟管理灵活性与稳定性

CLF7044搭载双整数模式PLL及重叠片上VCO,构建了业界领先的时钟处理架构:

双环路协同优化:PLL1支持外部VCXO或低成本晶振输入,通过窄环路带宽实现抖动消除;PLL2可独立驱动14路输出,支持JESD204B系统参考时钟(SYSREF)脉冲生成,满足多通道数据转换器的同步需求。

智能延迟配置:每个输出通道支持25ps模拟延迟与½VCO周期数字延迟独立编程,精准调整时钟相位,解决高速系统中的时序对齐难题。

高可靠性设计:集成信号丢失(LOS)检测与无瞬断参考时钟切换功能,在主时钟失效时自动切换至备用源,确保系统连续运行;4路GPIO报警接口实时反馈设备状态,提升系统健康管理能力。

三、多场景适配:定义下一代时钟分配解决方案

CLF7044凭借卓越的性能与灵活性,成为复杂时钟树设计的理想选择:

5G/6G基站:支持多载波GSM、LTE、W-CDMA等蜂窝协议,为基带处理单元提供低抖动时钟,优化信号调制精度;

波束成形:14路低噪声输出可同步驱动多通道TR组件,25ps级延迟控制满足阵列天线的相位一致性要求;

高速数据转换:兼容JESD204B接口,为ADC/DAC提供洁净的参考时钟与SYSREF同步信号,提升高速采样系统的信噪比(SNR);

工业与仪器仪表:支持-40℃~85℃宽温工作范围及优秀的电源抑制比(PSRR),适应严苛环境下的高精度测量需求。

四、技术亮点:细节处见真章

功耗与性能平衡:通过SPI可编程相位噪声与功耗模式,用户可根据场景动态调整,在低功耗模式下电流消耗低至1mA(断电模式),兼顾能效与性能;

外部VCO支持:兼容最高3200MHz外部VCO输入,灵活扩展系统频率范围,适配定制化高频时钟需求;

保持模式(Holdover):在参考时钟丢失时维持输出频率稳定,频率精度达0.5ppm,保障通信系统在短暂信号中断时的连续性。

五、核芯互联:持续赋能国产替代

作为本土高性能时钟芯片的创新者,核芯互联始终聚焦高端集成电路设计,致力于为客户提供“高性能、高兼容、高可靠”的国产化解决方案。CLF7044的推出,通过用纯国产化CMOS工艺对HMC7044进行全兼容设计,为产业链上下游提供了无风险的替代路径,助力关键器件自主可控。

即日起,CLF7044样品及评估板已开放申请,欢迎致电核芯互联技术支持团队(唐路:18601296113)或访问官网(www.hexinhulian.com)获取详细资料。核芯互联期待与您携手,以精准时钟赋能下一代智能系统。

关于核芯互联

核芯互联是一家专注于信号链、高速接口、时钟管理及混合信号集成电路设计的高科技企业,产品广泛应用于通信基础设施、工业控制、数据中心等领域。公司坚持自主创新与开放合作相结合,致力于成为全球领先的模拟及混合信号芯片供应商。

-

时钟抖动

+关注

关注

1文章

68浏览量

16405 -

消除器

+关注

关注

0文章

59浏览量

9142 -

核芯互联

+关注

关注

0文章

40浏览量

2490

原文标题:核芯互联 CLF7044 高性能时钟抖动消除器正式发布:全面兼容 HMC7044

文章出处:【微信号:gh_0dbe96735e9d,微信公众号:核芯互联】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高性能时钟管理利器:HMC7044B深度解析

LMK04208 高性能时钟调节器:特性、应用与设计要点

广芯微推出新一代高性能Sub-GHz射频收发芯片UM2011A

广芯微推出新一代2x520W并网型微型逆变器参考开发平台

核芯互联推出新一代高性能时钟抖动消除器CLF7044

核芯互联推出新一代高性能时钟抖动消除器CLF7044

评论