该CDC7005是一款高性能、低相位噪声和低偏斜时钟同步器和抖动清除器,可将压控晶体振荡器(VCXO)频率与基准时钟同步。可编程预分频器 M 和 N 为参考时钟与 VCXO 的频率比提供了高度的灵活性:VCXO_IN/REF_IN = (NxP)/M。VCXO_IN时钟的工作频率高达 800 MHz。通过选择外部VCXO和环路滤波器组件,可以调整PLL环路带宽和阻尼因子,以满足不同的系统要求。五个差分LVPECL输出中的每一个都可通过串行外设接口(SPI)进行编程。SPI允许单独控制每个输出的频率和使能/禁用状态。该器件在 3.3V 环境中运行。内置锁存器确保所有输出同步。

该CDC7005的工作温度范围为 –40°C 至 85°C。

*附件:cdc7005.pdf

特性

- 高性能 1:5 PLL 时钟同步器

- 两个时钟输入:VCXO_IN时钟与REF_IN时钟同步

- 同步频率高达 800 MHz (VCXO_IN)

- 支持五个差分LVPECL输出

- 每个输出频率可通过 x1、/2、/4、/8 /16 进行选择

- 所有输出都是同步的

- 集成低噪声OPA,用于外部低通滤波器

- 低 PLL 环路带宽的高效抖动屏蔽

- 低相位噪声特性

- 相位调整的可编程延迟

- 预分流器环带宽调整

- SPI可控分频设置

- 上电控制强制LVPECL输出在VCC <1.5 V时为3态

- 3.3V 电源

- 采用 64 引脚 BGA(0.8 mm 间距 - ZVA)或 48 引脚 QFN (RGZ) 封装

- 工业温度范围 –40°C 至 85°C

参数

1. 产品概述

CDC7005是德州仪器(TI)推出的3.3V高性能时钟合成器与抖动清除器,专为高频时钟同步设计,具有以下核心特性:

- 同步功能:支持两路时钟输入(VCXO_IN与REF_IN),最高同步频率达800 MHz(VCXO_IN)。

- 输出配置:提供5路差分LVPECL输出,每路可通过SPI编程选择分频比(×1、/2、/4、/8、/16),输出相位噪声低且支持可调延迟。

- 集成组件:内置低噪声运算放大器(OPA)用于外部低通滤波器设计,支持灵活的环路带宽调整。

- 控制接口:SPI可编程接口,支持分频比、延迟、电荷泵电流等参数配置。

2. 关键特性

- 高性能PLL:支持频率比VCXO_IN/REF_IN = (N×P)/M,通过外部VCXO和滤波器组件可定制环路带宽。

- 低抖动与低偏斜:优化的相位噪声性能,输出偏斜低至30 ps(同频模式下)。

- 电源管理:3.3V供电,工业级温度范围(-40°C至85°C),支持上电输出三态保护。

3. 封装与引脚

- 封装选项:64引脚BGA(0.8 mm间距)或48引脚QFN(RGZ)。

- 关键引脚:

- 控制接口:CTRL_LE(SPI使能)、CTRL_CLK(时钟)、CTRL_DATA(数据)。

- 状态指示:STATUS_LOCK(锁相状态)、STATUS_REF/VCXO(输入时钟有效性)。

- 模拟接口:CP_OUT(电荷泵输出)、OPA_IN/OUT(运算放大器接口)。

4. 应用场景

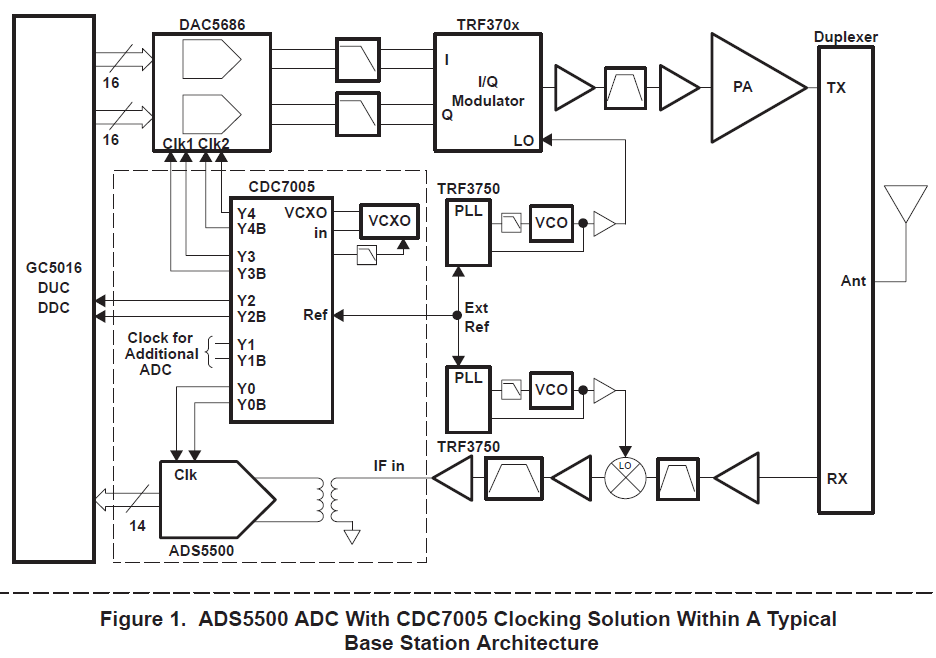

- 高速数据转换器时钟:如DAC5686等插值DAC的采样时钟生成,支持多路相位对齐输出(±200 ps偏斜)。

- 通信系统:3G基站中的时钟分配,支持245.76 MHz高频与61.44 MHz数据时钟同步。

5. 电气特性

- 相位噪声性能(典型值):

- 10 Hz: -105 dBc/Hz

- 100 kHz: -152 dBc/Hz

- 功耗:全输出激活时典型电流265 mA(3.6V供电)。

6. 设计支持

- 参考电路:提供被动环路滤波器设计示例(如图7),优化相位噪声与稳定性。

- 文档扩展:参考应用笔记SCAA067获取VCXO选型与相位噪声测试数据。

7. 注意事项

- 热管理:需确保封装散热焊盘接地,BGA封装热阻54°C/W(无气流)。

- SPI时序:严格遵循CTRL_LE/CLK/DATA的建立/保持时间(详见图1时序图)。

本文档完整覆盖CDC7005的功能、配置、电气参数及典型应用,适用于高频时钟系统的硬件设计参考。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

分频器

+关注

关注

43文章

537浏览量

53758 -

时钟

+关注

关注

11文章

1999浏览量

135239 -

晶体振荡器

+关注

关注

9文章

752浏览量

33426 -

清除器

+关注

关注

0文章

56浏览量

6112 -

同步器

+关注

关注

1文章

117浏览量

15701

发布评论请先 登录

相关推荐

热点推荐

能有效降低高速网络误码率的超低抖动时钟合成器

为了应对日益紧缩的时钟抖动预算,麦瑞半导体(Micrel, Inc)已推出两个全新系列的ClockWorks超低抖动时钟合成器,能够满足这些

详解频率合成器高性能架构的实现

)可以极大地促进高性能架构的实现。大部分高频系统都使用传统的基于整数分频器的设计(图1)或基于分数N分频器的设计。不管是使用哪种设计,联合使用单个通用频率合成器IC和一个外部压控振荡

发表于 07-08 06:10

超低抖动时钟合成器的设计挑战

摘要:该应用笔记提出了超低抖动时钟合成器的一种设计思路,其目标是产生2GHz时钟时,边沿之间的抖动< 100fs。分析和仿真结果表明,要达到

发表于 04-25 09:54

•691次阅读

限制性试剂影响ADC的信噪比性能和CDC7005与ADS5500的比较详细概述

TI公司引进了一套适合于高速、高中频采样ADC设备的设备,如ADS5500 ADC,能够在125MSPS下进行采样。为了实现这些高性能器件的全部潜力,必须提供一种极低的相位噪声时钟源。CDC7005

发表于 05-18 11:07

•4次下载

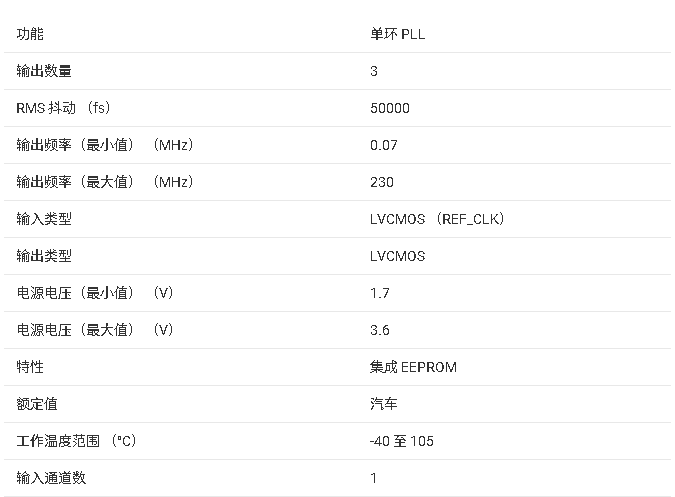

CDCE813-Q1 可编程时钟合成器与抖动清除器技术文档总结

CDCE813-Q1器件是一款基于锁相环(PLL)的模块化、低成本、高性能、可编程时钟合成器。它们从单个输入频率生成多达三个输出时钟。每个输出都可以使用集成的可配置PLL在系统内针对高

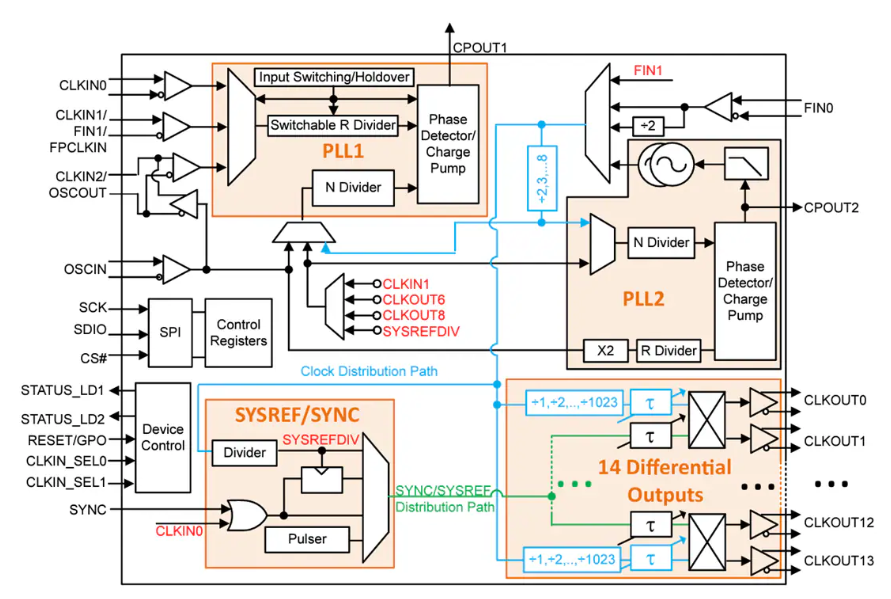

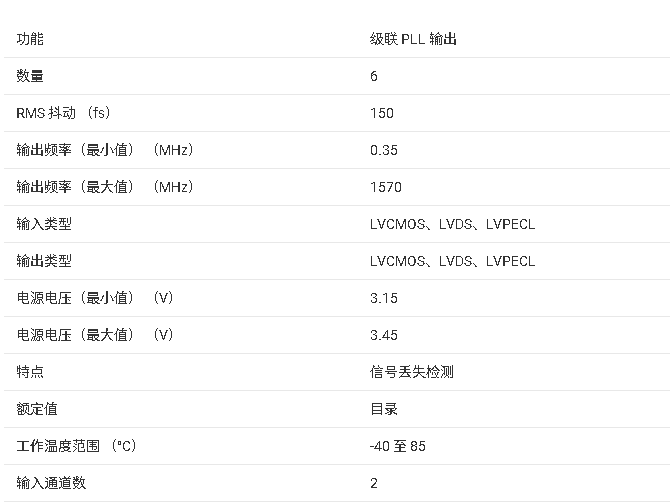

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析

LMK0482x系列时钟抖动清除器:高性能时钟解决方案解析 在电子设计领域,时钟信号的稳定性和低

深入解析 CDC421Axxx:高性能低抖动时钟发生器

时钟发生器——CDC421Axxx。 文件下载: cdc421a106.pdf 一、产品概述 CDC421Axxx 是一款高度集成的固定频率、低抖动

TI CDCDLP223:DLP™ 系统的高性能时钟合成器

TI CDCDLP223:DLP™ 系统的高性能时钟合成器 在电子设计领域,时钟合成器对于确保系统的稳定运行至关重要。今天我们要探讨的是德州

CDC7005高性能时钟合成器与抖动清除器技术文档总结

CDC7005高性能时钟合成器与抖动清除器技术文档总结

评论