摘要

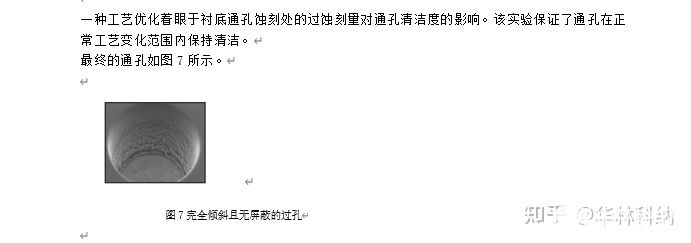

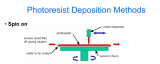

通过使用多级等离子体蚀刻实验设计、用于蚀刻后光致抗蚀剂去除的替代方法,以及开发自动蚀刻后遮盖物去除顺序;一种可再现的基板通孔处理方法被集成到大批量GaAs制造中。对于等离子体蚀刻部分,使用光学显微镜和扫描电子显微镜(SEM)来确定缺陷密度和通孔尺寸。使用光学显微镜、SEM和俄歇电子能谱(AES)完成对蚀刻后去除的分析。通过一系列评估,来自通用化学公司的化学物质被确定为能有效地同时去除光刻胶掩模和蚀刻残留物。开发的最终工艺产生了具有大约80度的单斜面侧壁轮廓的穿过衬底的通孔,该通孔清除了蚀刻后的掩膜材料。

介绍

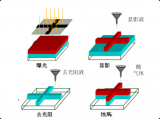

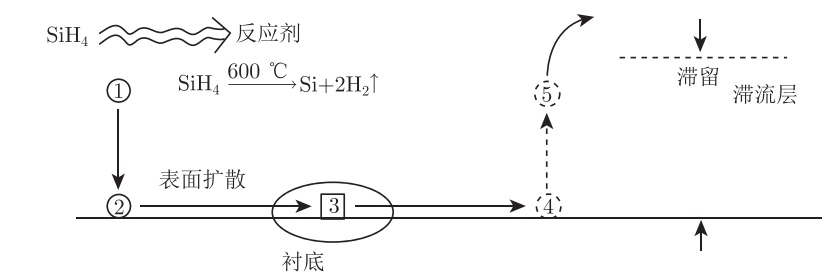

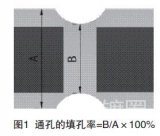

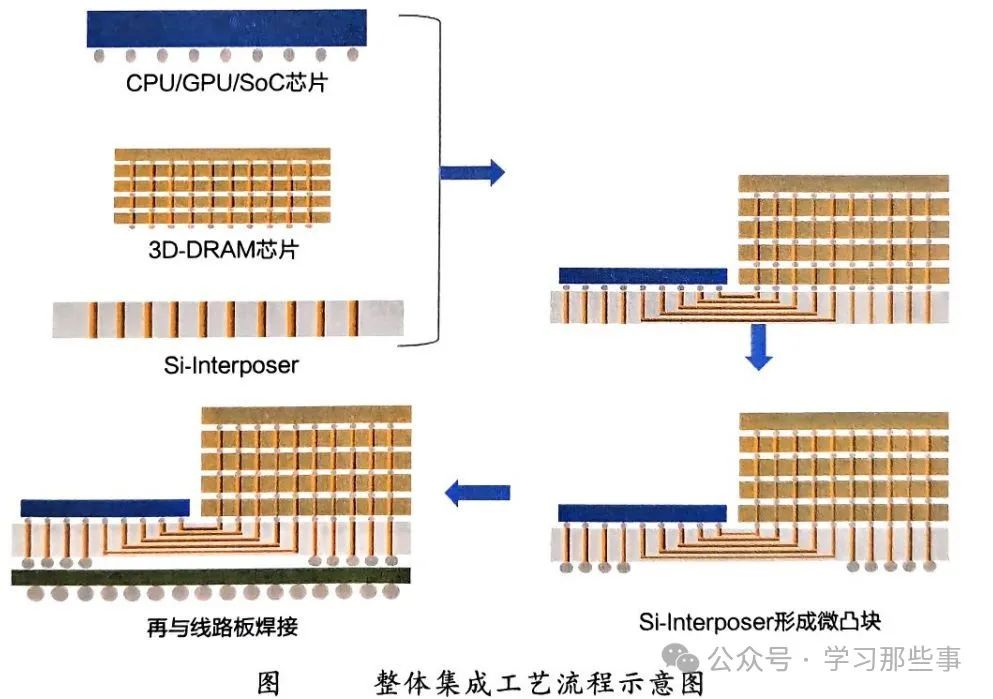

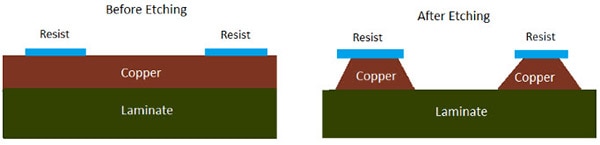

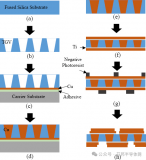

背面砷化镓(GaAs)通过基板的加工是一个高度机械化、非自动化的过程,需要大量的操作员干预。1制造商一直在努力使这一过程更具可制造性、稳健性和成本效益。衬底通孔制造包括将晶片安装到支撑衬底(图1)、机械和化学晶片减薄、光刻、等离子体蚀刻、光致抗蚀剂去除、蚀刻后残留物去除、金属化,以及最后将晶片从其支撑衬底上拆下。虽然每一个都是独立的过程,但它们确实相互影响。综上所述,成功的过孔的生产需要考虑整个背面工艺的材料和条件。

建立蚀刻工艺后,需要开发合适的面纱清洁。对于清洁工艺来说,重要的是要稳健,并处理任何自然的蚀刻工艺变化。利用从蚀刻后残留物的AES获得的知识,尝试确定哪种化学物质将提供干净的通孔。更具挑战性的是,加工温度必须严格控制在热塑性安装粘合剂的软化点以下。最后,必须仔细考虑与粘合剂的化学相互作用。

蚀刻修改

使用热塑性材料在安装在载体衬底上的150 mm (100) GaAs晶片上进行蚀刻实验。将晶片减薄到90 m.的目标厚度。用80 m直径的通孔和金蚀刻停止层涂覆在晶片的正面。所有实验都使用相同的掩模板。

此外,为了筛选通孔轮廓,SEM以30度的倾斜角用于晶片中心和边缘的自上而下的测量。然后测量顶部和底部通孔直径以及通孔侧壁垂直部分的长度。最后,通过自上而下的SEM工作筛选的晶片被剖切,并确定垂直与倾斜的比率。

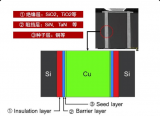

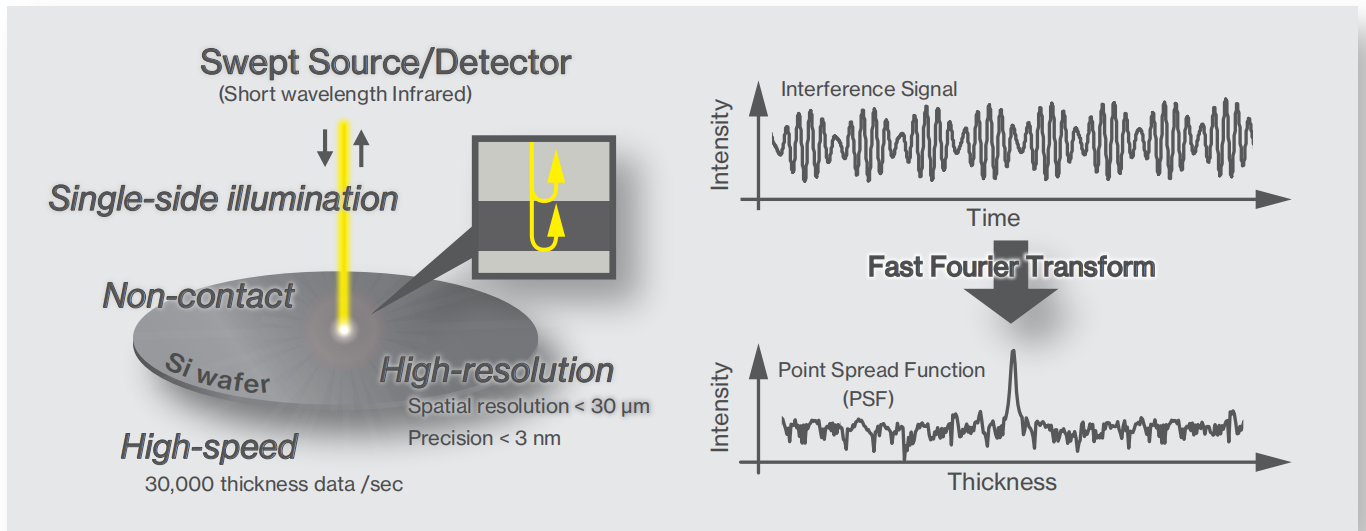

使用BCl3/Cl2气体化学的电感耦合等离子体(ICP)通孔蚀刻工艺被用于实验。该蚀刻机具有静电卡盘(ESC)和氦背面冷却。在等离子体条件下,将晶片表面的温度保持在100℃以下以防止光致抗蚀剂碳化至关重要。保持晶片温度也是防止热塑性安装材料分解所希望的。晶片中心测得的最终工艺温度为43℃,边缘为48℃。

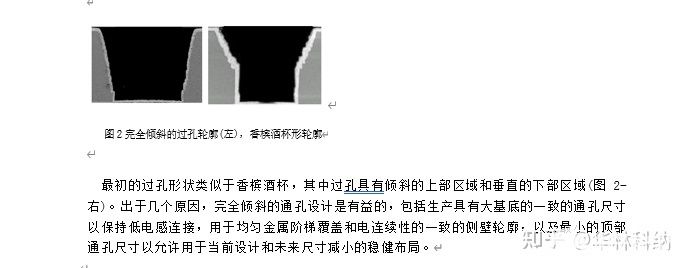

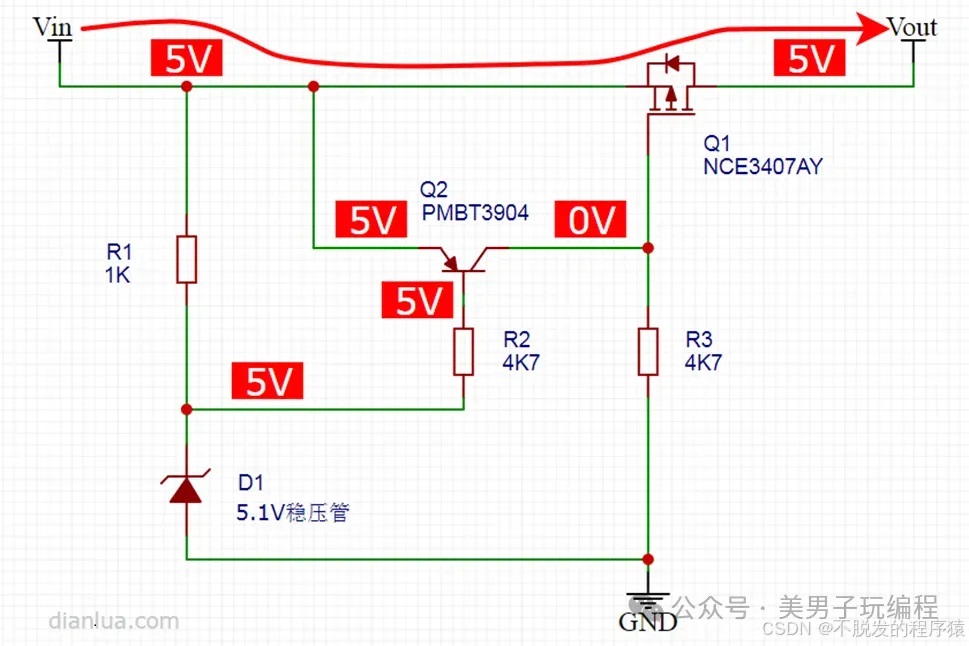

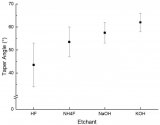

蚀刻过程中的第一步是原位去渣步骤,以去除任何潜在的光刻胶浮渣。去渣之后是使用BCl3/Cl2化学物质的突破步骤。对于主蚀刻步骤,使用BCl3/Cl2化学混合物。去渣和突破步骤通常用于最大限度地减少因污染、残留光刻胶或基板不均匀性而形成的柱状物或草状物。进行初始筛选实验以确定光刻和蚀刻参数对通孔轮廓的影响。探索曝光后烘烤温度、下电极功率、源功率、压力、卡盘温度和气流。响应是通过顶部直径,底部直径和垂直侧壁长度。从顶部和底部通孔直径计算侧壁角度对于单斜率剖面(图2-左)。结果显示,较低的曝光后烘烤温度是产生较窄的上部通孔直径的主要影响。曝光后烘烤温度增加20 ℃,通孔直径增加约15微米。底部通孔直径不受任何蚀刻或光参数的影响。完全倾斜的过孔的角度被计算为75度

85度。没有尖角的完全倾斜的通孔改善了在去除面纱期间湿化学物质的渗透。干净、完全倾斜的过孔形状还允许改善台阶覆盖和更薄的金属涂层,从而降低成本(图2-左)。

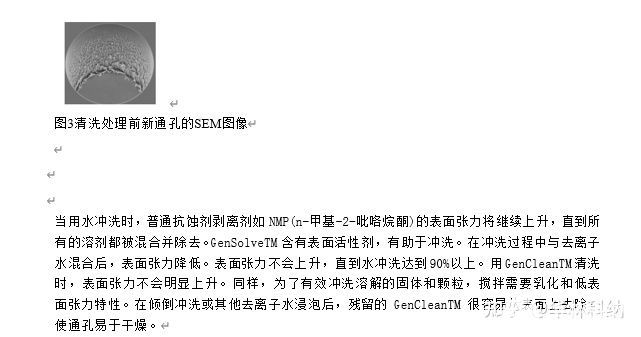

表面轮廓术用于计算蚀刻过程的蚀刻速率和选择性。在没有曝光后烘烤步骤的情况下,在用光致抗蚀剂图案化的GaAs晶片上测量台阶高度。优化的蚀刻速率条件产生了5.7 m/minute.的蚀刻速率因此,新的蚀刻工艺产生了完全倾斜的通孔轮廓。关于过蚀刻量的实验表明,过蚀刻越短,减少了面纱的数量(图3)。

结论

通过一系列的实验设计,开发了穿过衬底的通孔蚀刻工艺。该工艺产生入射角为75至85度的完全倾斜的通孔轮廓。生产的面纱材料的量减少了。等离子灰化过程被取消,由于金浓度降低,可以更容易地去除面纱。开发的面纱清洁工艺利用了溶剂配方(GenSolveTM)、预漂洗(GenCleanTM)和短时间金属浸出步骤的组合。这种优化产生了一种可制造的模块,并且产生了一致的干净过孔。

审核编辑:汤梓红

电子发烧友App

电子发烧友App

评论