文章来源:学习那些事

原文作者:小陈婆婆

随着集成电路特征尺寸的缩小,工艺窗口变小,可靠性成为更难兼顾的因素,设计上的改善对于优化可靠性至关重要。本文介绍了等离子刻蚀对高能量电子和空穴注入栅氧化层、负偏压温度不稳定性、等离子体诱发损伤、应力迁移等问题的影响,从而影响集成电路可靠性。

集成电路可靠性是产品寿命、稳定性和性能的关键, 晶圆制造阶段的可靠性问题主要源于工艺步骤对器件的潜在损伤。 等离子体蚀刻工艺对集成电路可靠性有广泛且决定性的影响,本文分述如下:

可靠性与失效时间

等离子体蚀刻对高能量电子和空穴注入栅氧化层(HCl)的影响

等离子体蚀刻对负偏压温度不稳定性(NBTI)的影响

等离子体蚀刻对等离子体诱发损伤(PID)的影响

等离子体蚀刻对应力迁移(SM)的影响

1、可靠性与失效时间

在超大规模集成电路时代,可靠性设计必须贯穿于IC开发的每个过程,这包括设计、工艺开发、制造和封装等各个阶段,只有全面考虑,新技术运用时的可靠性才能得到一定保证。随着集成电路特征尺寸的缩小,工艺窗口变小,可靠性成为更难兼顾的因素,设计上的改善对于优化可靠性至关重要。

1. 可靠性与时间的关系:

产品的可靠性通常是随时间递减的函数,即工作时间越长,可靠性越低。

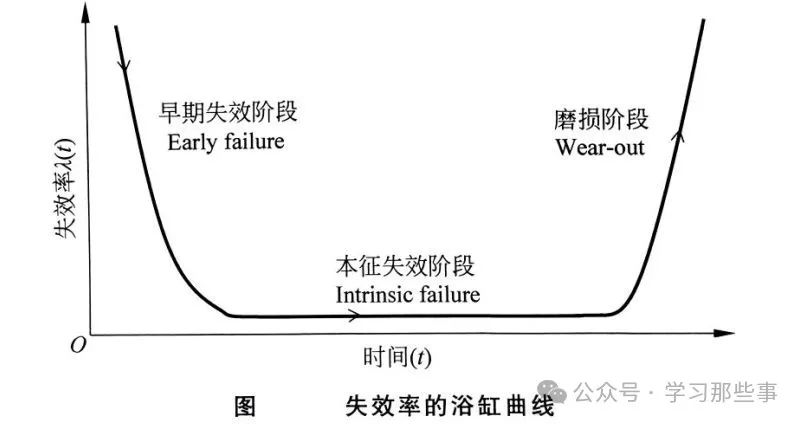

图1 失效率的浴缸曲线

2. 规定条件对可靠性的影响:

产品的可靠性水平和寿命在不同工作条件下会有所不同,这些条件包括环境条件、维护条件和操作方法等。

3. 可靠性与质量的不同:

器件的可靠性与质量是两个不同的概念,质量是器件与时间无关的属性,而可靠性则与器件随时间的退化相关。

4. 失效时间的定义:

当器件的重要参数退化到不能正常工作时,器件失效,此时对应的时间称为失效时间。

失效时间与寿命不同,寿命强调在规定条件下(一般为工作条件),而失效时间不一定。

5. 失效时间与应力的关系:

器件的最终失效时间不仅与器件的材料性能和微结构有关,也取决于器件承受的电场、温度、化学环境等应力的大小。

6. 失效时间和应力的建模:

对失效时间和应力的建模非常关键,模型直接决定了从高应力水平下的失效时间外推到低应力水平下的失效时间长短。

7. 威布尔失效率:

威布尔失效率可能随时间增大、减小或保持不变,这取决于威布尔分布的参数。

当参数等于1时,威布尔失效率是常数,与时间无关。当参数小于1时,威布尔失效率随时间减小。当参数大于1时,威布尔失效率随时间增大。

2、等离子体蚀刻对HCI的影响

在工艺可靠性领域,HCI(高能量电子和空穴注入栅氧化层)是导致器件性能退化的重要因素。这种注入过程会产生界面态和氧化层陷阱电荷,进而造成栅氧化层的损伤。随着损伤的累积,器件的电流电压特性将发生变化,当这些变化超过一定限度时,器件将失效。

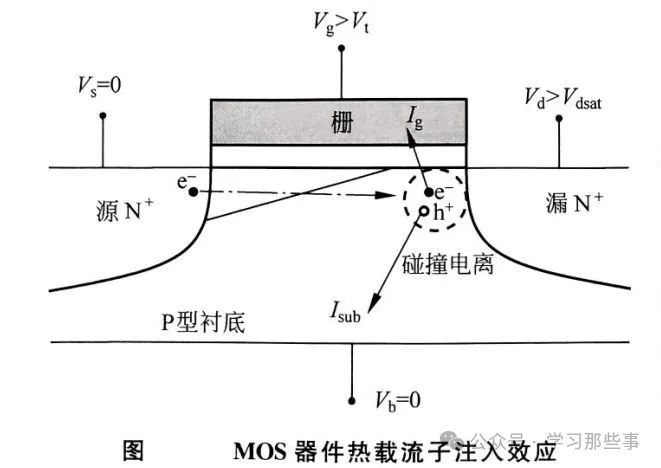

热载流子注入效应示意图:

图2 MOS器件热载流子注入效应

上图展示了MOSFET器件的热载流子注入效应示意图,直观呈现了热载流子如何对栅氧化层造成损伤。

为了抑制热载流子效应,可以采取以下措施:选择合适的源漏离子注入浓度和衬底注入浓度;使用轻掺杂漏区(LDD)方法,该方法已被证明能有效抑制热载流子效应。

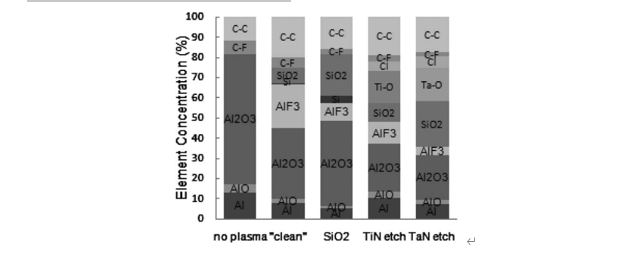

等离子体蚀刻对HCI性能的影响:

研究表明,等离子体相关工艺损伤后的栅极氧化层,其HCI性能明显恶化。这是因为等离子体工艺过程中,栅氧中会流过一定的电流,这个充电电流会造成新的氧化层陷阱和界面态。当热载流子注入这些受损区域时,更容易导致氧化层的进一步损伤。

3、等离子体蚀刻对NBTI的影响

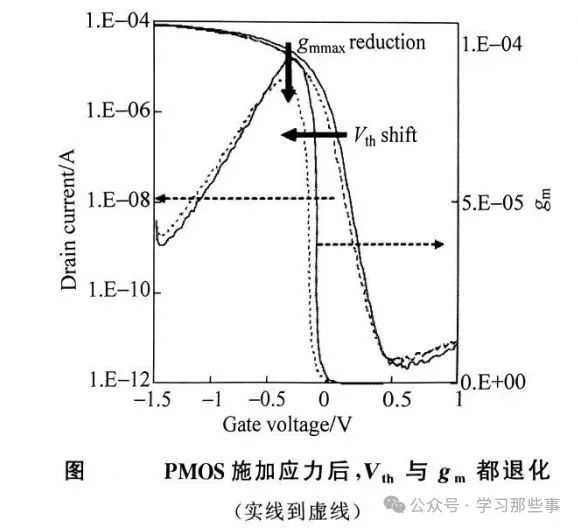

NBTI(负偏压温度不稳定性)是PMOS器件在栅极负偏压和较高温度条件下工作时,其器件参数(如阈值电压Vth、跨导gm和饱和漏电流Idsat等)发生不稳定性的现象。

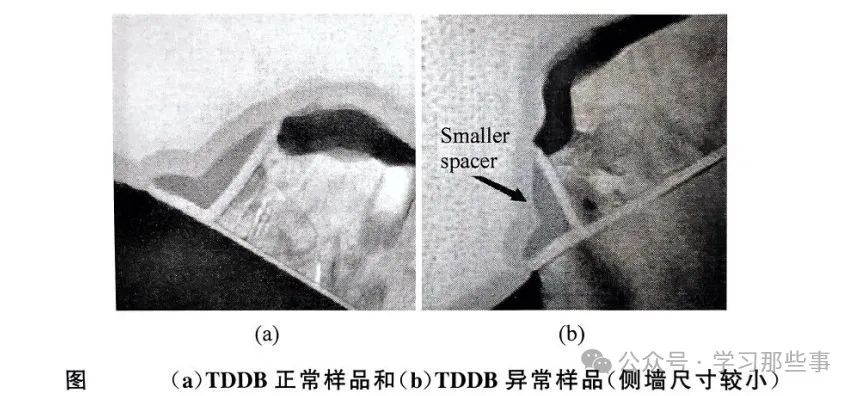

图3 (a)TDDB正常样品和(b)TDDB异常样品(侧墙尺寸较小)

对于NMOS器件,则对应的是PBTI(正偏压温度不稳定性)

图4 PMOS施加压力后,Vth与gm都退化(实线到虚线)

NBTI效应的解释模型:

反应-扩散模型很好地解释了NBTI效应。在该模型中,PMOS器件在负栅偏压下,SiO2层中的电场方向为离开界面方向。如果Si-H键断裂,就会释放一个H+离子,留下带正电的界面态。H+离子在电场作用下向SiO2中漂移,增加了氧化层陷阱的数量。这些界面态与陷阱导致半导体器件参数的改变。当停止施加应力(即电场降为0)时,部分H+离子会产生回流,使器件发生部分恢复,但完全恢复是不可能的,因为部分H离子会在SiO2栅电介质层内发生还原反应。

NBTI退化的饱和现象:

由于Si-H键的数量是有限的,随时间增加,未断的Si-H数目减少,Si-H断裂引起的退化率也不断减小,最后趋近于零,这就是NBTI退化的饱和现象。

引起NBTI的物质与改善方法:

氢气和水汽是引起NBTI的两种主要物质。为了减小NBTI效应,必须降低Si-SiO2界面处的初始缺陷密度并且使水不出现在氧化层中。将氘注入Si-SiO2界面来形成Si-D键是一个改善NBTI的有效方法。

等离子体损伤对NBTI的影响:

经过等离子体损伤(PID)后的器件,其NBTI性能会发生退化。因为电荷损伤导致了更高的界面态密度,尽管后续的退火过程有可能将其钝化,但这些高的初始界面态密度导致了更高的NBTI退化。因此,NBTI可以作为检测潜在等离子体损伤的有效手段。

退火工艺对NBTI的影响:

研究表明,纯H2退火比N2/H2混合气体对改善NBTI帮助更大。因为纯H2有更高的H2含量,其到达Si-SiO2界面的H更多,对悬挂键的钝化作用更明显。然而,退火时间有明显的饱和效应,当退火时间大于一定值后,延长退火时间并不能进一步增加NBTI失效时间。过量的H和界面态形成有紧密联系,所以当太多的H漂移到达Si-SiO2界面时,会与已钝化后的Si-H键中的H结合形成H2,而遗留下新的悬挂键,从而导致NBTI性能退化。

伪栅去除工艺对NBTI的影响:

在伪栅去除工艺中,HBr气体的解离生成的H活性离子会损伤栅电介质,影响NBTI。使用同步脉冲等离子体可以降低HBr的解离率,明显改善NBTI,且不影响其他性能。在伪栅去除后的光阻去除工艺中,更高H2含量的N2/H2灰化工艺能使NBTI失效时间增加一个数量级。

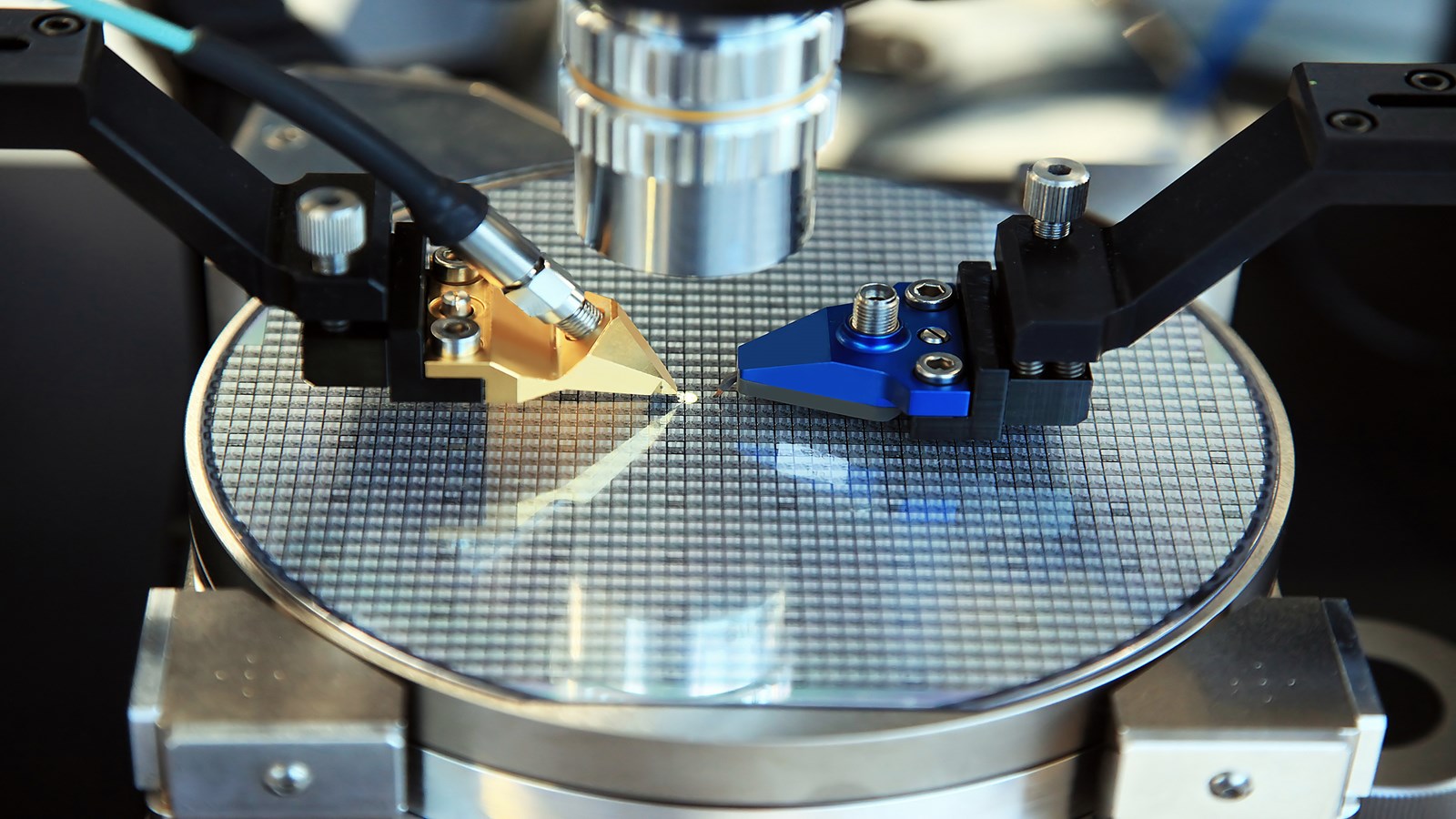

4、等离子体蚀刻对PID的影响

等离子体诱发损伤(PID)是集成电路制造中一个关键问题,尤其在各式各样的等离子体工艺中,MOSFET器件易受损伤而导致性能偏移。PID的主要机理包括:

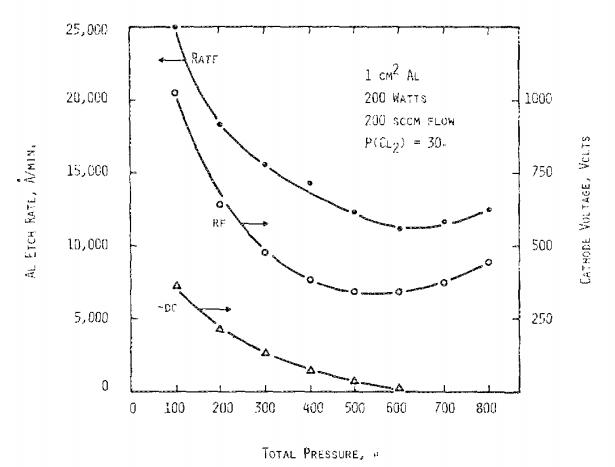

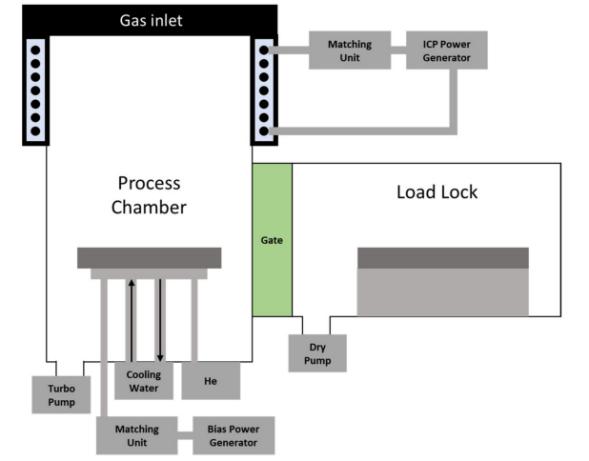

1. 等离子体密度:

高的等离子体密度意味着更大的电流,容易引发PID问题。当等离子体密度增加时,电荷充电效应增强,导致器件损伤加剧。例如,减小ICP金属蚀刻反应腔室高度会显著增强晶圆表面电场强度,从而增加PID风险。

2. 等离子体局部不均匀性:

在非均匀等离子体中,局部范围内的电势不均衡会在晶圆表面产生电流路径,引起栅氧化层损伤。

3. 电子遮蔽效应(ESE):

等离子体中电子的方向性较差,容易被光阻遮蔽,导致正离子在蚀刻前端聚集,形成对器件的正电势,引发PID。

图5 (a)电子遮蔽效应和(b)反向电子遮蔽效应

4. 反向电子遮蔽效应(RESE):

在图形空旷区域,电子的各向同性导致部分电子被要蚀刻的金属侧壁收集,而离子不会,从而在金属侧壁形成负电势,对器件造成损伤。

5. 真空紫外线辐射(VUV):

等离子体放电时产生的大量VUV光子会在栅氧化层中产生光电流,损伤器件。采用带隙比氧化硅窄的氮化硅层能有效阻挡VUV,保护栅氧化层。

PID的程度可以通过栅极漏电流来表征。

图6 (a)PID的测试方法:栅极漏电流和(b)PID的测试结果

当接收天线面积与器件大小的比值(天线比)越大时,器件受到的损伤越严重。电路设计时,避免过高的天线比、采用金属跳层或使用保护二极管将电荷引入衬底能有效抑制PID影响。

不同等离子体工艺对PID的影响各异。例如,第一金属层的电介质蚀刻在很小的接触孔天线比时就可能产生PID问题,而高层金属要到几千的天线比时才产生PID问题。过蚀刻时间、电源频率等因素也会影响PID。在伪栅去除工艺中,由于等离子体直接接触高k栅介质层上的功函数金属,氢离子对栅介质层的损伤大大增加。

为了应对PID挑战,业界开发出了在伪栅去除后再沉积高k栅介质层的工艺,以及先用等离子体蚀刻一部分再用化学溶剂去除剩余部分的方法,有效避免了等离子体蚀刻引起的栅介质层损伤。

5、等离子体蚀刻对SM的影响

等离子体蚀刻对SM(应力迁移)的影响主要体现在以下两个方面:

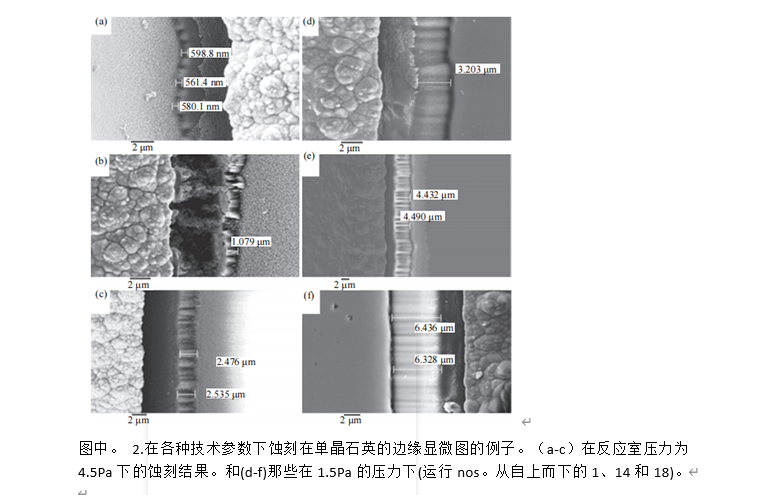

蚀刻后通孔的形貌

蚀刻工艺后,通孔的形貌对后续的金属填充和应力迁移行为有着重要影响。如果蚀刻过程中,沟槽和通孔连接处出现了小栅栏状形貌,这种不规则的形貌会导致铜填充时在这些区域出现空洞。

图7 通孔底部空洞导致接触电阻上升

这些空洞会成为应力集中的点,从而在应力迁移过程中加速空洞的扩展,最终导致电路的早期失效。因此,控制蚀刻工艺以获得良好的通孔形貌是防止应力迁移的重要措施之一。

通孔底部的聚合物残留及铜表面处理工艺

蚀刻后,通孔底部可能会残留一些聚合物。这些聚合物残留物不仅会影响后续的金属填充效果,还可能成为应力迁移过程中的缺陷源。此外,通孔底部的铜表面状态也对应力迁移行为有显著影响。如果铜表面存在氧化物或其他污染物,会加速应力迁移过程中的空洞形成和扩展。

为了改善通孔底部的聚合物残留和铜表面状态,通常采用蚀刻后处理(Post Etch Treatment, PET)工艺。有研究发现使用N2/H2气体的PET比CO2能更好地清除通孔底部的聚合物残留,并且对通孔底部铜进行还原,从而显著提高了SM性能。

图8 (a)不同PET对通孔底部聚合物的清理能力以及(b)相对应的SM测试结果

这是因为N2/H2气体能够有效地与聚合物残留物反应,将其转化为可挥发的物质,并通过气流将其带走。同时,H2还能还原铜表面,去除氧化物和其他污染物,从而改善了铜表面的状态。

等离子体蚀刻对SM的影响主要体现在通孔形貌和通孔底部的聚合物残留及铜表面处理工艺上。为了获得良好的电路性能和可靠性,需要严格控制蚀刻工艺和PET工艺参数,以获得良好的通孔形貌和清洁的铜表面。

-

集成电路

+关注

关注

5464文章

12695浏览量

375827 -

等离子体

+关注

关注

0文章

147浏览量

15297 -

晶圆

+关注

关注

53文章

5451浏览量

132774 -

蚀刻工艺

+关注

关注

3文章

53浏览量

12122

原文标题:等离子体蚀刻工艺对集成电路可靠性影响

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

金属蚀刻残留物对对等离子体成分和均匀性的影响

等离子体蚀刻和沉积问题的解决方案

PCB多层板等离子体处理技术

PCB电路板等离子体切割机蚀孔工艺技术

PCB板制作工艺中的等离子体加工技术

PCB多层板等离子体处理技术

低温等离子体废气处理系统

TDK|低温等离子体技术的应用

等离子体应用

石英单晶等离子体蚀刻工艺参数的优化

精确跟踪芯片蚀刻过程,用高分辨率光谱仪监测等离子体

等离子体清洗工艺的关键技术 等离子体清洗在封装生产中的应用

等离子体蚀刻工艺对集成电路可靠性的影响

等离子体蚀刻工艺对集成电路可靠性的影响

评论