文章来源:Jeff的芯片世界

原文作者:Jeff的芯片世界

本文主要讲述TSV的工艺技术。

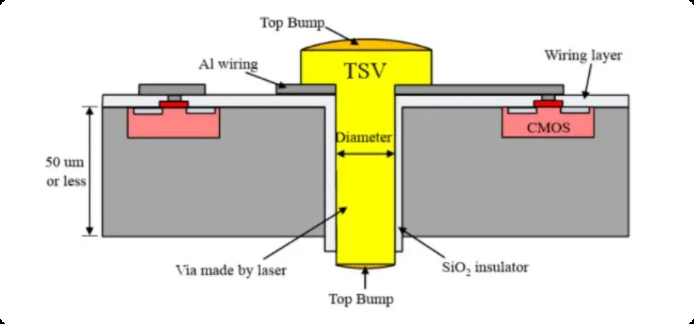

硅通孔(Through Silicon Via,TSV)技术是一种通过在硅介质层中制作垂直导通孔并填充导电材料来实现芯片间垂直互连的先进封装技术。作为三维系统级封装(3D-SiP)的核心技术,TSV能够显著缩短互连路径,降低寄生电容和电感,从而提升系统性能、降低功耗,并支持器件小型化与异构集成。与传统水平的引线键合和倒装芯片互连相比,TSV实现了芯片在垂直方向的堆叠与连接,被视为第三代封装互连技术的重要代表。

TSV制造工艺概述

TSV制造主要包括通孔形成、侧壁涂层和导体填充三大步骤。

1.通孔形成

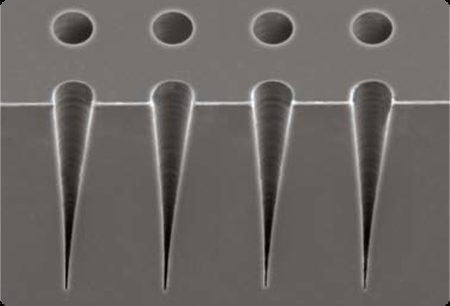

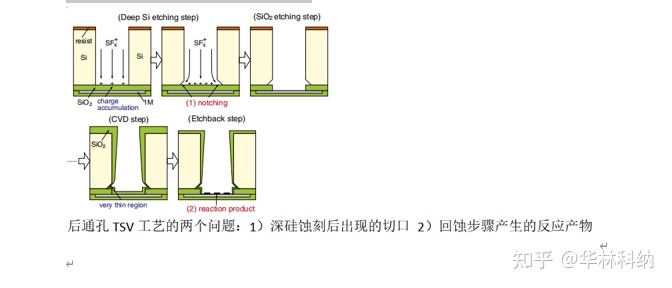

通孔形成通常采用深反应离子刻蚀(DRIE)、激光钻孔或湿法刻蚀等方法。其中,Bosch刻蚀作为主流的干法刻蚀工艺,通过刻蚀与钝化的交替循环,实现高深宽比的通孔刻蚀,深度可达数百微米,但也存在扇形侧壁、微观负载效应等问题,需通过优化射频功率、气体流量等参数改善。激光钻孔利用高能激光束进行光热烧蚀,具有高精度、无机械磨损的优点,但易产生热影响区和溅渣沉积,可通过多脉冲紫外激光或添加掩膜等方式解决。湿法刻蚀早期使用KOH溶液,成本低但侧壁不垂直且易污染,现代改进工艺如HNA刻蚀体系、TMAH工艺和光辅助电化学刻蚀提高了通孔圆度和CMOS兼容性。

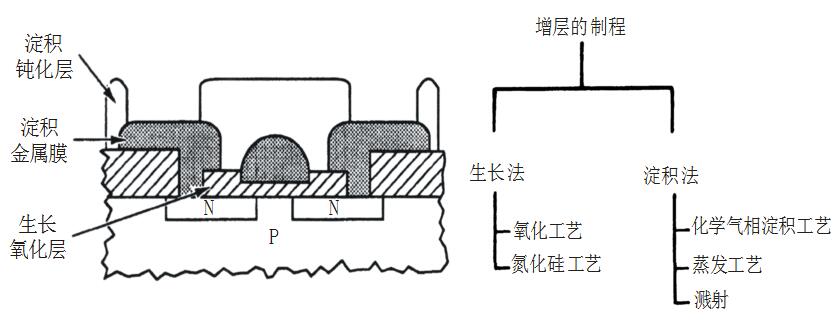

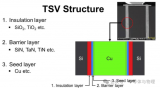

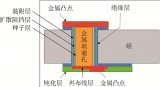

2.侧壁涂层

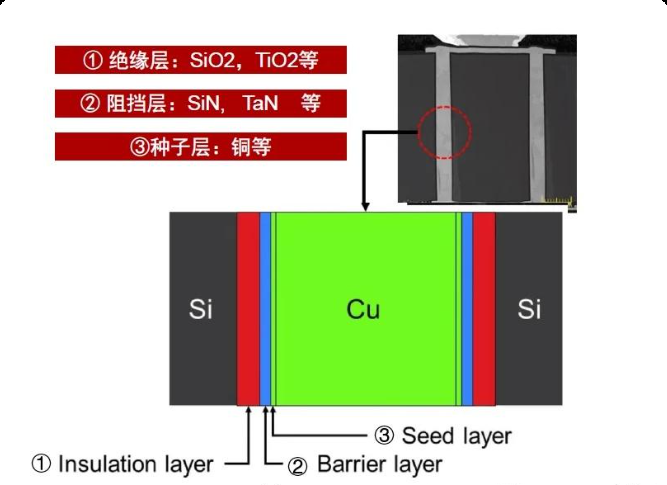

TSV侧壁涂层包括绝缘层、阻挡层和种子层,直接影响电气性能与可靠性。绝缘层常用SiO₂,通过热氧化法、PECVD或HDPCVD制备,用于防止漏电和串扰;阻挡层采用Ti、TiN或Ta等材料,通过原子层沉积、化学镀或溅射工艺沉积,防止金属离子扩散并提升粘合度;种子层如Ti/Cu或Ti/Au薄层,通过溅射形成,影响后续填充机制,高深宽比TSV中需解决涂层均匀性问题,可引入化学镀CoWB等材料优化。

3.导体填充

导体填充以电镀法为主,核心挑战是避免电镀角效应导致的空洞。采用Cu-Ni、Cu-W等新型填充材料可提升填充速率与质量;周期性反向脉冲(PPR)电镀能细化晶粒、实现无空洞填充,但填充时间较长,需通过调整镀液添加剂缩短周期。添加剂的使用需精确控制成分与比例,单一添加剂也可降低工艺复杂度。超声波辅助电镀通过声流与空化效应加速传质,提高填充速度与质量,且能减少添加剂使用,但需控制超声波功率以避免降低铜与侧壁的黏附性。

TSV键合工艺与应用

TSV键合工艺主要包括焊锡凸点、铜柱凸点(CPB)和混合键合。电镀法是主流的凸点制备方式,通过光刻胶控制尺寸,但工序复杂、焊料成分难调控;非光刻工艺可低成本制备Sn-3.5Ag凸点,而焊膏压印工艺通过模板压印和回流焊简化流程,但受模板限制难用于超细间距TSV,可结合激光边缘技术改善。铜柱凸点结合光刻与电镀,在TSV上形成高铜柱并镀薄焊锡膜,实现更小间距、避免桥接,且散热性和机械强度高,但热处理中易形成金属间化合物,需添加镍层解决;焊锡注模(IMS)工艺可制备无铅凸点,但需耐高温光刻胶材料。混合键合实现介质层与金属(如铜)界面的无缝键合,通过表面处理提高亲水性和降低粗糙度,再经退火增强键合强度,但成本较高,且需优化等离子体处理以避免Cu₂O形成。

TSV技术应用广泛,涵盖低密度与高密度场景。低密度应用如单个MEMS器件,通过TSV实现电信号从晶圆正面到背面的传导,并将MEMS堆叠在CMOS芯片上,例如惯性传感器集成,采用DRIE、MOCVD沉积铜等工艺。

高密度应用包括传感器/MEMS阵列与CMOS集成,如CMOS图像传感器(CIS),索尼IMX400采用三层堆叠结构,通过TSV与重布线层互联,TSV最小直径达2.5μm。中介层技术(2.5D集成)作为芯片与封装基板间的衬底,应用于多芯片集成与I/O再分配,如光电异构集成系统。多层与晶圆堆叠用于3D封装与高带宽存储器(HBM)互联,通过TSV与微凸点连接,实现薄形化晶圆堆叠,减小间隙与总厚度。

在具体应用方向上,TSV可分为背面连接、2.5D封装和3D封装。背面连接用于CMOS图像传感器和SiGe功率放大器,通过TSV替代引线键合,减小模组尺寸并简化晶圆级封装。2.5D封装如FPGA器件,使用硅中介层实现密切连接,解决大尺寸芯片技术难题。3D封装以存储器堆叠为代表,如宽I/O DRAM,降低封装高度与功耗,提升带宽。

TSV技术优势与挑战

TSV技术的主要优势包括缩短互连长度以降低信号延迟、电容和电感,从而提升通信速度与带宽,同时降低功耗;支持垂直堆叠,实现器件小型化;促进异构集成,高效整合逻辑、内存和MEMS等不同功能芯片。

然而,TSV也面临制造成本高、工艺复杂、热应力问题等挑战。成本高源于深硅刻蚀、电镀填充等复杂步骤;热应力因铜与硅的热膨胀系数差异,可能导致介质层开裂或分层;工艺涉及刻蚀、涂层、填充和平坦化等多步骤,对精度要求极高。

未来展望与发展方向

TSV技术持续优化,推动3D-SiP向更高效、可靠的三维集成发展。未来创新方向包括通孔尺寸缩减、晶圆减薄、材料与工艺改进,以及应对散热、信号传输和可靠性挑战。

企业如台积电通过CoWoS和InFO技术提升TSV产能,加速HBM商业化;三星电子在HBM封装中推动高层数堆叠;英特尔利用Foveros 3D封装实现逻辑与内存芯片整合;国内企业在CIS等领域实现技术突破,增强产业链竞争力。随着集成电路封装需求增长,TSV将在5G、人工智能、自动驾驶等领域发挥关键作用,但仍需解决可靠性、散热和测试等问题以促进广泛应用。

-

制造工艺

+关注

关注

2文章

216浏览量

21315 -

TSV

+关注

关注

4文章

139浏览量

82777 -

先进封装

+关注

关注

2文章

563浏览量

1062

原文标题:TSV工艺技术介绍

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

TSV技术的关键工艺和应用领域

TSV工艺流程与电学特性研究

硅通孔(TSV)电镀

TSV关键工艺设备及特点

TSV的工艺流程和关键技术综述

基于两步刻蚀工艺的锥形TSV制备方法

TSV以及博世工艺介绍

TSV制造工艺概述

TSV制造工艺概述

评论