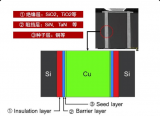

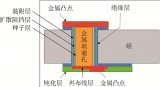

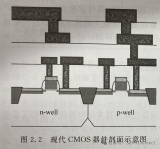

电子发烧友网报道(文/黄山明)TSV(Through Silicon Via)即硅通孔技术,是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的技术,是2.5D/3D封装的关键工艺技术之一。

这些材料核心功能主要有三个,导电连接,主要提供低电阻信号/电源传输路径;结构支撑,用来承受多层堆叠带来的机械应力;介质隔离,避免相邻通孔间的电短路。

主流材料种类繁多,包括导电材料、绝缘材料、辅助材料等。技术上,TSV材料需要再材料匹配性上让热膨胀系数(CTE)需与硅(2.6ppm/℃)接近,避免热应力导致分层,其中铜填充需控制晶粒尺寸(<1μm)以降低电阻率。

填充工艺上,要满足高深宽比(>10:1)通孔的无空洞填充,电镀铜需优化添加剂(如整平剂、抑制剂)实现超填充( superfilling)。

同时可靠性上,电迁移寿命(10年@150℃)需满足 JEDEC 标准,铜扩散阻挡层厚度需≥10nm(防止与硅反应生成Cu₃Si)。

当前全球TSV技术发展情况

目前在全球,主要由台积电、三星和英特尔主导TSV技术发展,尤其在HBM、3D IC等高端封装领域占据全球超80%市场份额。其中铜作为主流填充材料,其电镀工艺(如硫酸铜、甲基磺酸铜体系)已实现高深宽比TSV的无缺陷填充,电镀设备与添加剂市场由安美特、陶氏等国际企业垄断。

规模上,2024年全球TSV市场规模达342.3亿美元,预计2031年增至796.1亿美元(CAGR 13%),其中填充材料成本占比达44%,驱动电镀市场年复合增长率16%。预计2025年中国TSV市场规模占全球25%,2027年国内封装材料市场规模突破600亿元,TSV相关材料(如绝缘层、种子层)成为增长核心。

近年来,国内市场在TVS材料上也有了不小的技术突破,例如深南电路、兴森科技的FC-BGA基板通过华为认证;华海诚科的颗粒状环氧塑封料(GMC)通过HBM封装验证;德邦科技实现集成电路封装材料批量供应。

值得一提的是,TSV关键材料(如绝缘层、种子层)国产化率逐步提升,2025年目标ABF载板15%、键合丝30%、封装树脂25%,2030年目标达50%、70%、60%。当然,一些高端材料(如高纯度球铝、先进基板)仍依赖进口,需加强产学研协同发展。

小结

TSV 填充材料的选择需综合考虑导电性、机械性能、工艺兼容性及成本。随着 3D 集成技术向更高密度、更低功耗发展,材料创新与工艺优化将持续推动 TSV 技术突破,成为半导体产业重要支撑。

这些材料核心功能主要有三个,导电连接,主要提供低电阻信号/电源传输路径;结构支撑,用来承受多层堆叠带来的机械应力;介质隔离,避免相邻通孔间的电短路。

| 材料类型 | 典型材料 | 特性优势 | 应用场景 |

| 导电材料 | 铜(Cu) | 导电性最优(1.68μΩ・cm),成本低 | 主流 TSV 填充 |

| 钨(W) | 抗电迁移能力强,高温稳定性好 | 高温环境 / 可靠性要求高 | |

| 银(Ag) | 高导电性,但成本高易氧化 | 特殊高频器件 | |

| 绝缘材料 | 二氧化硅(SiO₂) | 介电常数低(3.9),工艺成熟 | 通孔侧壁绝缘 |

| 聚酰亚胺(PI) | 柔韧性好,应力缓冲能力强 | 柔性电子器件 | |

| 氮化硅(Si₃N₄) | 高击穿电压(>10MV/cm) | 高压器件 | |

| 辅助材料 | 阻挡层(Ta/TaN) | 防止铜扩散至硅基底 | 铜填充 TSV 必备 |

| 种子层(Cu) | 促进电镀铜均匀沉积 | 铜填充工艺 |

主流材料种类繁多,包括导电材料、绝缘材料、辅助材料等。技术上,TSV材料需要再材料匹配性上让热膨胀系数(CTE)需与硅(2.6ppm/℃)接近,避免热应力导致分层,其中铜填充需控制晶粒尺寸(<1μm)以降低电阻率。

填充工艺上,要满足高深宽比(>10:1)通孔的无空洞填充,电镀铜需优化添加剂(如整平剂、抑制剂)实现超填充( superfilling)。

同时可靠性上,电迁移寿命(10年@150℃)需满足 JEDEC 标准,铜扩散阻挡层厚度需≥10nm(防止与硅反应生成Cu₃Si)。

当前全球TSV技术发展情况

目前在全球,主要由台积电、三星和英特尔主导TSV技术发展,尤其在HBM、3D IC等高端封装领域占据全球超80%市场份额。其中铜作为主流填充材料,其电镀工艺(如硫酸铜、甲基磺酸铜体系)已实现高深宽比TSV的无缺陷填充,电镀设备与添加剂市场由安美特、陶氏等国际企业垄断。

规模上,2024年全球TSV市场规模达342.3亿美元,预计2031年增至796.1亿美元(CAGR 13%),其中填充材料成本占比达44%,驱动电镀市场年复合增长率16%。预计2025年中国TSV市场规模占全球25%,2027年国内封装材料市场规模突破600亿元,TSV相关材料(如绝缘层、种子层)成为增长核心。

近年来,国内市场在TVS材料上也有了不小的技术突破,例如深南电路、兴森科技的FC-BGA基板通过华为认证;华海诚科的颗粒状环氧塑封料(GMC)通过HBM封装验证;德邦科技实现集成电路封装材料批量供应。

值得一提的是,TSV关键材料(如绝缘层、种子层)国产化率逐步提升,2025年目标ABF载板15%、键合丝30%、封装树脂25%,2030年目标达50%、70%、60%。当然,一些高端材料(如高纯度球铝、先进基板)仍依赖进口,需加强产学研协同发展。

小结

TSV 填充材料的选择需综合考虑导电性、机械性能、工艺兼容性及成本。随着 3D 集成技术向更高密度、更低功耗发展,材料创新与工艺优化将持续推动 TSV 技术突破,成为半导体产业重要支撑。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TSV

+关注

关注

4文章

139浏览量

82779 -

硅通孔

+关注

关注

2文章

31浏览量

12150

发布评论请先 登录

相关推荐

热点推荐

无源TSV转接板的制作方法

无源TSV转接板作为先进封装的“交通枢纽”,是实现高密度异构集成的核心。本文深度解析TSV高深宽比刻蚀与填充工艺,详尽对比聚合物电镀与大马士革法RDL的制备差异,并拆解背面减薄、露铜及CoW组装全流程,带你攻克先进互连技术的制造

PCB板中塞孔和埋孔的区别

PCB板中塞孔和埋孔在很多方面都存在明显区别,下面咱们一起来看看: 一、定义 塞孔是指在孔壁镀铜之后,用环氧树脂等材料填平过孔,再在表面镀

TSV制造技术里的通孔刻蚀与绝缘层

相较于传统CMOS工艺,TSV需应对高深宽比结构带来的技术挑战,从激光或深层离子反应刻蚀形成盲孔开始,经等离子体化学气相沉积绝缘层、金属黏附/阻挡/种子层的多层沉积,到铜电镀填充及改进型化学机械抛光(CMP)处理厚铜层,每一步均

基于TSV的减薄技术解析

在半导体三维集成(3D IC)技术中,硅通孔(TSV)是实现芯片垂直堆叠的核心,但受深宽比限制,传统厚硅片(700-800μm)难以制造直径更小(5-20μm)的TSV,导致芯片面积占

日月光最新推出FOCoS-Bridge TSV技术

日月光半导体最新推出FOCoS-Bridge TSV技术,利用硅通孔提供更短供电路径,实现更高 I/O 密度与更好散热性能,满足AI/HPC对高带宽与高效能的需求。

TSV硅通孔填充材料

TSV硅通孔填充材料

评论