来源:光刻人笔记;作者:LithoMan

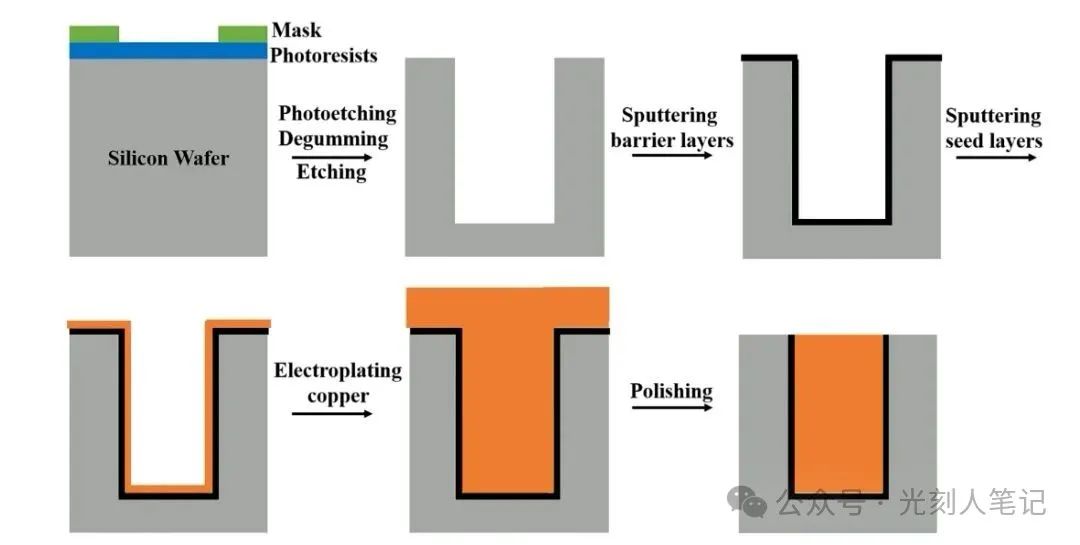

铜互连工艺是一种在集成电路制造中用于连接不同层电路的金属互连技术,其核心在于通过“大马士革”(Damascene)工艺实现铜的嵌入式填充。该工艺的基本原理是:在绝缘层上先蚀刻出沟槽或通孔,然后在沟槽或通孔中沉积铜,并通过化学机械抛光(CMP)去除多余的铜,从而形成嵌入式的金属线。

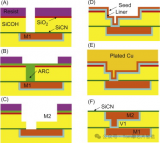

铜互连工艺的主要步骤包括:

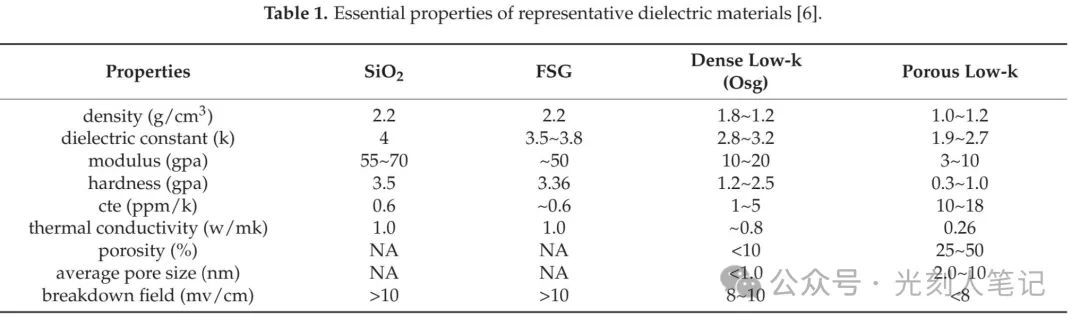

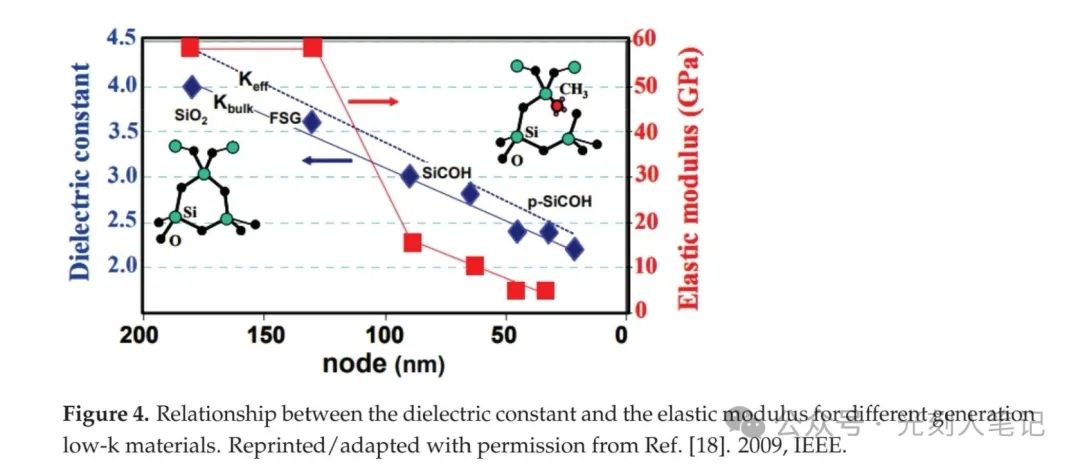

介质沉积:在衬底上沉积一层低介电常数(low-k)材料,如氟掺杂二氧化硅(k ~ 3.7)或碳掺杂二氧化硅(k ~ 2.7),以减少寄生电容和信号延迟。

光刻与蚀刻:通过光刻胶图案化并蚀刻出沟槽或通孔,形成所需的金属连接路径。

阻挡层与种子层沉积:在沟槽或通孔底部沉积阻挡层(如TaN、Ta或Si3N4),以防止铜扩散到绝缘层中,同时在阻挡层上沉积铜种子层,作为电镀的导电基础。

铜电镀:在种子层上进行电镀,填充沟槽或通孔,形成铜互连结构。

化学机械抛光(CMP) :通过CMP去除沟槽或通孔外多余的铜,使表面平整,便于后续工艺。

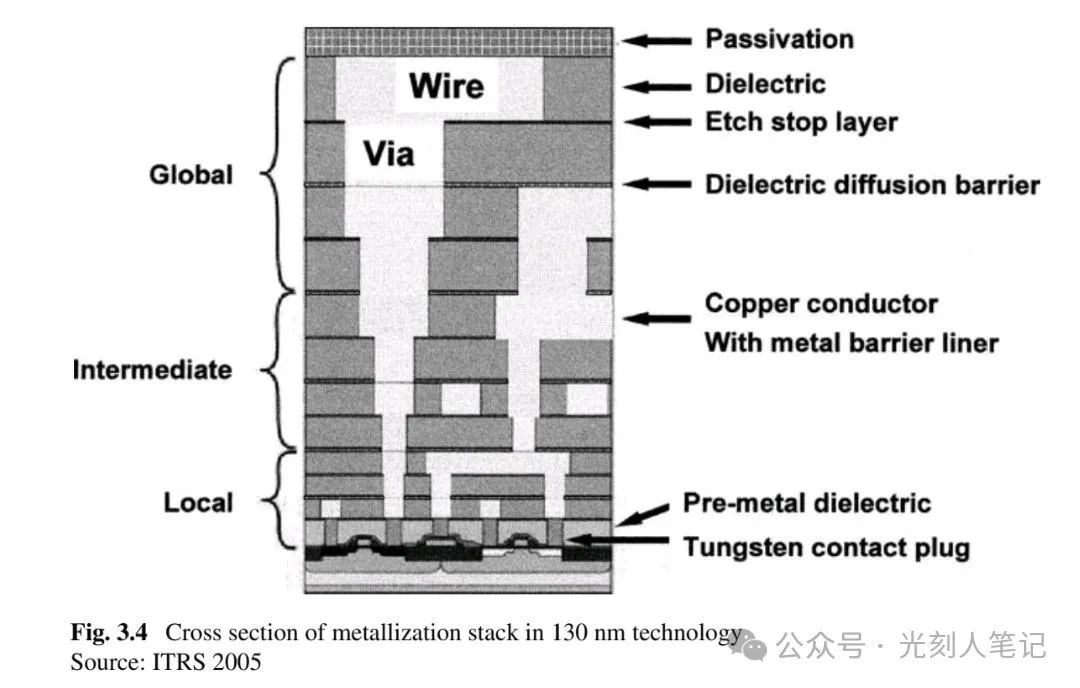

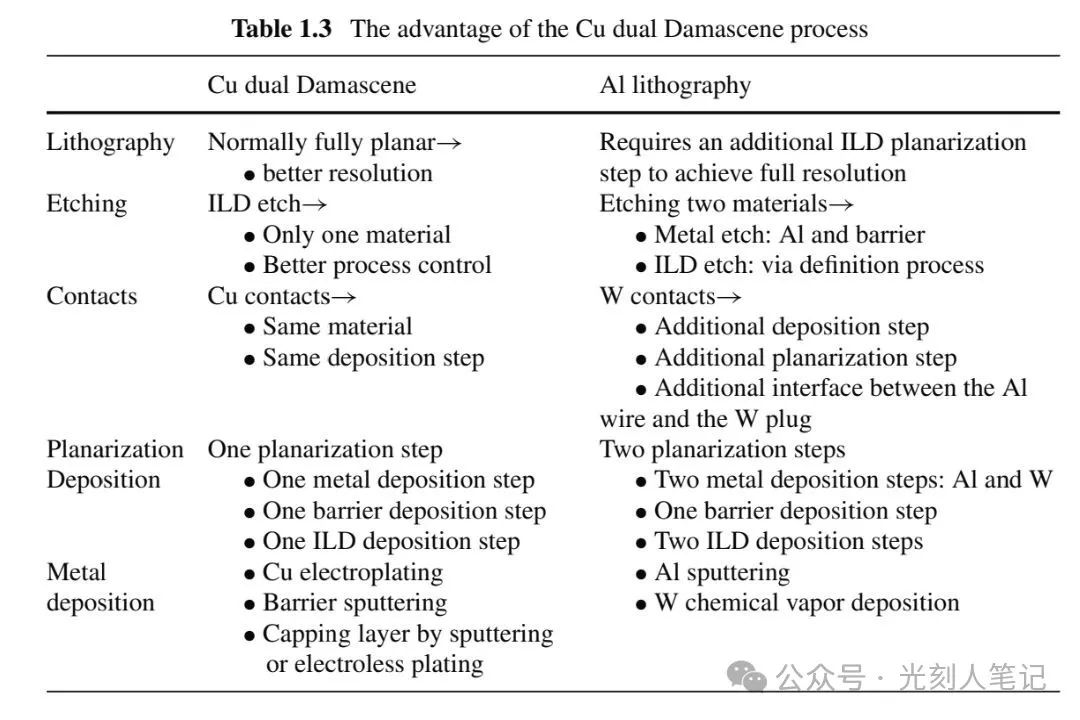

与铝互连相比,铜互连具有更低的电阻率(1.68 μΩ·cm)和更好的抗电迁移性能,因此成为现代集成电路制造中的主流互连材料。然而,由于铜的刻蚀难度较大,传统的干法或湿法刻蚀技术难以满足纳米级工艺的要求,因此发展了双嵌入式(Dual Damascene)工艺,即在一次光刻和蚀刻过程中同时形成沟槽和通孔,从而提高工艺效率和良率。

铜互连工艺的发展历程

铜互连工艺的发展历程可以追溯到20世纪90年代,其核心在于以铜替代传统铝互连材料,以解决小型化集成电路中出现的电阻率高、电迁移问题等挑战。以下是铜互连工艺发展的关键阶段和主要进展:

铜互连的引入与大马士革工艺的提出

1997年,IBM率先将铜互连技术引入其100nm制程芯片制造中,标志着铜互连时代的开始。IBM提出的“大马士革工艺”(Damascene Process)成为铜互连的主要制造方法。该工艺通过先在介电层上形成沟槽和通孔图案,再填充铜并进行化学机械抛光(CMP)来去除多余铜,从而实现高精度的互连结构。

铜互连的优势与挑战

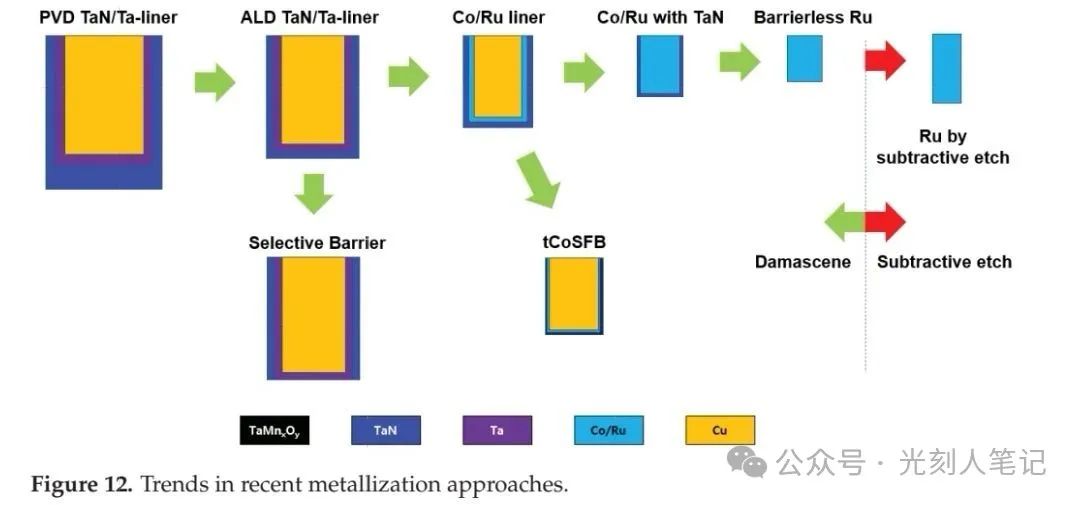

铜的电阻率比铝低约40%,具有更好的导电性和抗电迁移性能,因此成为高性能集成电路的首选材料。然而,铜的引入也带来了新的挑战,例如铜原子在介电层中的扩散问题,这可能导致电压衰减甚至击穿。为了解决这一问题,研究人员开发了阻挡层工艺,如氮化钽/钽(TaN/Ta)结构,以防止铜的扩散。

铜互连工艺的优化与材料创新

随着技术节点的缩小,铜互连的可靠性问题逐渐显现,例如电迁移、漏电和击穿等。为此,研究人员不断优化铜互连的工艺,包括改进沉积和蚀刻技术、开发新型阻挡层材料(如钌、钴等)以及探索更高效的铜沉积工艺。例如,IBM在2024年IEDM会议上发表了关于铜互连技术的最新进展,探讨了其在先进节点中的应用。

铜互连在先进节点中的应用与替代材料的探索

随着技术进入7nm及以下节点,铜互连的电阻效应和尺寸效应问题日益突出,促使行业开始探索铜的替代材料,如钌、钴等。尽管如此,铜在短距离互联中仍因其成本低、性能稳定而保持优势。此外,光互连(CPO)等新技术也在探索中,但目前铜互连仍是主流选择。

铜互连工艺的未来展望

铜互连技术在20年的发展中取得了显著进步,成为高性能集成电路制造的核心工艺之一。然而,随着技术节点的进一步缩小,铜互连仍面临新的挑战,如如何进一步降低电阻、提高可靠性以及实现更复杂的3D集成结构。未来,铜互连技术将继续在上层互连层中发挥重要作用,同时与其他新型材料协同工作,以满足先进芯片的需求。

铜互连工艺的主要应用领域

铜互连工艺的主要应用领域包括:

超大规模集成电路(VLSI)制造:铜互连技术广泛应用于超大规模集成电路制造中,取代传统铝互连,因其具有更低的电阻率、更好的抗电迁移性能和更高的导热性,能够有效降低功耗和提高芯片性能。

先进封装技术:铜互连在先进封装技术中也有重要应用,如硅通孔(TSV)技术实现多层芯片的垂直互连,以及Bump、RDL等技术实现芯片间的电气连接。

高性能计算与通信设备:铜互连技术在高端微处理器、存储器芯片等高性能计算设备中广泛应用,能够支持更高的电流密度和更低的功耗。

功率器件与IGBT模块:铜互连技术在功率器件中具有显著优势,如降低IGBT模块的功率损耗,提升散热能力,提高模块功率密度和可靠性。

化学机械抛光(CMP) :铜互连工艺在CMP技术中起着关键作用,用于去除互连结构中的多余铜层,确保表面平整度。

低介电常数(low-k)材料集成:铜互连技术与低介电常数材料结合使用,以减少互连结构中的寄生电容,提高芯片性能。

三维集成电路(3D IC) :铜互连技术在三维集成电路中用于实现芯片层之间的垂直互连,提高集成度和性能。

新型半导体材料:铜互连技术在氧化物半导体和柔性电子中作为导电层或电极材料发挥关键作用。

铜互连技术在半导体制造的多个关键领域中发挥着重要作用,是推动芯片性能提升和集成度提高的重要基础。

铜互连工艺的关键技术步骤(如沉积、蚀刻等)

铜互连工艺的关键技术步骤主要包括以下几个方面:

沉积:在硅片上依次沉积绝缘层(如SiO2、TEOS、低k介质等),随后沉积阻挡层(如TiN、TaN、SiN等)和种子层(如Cu/Ta),以确保铜的附着和防止扩散。

光刻与图案化:通过光刻技术在绝缘层上形成图案,定义通孔和沟槽的位置。

蚀刻:使用等离子体刻蚀或化学蚀刻技术,在绝缘层上形成通孔和沟槽。

铜沉积:采用电镀(ECD)或化学气相沉积(CVD)等方法,在通孔和沟槽中填充铜。

化学机械抛光(CMP) :去除多余的铜层,使铜层与绝缘层表面齐平。

剥离与清洗:去除光刻胶和残留的阻挡层或种子层。

这些步骤共同构成了铜互连工艺的核心流程,确保了铜互连结构的高精度、低电阻和良好的可靠性。

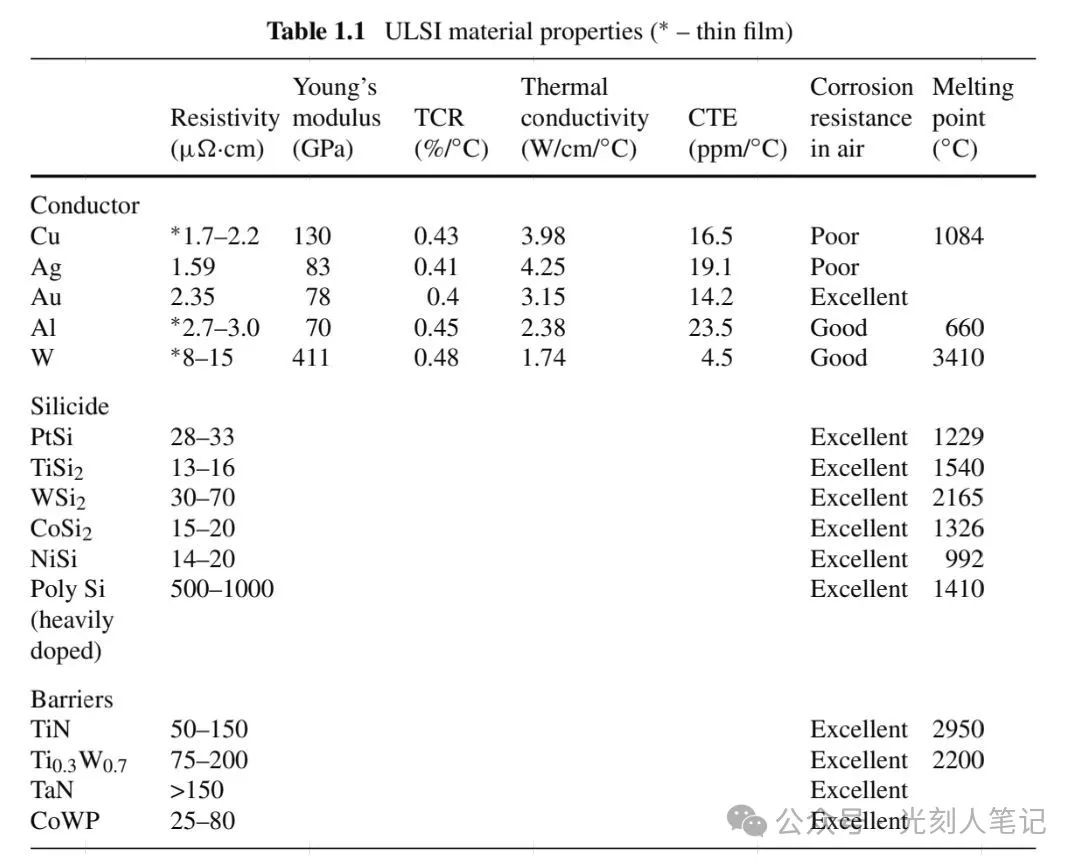

铜互连材料的物理化学特性

铜互连材料的物理化学特性主要体现在其电阻率、导电性、抗电迁移能力、热稳定性、与衬底的附着力以及扩散阻挡性能等方面。以下是基于我搜索到的资料对铜互连材料的物理化学特性的总结:

电阻率:铜具有较低的电阻率(约1.67 μΩ·cm),这使其成为低电阻互连的理想选择,尤其在纳米级集成电路中,铜的低电阻率显著降低了RC延迟和功耗。

导电性:铜的导电性优异,能够有效传输电流,是未来集成电路中最具潜力的互连材料之一。

抗电迁移能力:铜相比铝具有更强的抗电迁移能力,这使其在高密度互连结构中更加可靠。

热稳定性:铜具有良好的热传导系数,能够有效散热,同时在高温下仍能保持较高的导电性和机械强度。

与衬底的附着力:铜与硅基底之间的附着力较差,容易发生剥离或扩散。为了解决这一问题,研究者开发了过渡层(如氮化钛、氮化钽等)来增强铜与衬底之间的结合力。

扩散阻挡性能:铜容易向硅基底扩散,影响器件性能。为此,研究者引入了多种扩散阻挡层材料,如氮化物(TaN、TiN)、金属化合物(Ru、Co)和自组装分子层(SAMs)等,以防止铜扩散。

化学稳定性:铜在空气中容易氧化,形成氧化铜层,这会增加接触电阻。为了防止氧化,研究者在铜互连中添加了抗氧化剂(如抗坏血酸)或使用保护性气体(如N₂)进行烧结。

加工性能:铜的电镀工艺成熟,尤其是在酸性硫酸铜体系中,能够实现高电流密度和均匀的铜沉积,适用于深沟槽和通孔的填充。

界面反应:铜与介电材料(如低介电常数材料)之间的界面反应对互连性能至关重要。研究表明,界面的粘附性和稳定性是影响铜互连可靠性的重要因素。

微观结构:铜的微观结构(如晶粒尺寸、织构)对互连性能有显著影响。研究表明,通过控制沉积条件(如温度、压力、气体组成)可以优化铜的微观结构,从而提高其导电性和抗电迁移能力。

铜互连材料具有优异的物理化学特性,使其成为先进集成电路中不可或缺的互连材料。然而,其在实际应用中仍面临一些挑战,如与衬底的附着力、扩散阻挡性能和界面稳定性等问题,需要通过材料设计和工艺优化来进一步解决。

铜互连工艺面临的挑战(如电迁移、可靠性等)

铜互连工艺在先进集成电路制造中面临诸多挑战,其中电迁移和可靠性问题尤为突出。随着芯片尺寸的不断缩小,铜互连的电迁移问题逐渐成为影响集成电路可靠性的关键因素之一。电迁移是指在高电流密度下,金属原子沿着导体内部的晶格结构发生定向迁移的现象,这会导致铜原子从某些区域流失,形成空洞,从而显著增加互连电阻,阻碍电流传输,甚至引发短路或断路。此外,铜互连的电迁移还受到电流密度、温度、应力梯度等因素的影响。在纳米尺度下,铜互连的电阻率会随着线宽的减小而迅速增加,即“尺寸效应”,这进一步加剧了电迁移问题。

为了解决电迁移问题,业界提出了多种改进措施。例如,通过优化通孔倾角、实现阻挡层的完全反溅射和改善铜表面处理,可以有效减缓电迁移,提高互连线的可靠性。此外,采用新型阻挡层材料如钴(Co)或钌(Ru)作为替代材料,因其具有更小的平均电子自由程和更高的熔点,具备更好的抗“尺寸效应”和抗电迁移能力。同时,改进的互连工艺如空气隙技术和应力缓冲层沉积也被认为是提高铜互连可靠性的有效手段。

铜互连的可靠性还受到其他因素的影响, 如铜污染和沉积问题。铜污染是指铜原子在介电质层中的扩散导致电压衰减甚至击穿,可以通过采用氮化钽/钽结构来阻挡铜原子的扩散。沉积问题则可以通过大马士革工艺和化学机械平坦化抛光研磨工艺来解决。此外,随着工艺节点的缩小,大马士革工艺需要精准控制沟槽尺寸并降低介质层损伤,因此业界开发了金属硬掩模层一体化刻蚀工艺。

铜互连工艺在先进集成电路制造中面临的主要挑战包括电迁移和可靠性问题。为应对这些问题,业界正在通过优化材料选择、改进工艺流程和引入新型技术手段来提高铜互连的性能和可靠性。

铜互连与传统铝互连的对比分析

铜互连与传统铝互连在半导体制造中具有显著的对比优势。首先,铜的电阻率(1.7 μΩ·cm)比铝(2.8 μΩ·cm)低约60%,这使得铜互连在降低互连线电阻和RC延迟方面具有明显优势,从而提升芯片速度和性能。此外,铜的抗电迁移能力远优于铝,其电流密度上限可达5×10⁶ A/cm²,而铝仅为2×10⁵ A/cm²,这使得铜互连在高密度集成中更加可靠。

在工艺流程方面,铜互连通常采用大马士革工艺,通过先刻蚀介质层再填充铜的方式实现,而铝互连则采用传统的沉积和刻蚀工艺。铜互连工艺在介质层处理上更为复杂,但能够实现更精细的互连结构。此外,铜互连的寄生电容较小,信号串扰也较少,这对高速集成电路尤为重要。

然而,铜互连也面临一些挑战,如TDDB(时间相关介质击穿)问题,这在低k介质材料中尤为突出。尽管如此,铜互连因其在电阻、电迁移、导热等方面的综合优势,已成为先进制程集成电路中主流的互连材料。

-

集成电路

+关注

关注

5465文章

12695浏览量

375856 -

工艺

+关注

关注

4文章

720浏览量

30403 -

互连

+关注

关注

0文章

26浏览量

10598

原文标题:铜互联工艺

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文详解铜大马士革工艺

CMOS集成电路的基本制造工艺

超大规模集成电路铜互连电镀工艺

如何采用铜互连单大马士革工艺制作超厚金属铜集成电感的概述

铝/铜互连工艺与双镶嵌法(AL/Cu Interconnect and Dual Damascenes)

提高铜互连优势的方法

一文详解封装互连技术

铜互连,尚能饭否?

大马士革铜互连工艺详解

一文详解铜互连工艺

一文详解铜互连工艺

评论