本文主要简单介绍探讨接触孔工艺制造流程。以55nm接触控工艺为切入点进行简单介绍。

在集成电路制造领域,工艺流程主要涵盖前段工艺(Front End of Line,FEOL)与后段工艺(Back End of Line,BEOL)。前段工艺主要用于制作晶体管,而后段工艺则专注于实现晶体管之间的金属布线互连。其中,接触孔工艺作为前后段工艺衔接的关键环节,其作用是连接晶体管有源区与第一金属层。在大规模生产的成套工艺流程里,接触孔工艺一旦出现缺陷,常常会成为影响良率的关键因素。在该工艺模块中,接触电阻(Contact Resistance,Rc)和套刻对准(Overlay)是需要重点关注的两个核心部分。

电路信号的传输速度取决于电阻与电容的乘积,因此,在接触孔工艺中,降低接触电阻成为了一个至关重要的问题。针对这一问题,主要可从接触孔材料、接触孔关键尺寸等方面展开考量。

接触孔工艺简介

在接触孔材料方面,用金属镍硅化物替代以往的金属钴硅化物,能够获得更小的接触电阻;采用金属钨替换之前的金属铝作为接触孔的填充材料,不仅可拥有更强的抗电迁移能力,还能实现更小的电阻率以及更高的台阶覆盖率;在不影响填充能力的前提下,减小具有高阻特性的黏合层 Ti/TiN 的厚度,同样可以达到降低电阻的目的。

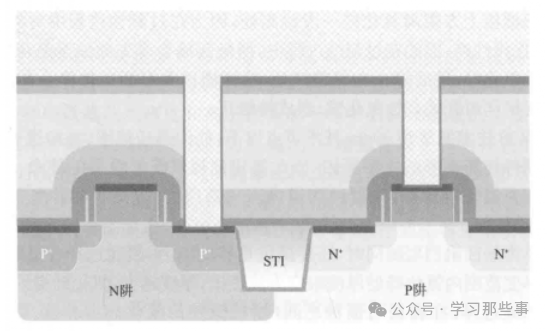

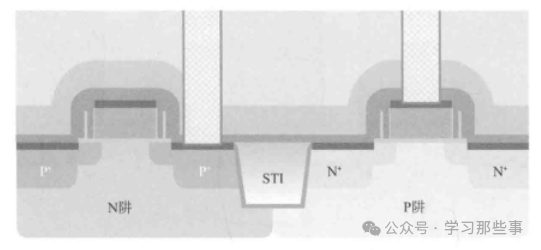

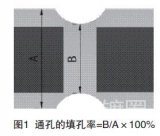

在接触孔关键尺寸方面,随着技术节点逐渐缩小,多晶硅到接触孔的距离越来越短。减小接触孔的关键尺寸,有助于减少多晶硅和接触孔之间桥联的问题,然而,关键尺寸的减小会致使接触孔与多晶硅及有源区的接触面积变小,进而增加接触电阻。与此同时,降低层间介质的厚度也有助于降低电阻。所以,需要探寻合适的工艺窗口,以平衡这些因素之间的关系。光刻工艺中的套刻对准步骤,对接触孔工艺有着较大的影响,尤其是在静态随机存取存储器(Static Random - Access Memory,SRAM)区域。静态随机存取存储器依靠提高晶体管密度来增加缓存容量,其设计可不遵循最小设计规则,这给工艺带来了极大的挑战。在静态随机存取存储器区域,当接触孔与栅极套刻对准时,若出现较大偏差,就容易导致接触孔和栅极之间发生桥联短路,进而使器件失效。当接触孔与有源区套刻对准时,部分有源区上的接触孔与有源区重叠,一旦产生对准偏差,在后续刻蚀过程中就会刻蚀掉一部分浅沟槽隔离(STI)上的氧化物,从而增加漏电,加大器件功耗。

接触孔工艺流程

55nm 接触孔工艺选用金属钨作为填充材料,在器件与第一层金属之间采用介质材料,以此形成层间介质层(Inter - Layer Dielectric,ILD),从而实现电性隔离,并降低金属与衬底之间的寄生电容。55nm 接触孔工艺的具体步骤如下:

清洗:

在进行化学气相沉积(Chemical Vapour Deposition,CVD)之前,需对晶圆表面进行清洗,以确保其表面洁净。

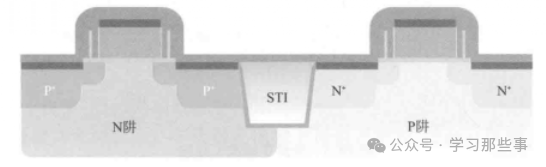

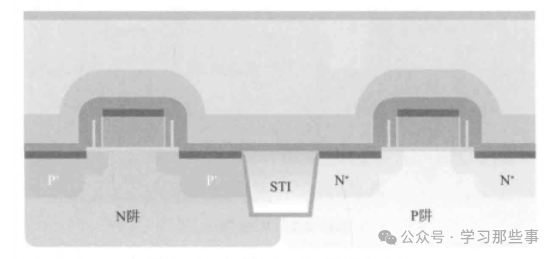

沉积具有拉应力的氮化物层:

如下图所示,利用化学气相沉积法沉积一层氮化物,这层氮化物既作为后续刻蚀接触孔的刻蚀停止层,同时还能引入应力。在早期工艺中,对器件的工作速率要求相对较低,所以在这一步骤采用的是氧化物加氮化物的组合,主要目的是实现电性隔离。加入氧化层,一方面是将其作为刻蚀停止层;另一方面是因为氮化物与硅衬底的晶格常数和热膨胀系数不匹配,氮化物与硅直接接触会产生较大应力,容易致使硅衬底出现裂纹、大量位错或缺陷。因此,需要在衬底上生长一层氧化物,以缓解氮化物与硅衬底之间的应力。随着技术节点不断缩小,对 <100> 晶向的硅片施加拉应力,能够显著提升其沟道的电子迁移率,进而提高器件的驱动电流。所以,在这一步骤中去除了氧化物,以充分发挥氮化物的应力作用,通过精准控制沉积工艺的各项指标来调控应力大小,有效提升 NMOS 器件的工作速率。

生长具有拉应力的氮化物

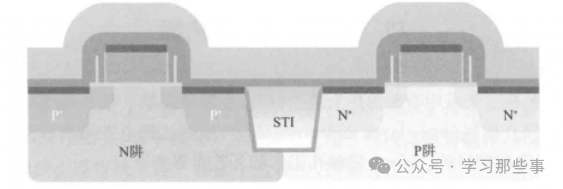

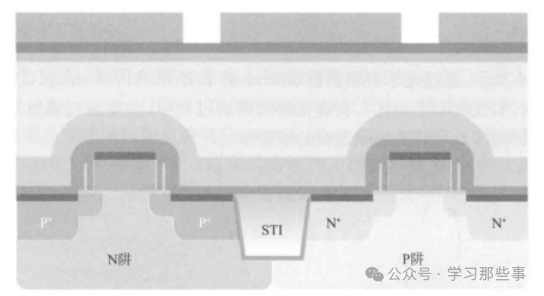

沉积磷硅玻璃:

如下图所示,运用高密度等离子体化学气相沉积工艺(High Density Plasma Chemical Vapour Deposition,HDPCVD)沉积磷硅玻璃(PSG),将其作为第一层层间介质层。磷硅玻璃是在未掺杂硅酸盐玻璃(Undoped Silicate Glass,USG)中掺磷形成的,它能够有效吸收固定离子(主要为 Na)并阻挡水汽。在该步骤中,主要从间隙填充能力(Gap Fill)、等离子体损伤、薄膜均匀性这三个方面对高密度等离子体化学气相沉积工艺进行优化。

生长磷硅玻璃层

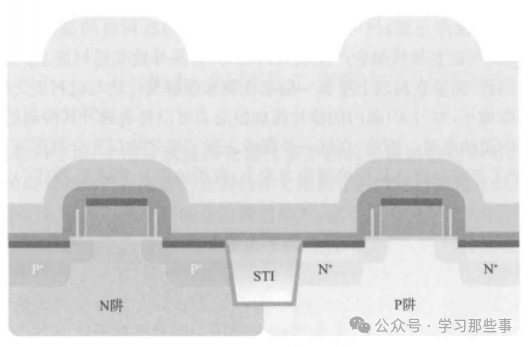

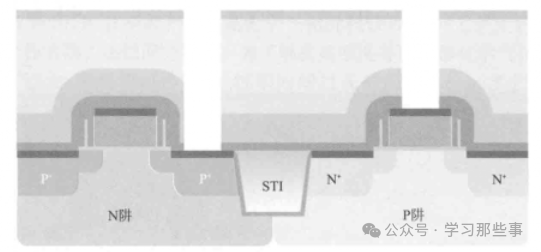

沉积 TEOS:

如下图所示,采用等离子体增强化学气相沉积(PECVD)工艺生长正硅酸乙酯(TEOS),将其作为第二层层间介质层。为解决高密度等离子体化学气相沉积工艺中等离子体密度过大、薄膜均匀性欠佳、沉积时间过长的问题,55nm 工艺采用 PSG + TEOS 的组合作为层间介质。

生长正硅酸乙酯层

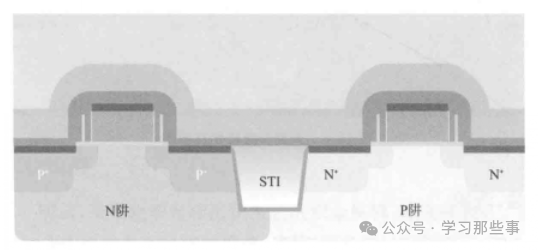

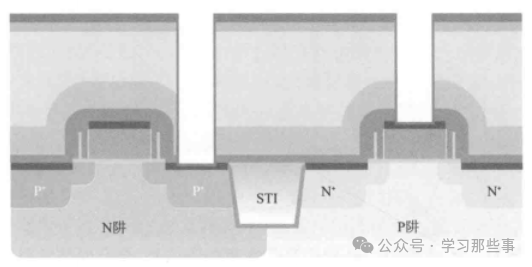

CMP:

如下图所示,借助化学机械研磨(Chemical Mechanical Polishing,CMP)来调整层间介质层的高度,实现表面平坦化。在研磨氧化物的过程中,主要通过调节研磨时间来达到指定的介质层高度,最后清洗去除表面的研磨液。

化学机械研磨调整高度

沉积氧化物:

如下图所示,利用等离子体增强化学气相沉积形成一层氧化物,该氧化物可作为光刻的抗反射涂层,以减少反射,降低驻波效应,同时还能修复化学机械研磨工艺对表面造成的损伤。

生成等离子体增强的氧化物

光刻:

如下图所示,通过光刻胶旋涂、前烘、对准与曝光、后烘、显影、坚膜等一系列步骤,将掩模上的图形转移到光刻胶上。非接触孔区域保留光刻胶,接触孔区域的光刻胶则通过显影去除,后续将通过刻蚀工艺形成接触孔。

光刻形成接触孔图案

刻蚀、清洗:

如下图所示,采用 CF₄等气体形成的等离子体轰击晶圆,去除无光刻胶覆盖区域的介质层,形成高深宽比的接触孔。在形成接触孔后,通过干法刻蚀和湿法刻蚀去除光刻胶和抗反射涂层,随后将晶圆放入清洗槽中清洗,最后在物理气相沉积(Physical Vapor Deposition,PVD)金属前,用氩离子溅射去除表面的氧化物。

刻蚀形成接触控图案

沉积黏合层(Glue Layer,GL):

如下图所示,利用物理气相沉积工艺溅射沉积 Ti 和 TiN 层。Ti/TiN 层主要有两方面作用:一方面,由于钨与氧化物的黏附性较差,如果直接将钨填充进氧化物,形成的介质层中钨层极易脱落,因此需要 Ti/TiN 作为黏附层,防止钨层脱落;另一方面,Ti/TiN 层作为阻挡层,能够有效防止钨扩散至器件有源区内,对器件性能造成损害。

沉积Ti/TiN层

沉积钨层:

如下图所示,采用化学气相沉积工艺沉积金属钨,填充接触孔。这个过程主要分为两步,第一步是利用六氟化钨(WF₆)、硅烷(SiH₄)和乙硼烷(B₂H₆)在一定温度和压力下反应沉积一层钨籽晶层,第二步是利用六氟化钨(WF₆)和氢气(H₂)沉积大量的钨。

沉积钨层

CMP:

如下图所示,利用化学机械研磨去除表面多余的钨层和 Ti/TiN 层,防止钨残留导致不同区域的接触孔短路,同时也使表面平坦化。正硅酸乙酯层是化学机械研磨的停止层,考虑到工艺的容忍度,当终点检测器检测到正硅酸乙酯的成分时,会再进行一定时间的研磨,确保钨没有残留。

-

检测器

+关注

关注

1文章

947浏览量

50116 -

工艺

+关注

关注

4文章

720浏览量

30393

原文标题:接触孔工艺简介

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

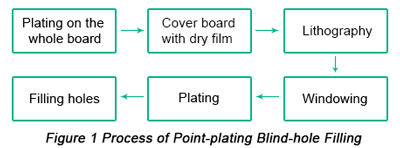

点镀盲孔填充工艺流程简介

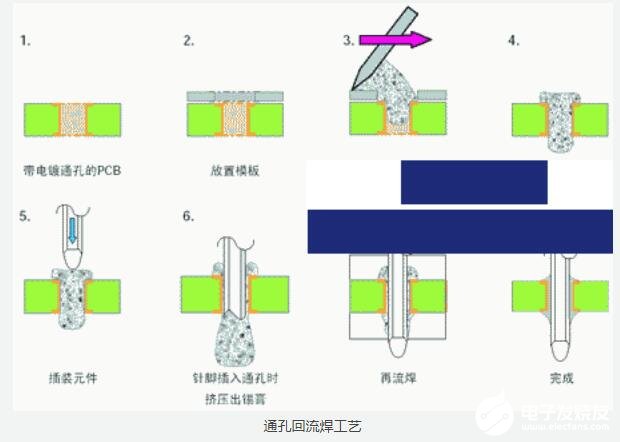

通孔回流焊工艺原理_通孔回流焊接工艺的优缺点

何时使用通孔技术工艺?

PCB导电孔塞孔工艺的实现

PCB线路板导电孔塞孔工艺的实现

互连/接触/通孔/填充分别代表了什么

接触孔工艺简介

接触孔工艺简介

评论