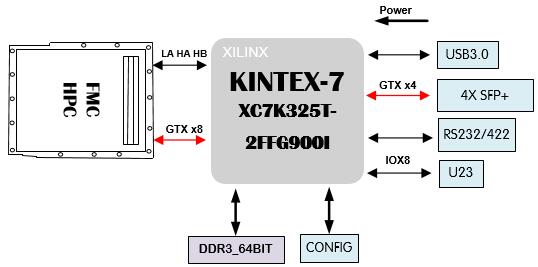

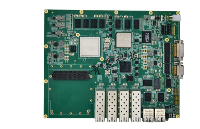

的Kintex-7系列FPGA JFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在

2025-12-19 17:48:31

3uvpx板卡, DA输出核心板, RFSOC, XCVU9P芯片, 信号输出播放, 硬件加速卡, 3U VPX板卡

2025-12-18 14:18:51 242

242

探索VITA 57.1 FMC扩展卡:FPGA开发的得力助手 在电子工程师的日常工作中,FPGA(现场可编程门阵列)开发是一个重要的领域。而在FPGA开发过程中,I/O扩展是常常会遇到的需求。今天

2025-12-18 11:25:20 177

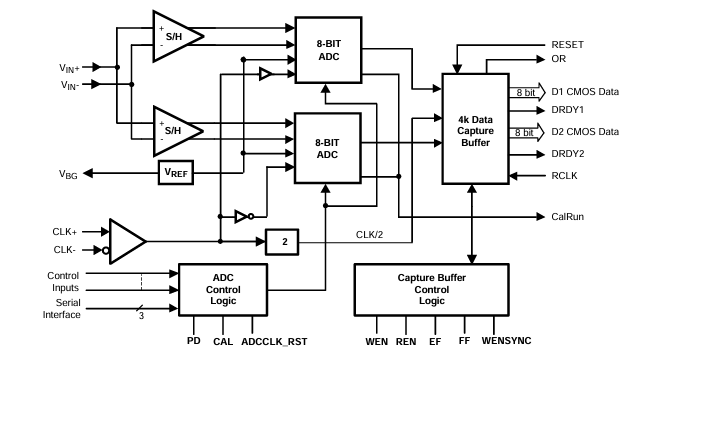

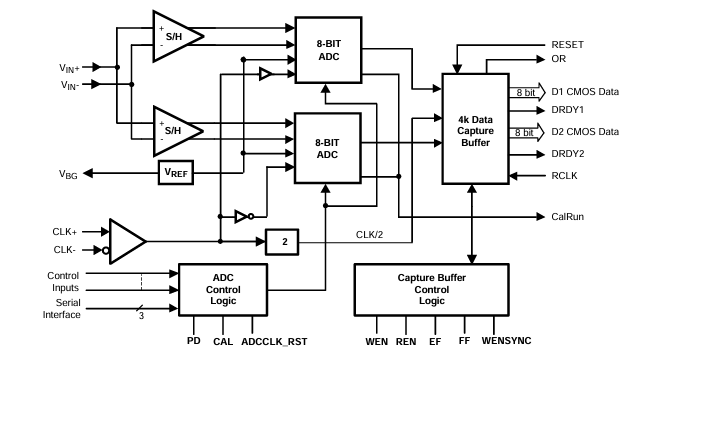

177 在电子工程师的设计世界里,A/D转换器是至关重要的组件之一。今天,我们将深入探讨德州仪器(TI)的ADC08B3000,这是一款8位、3GSPS的高性能、低功耗A/D转换器,它在众多领域都有

2025-11-26 17:43:49 728

728

终端兼容的 DAC37J84/DAC38J84 系列是一款低功耗、16 位、四通道、 1.6/2.5 GSPS 数模转换器 (DAC),带JESD204B接口。

数字数据通过 1、2、4 或

2025-11-13 14:31:02 472

472

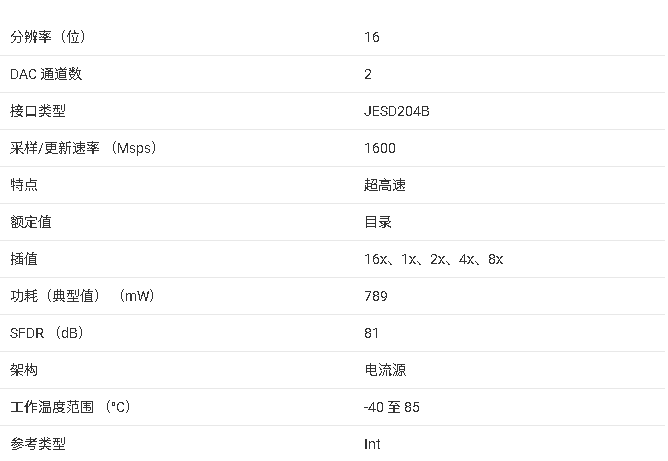

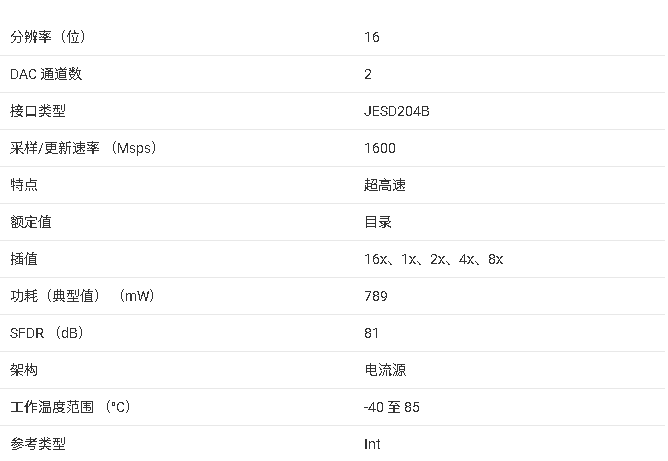

引脚兼容的DAC37J82/DAC38J82系列是一款非常低功耗、16位、双通道、 1.6/2.5 GSPS 数模转换器 (DAC),带JESD204B接口。最大输入数据速率 是 1.23 GSPS

2025-11-13 13:52:47 434

434

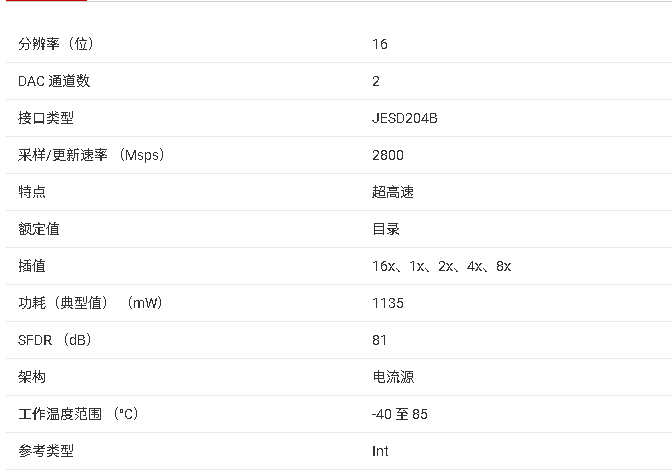

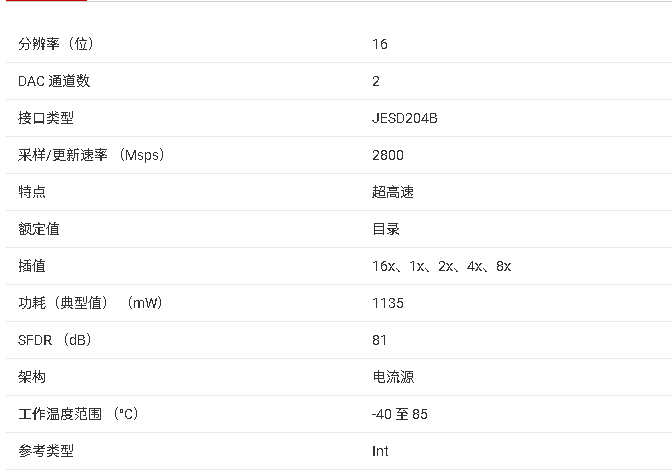

该DAC39J82是一款非常低功耗、16 位、双通道、2.8 GSPS 数模 具有JESD204B接口的转换器 (DAC)。最大输入数据速率为1.4 GSPS。

数字数据通过 1、2、4 或

2025-11-12 11:32:03 547

547

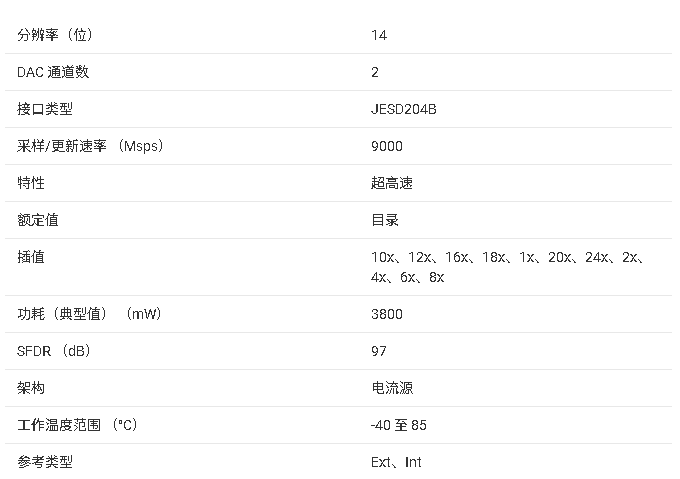

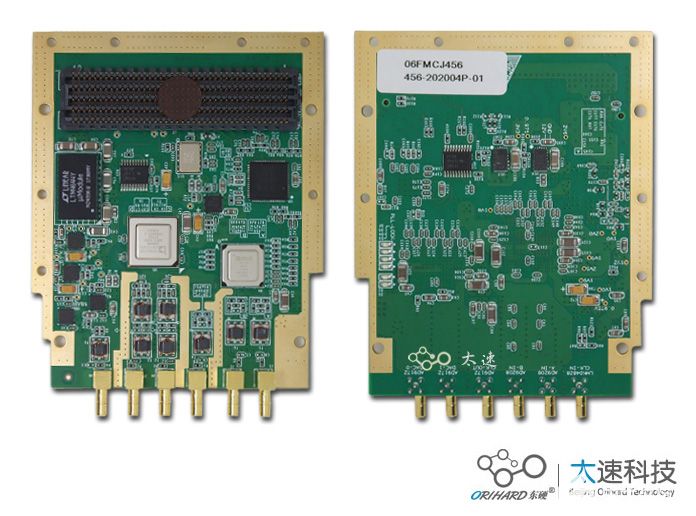

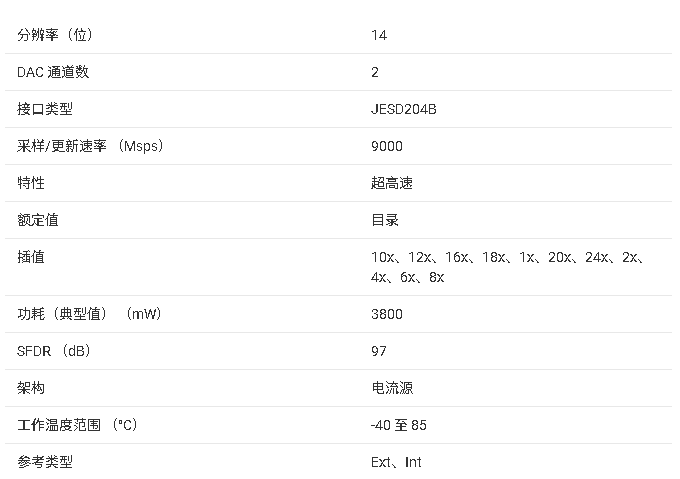

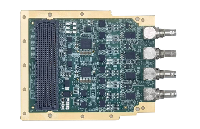

板卡概述FMC163是一款基于VITA57.1标准的实现2路14-bit、3GSPS ADC采集功能、2路14-bit 12GSPS DA回放FMC子卡模块。该模块遵循

2025-11-11 15:23:45

JESD204B接口,最大比特率为12.5 Gbps (DAC38RF89)和12.8 Gbps (DAC38RF82)。

2025-11-06 15:53:50 445

445

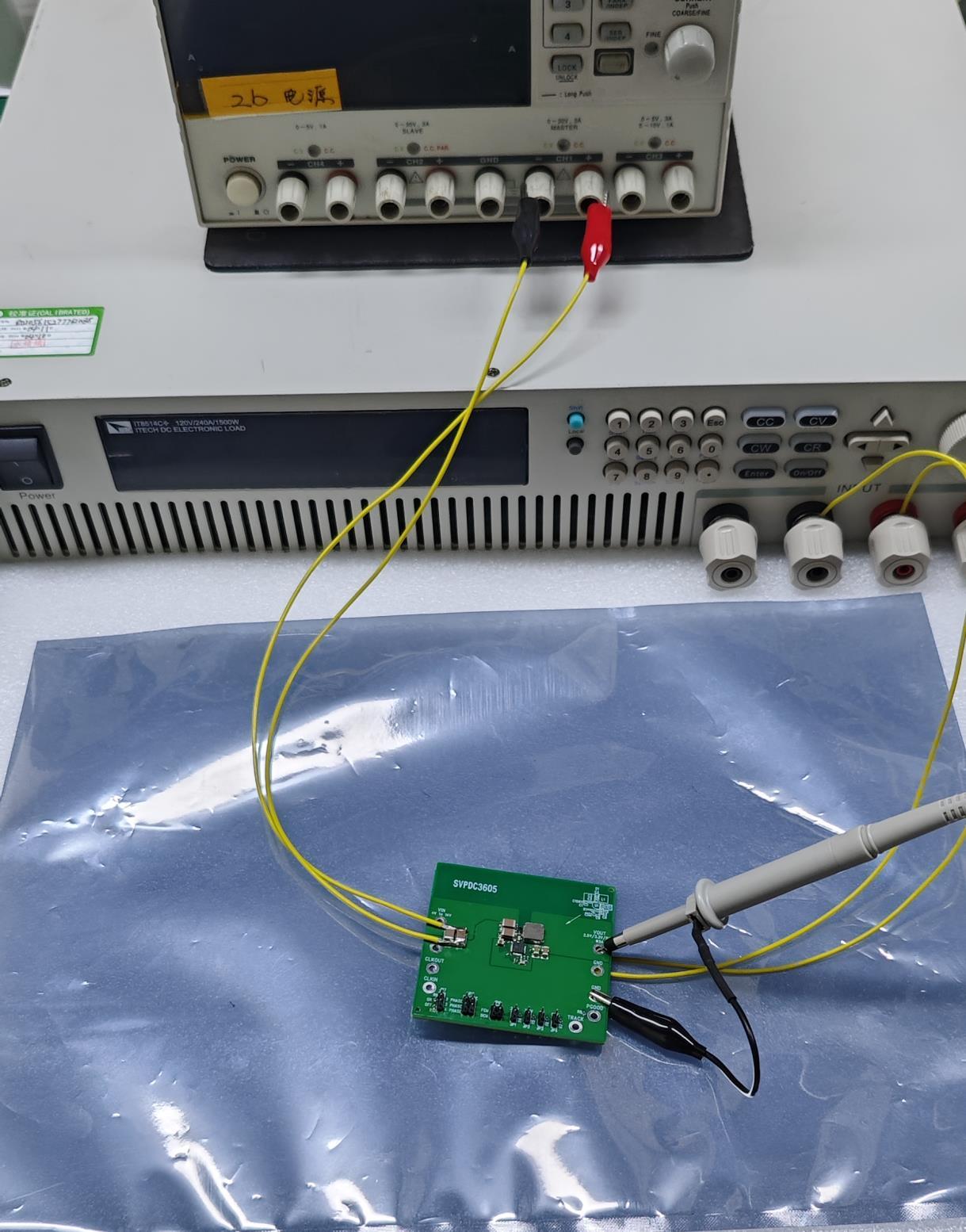

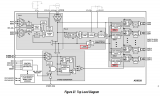

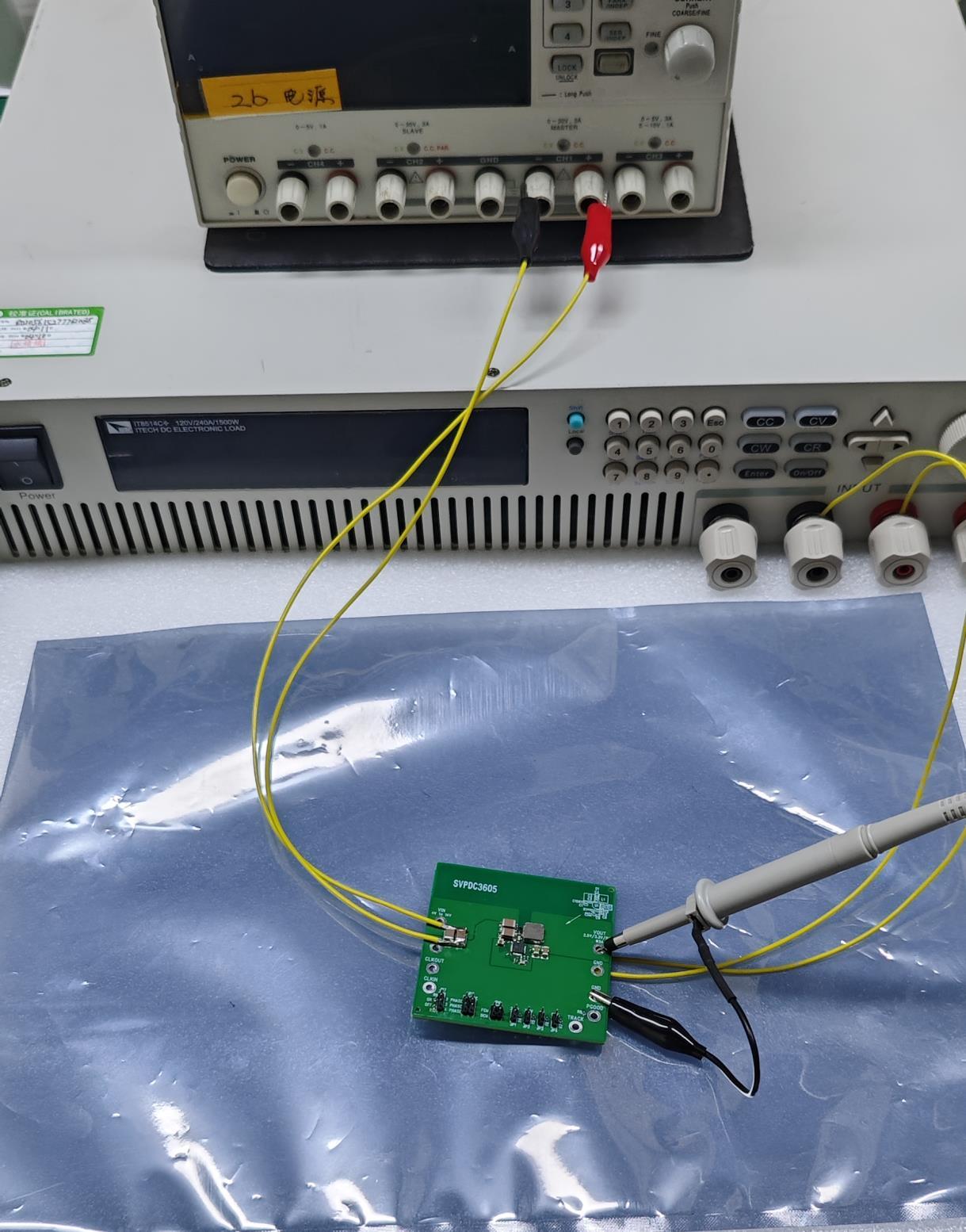

摘要 :本文以国科安芯推出的ASP3605A同步降压调节器为例,讨论其在高速模数转换器(ADC)子卡中的适配性。文章首先概述了高速ADC对电源管理的苛刻要求,包括电源精度、纹波控制、动态响应和热管

2025-10-23 17:53:58 190

190

板卡概述FMC163是一款基于VITA57.1标准的实现2路14-bit、3GSPS ADC采集功能、2路14-bit 12GSPS DA回放FMC子卡模块。该模块遵循VITA57.1标准,可直接

2025-10-22 16:21:09

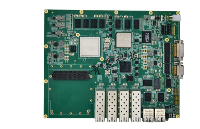

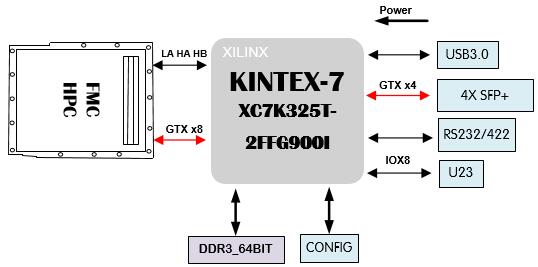

Xilinx的Kintex-7系列FPGA XC7K325T作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,处理节点之

2025-10-21 16:13:57 871

871

Xilinx的Kintex-7系列FPGA XC7K325T作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,处理节点之

2025-10-21 15:57:10

CameraLink图像模拟源, FMC子卡, FMC子卡模块, 万兆网络的触发采集, 中频信号采集

2025-10-21 11:02:58 313

313

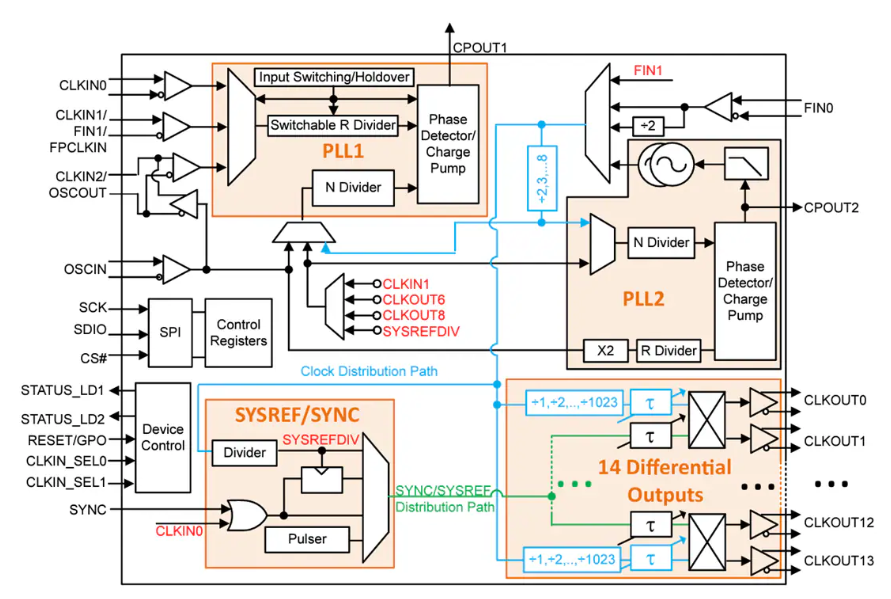

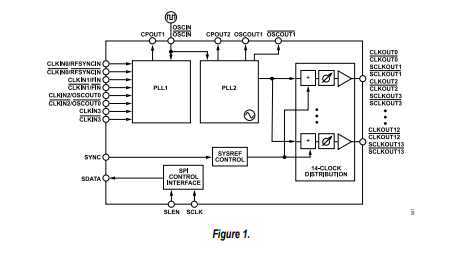

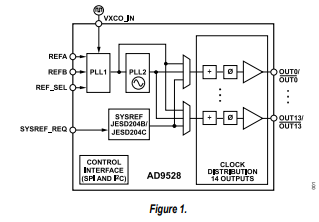

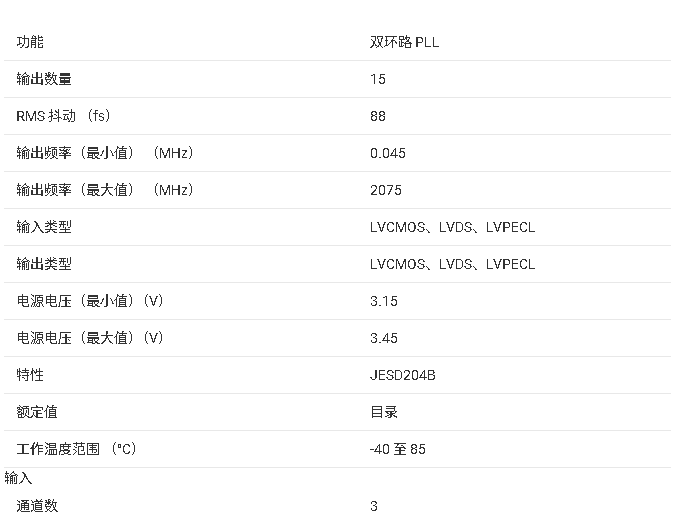

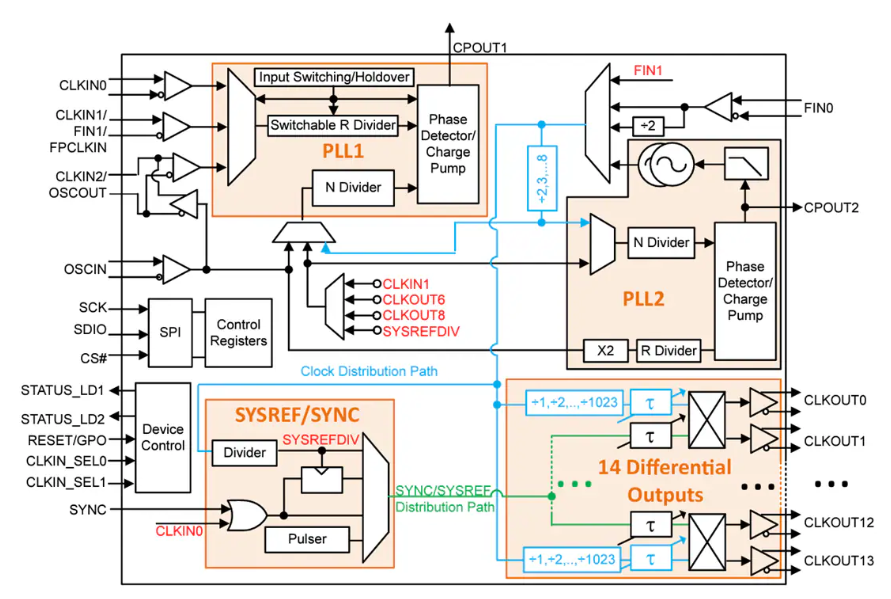

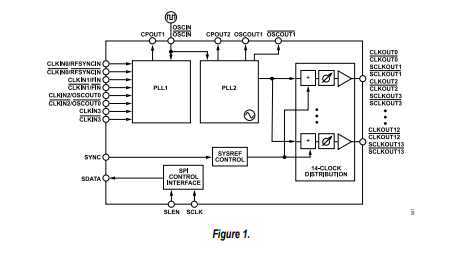

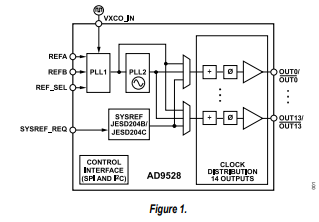

AD9528是一款双级PLL,集成JESD204B SYSREF发生器,可用于多器件同步。

2025-10-15 10:24:53 1197

1197

飞凌嵌入式FET153-S核心板配备3路千兆以太网接口、2路CAN-FD接口和Local Bus,支持高吞吐量网络连接,满足复杂数据驱动型应用需求。此外,T153处理器还提供10路UART、24路GPADC、6路TWI接口、30路PWM等接口,这些接口为多样化应用提供灵活性。

2025-10-10 11:40:54 2218

2218

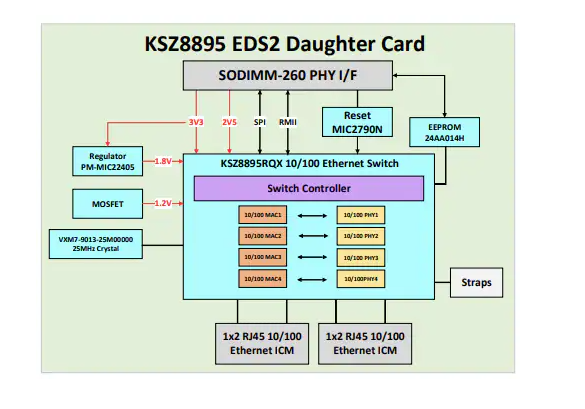

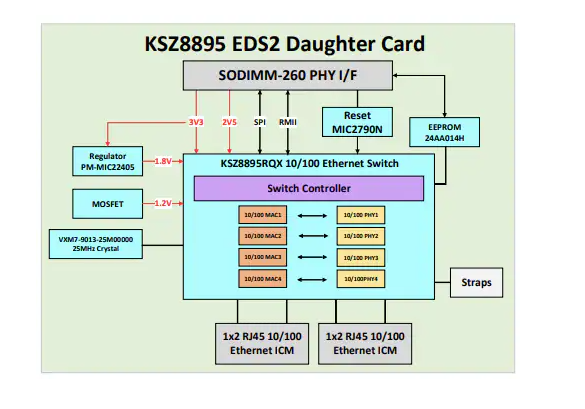

Microchip Technology KSZ8895 EDS2子卡设计用于评估KSZ8895千兆以太网RGMII交换机,需搭配兼容EDS2的主板使用。此卡配备VXM7-9013-25M0000

2025-10-06 15:33:00 1107

1107

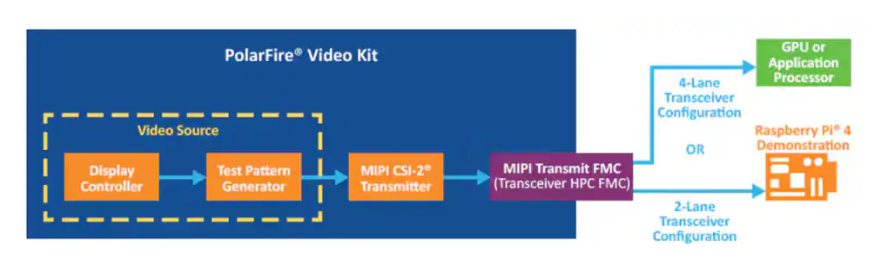

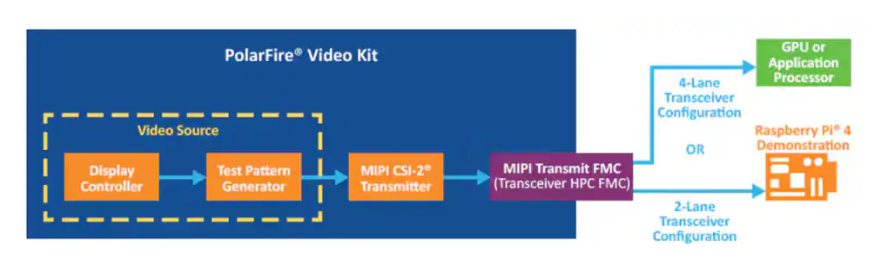

Microchip Technology VIDEO-DC-MIPITX CSI-2 MIPI Transmit FMC卡采用PolarFire^®^ 和PolarFire SoC FPGA

2025-09-29 10:10:26 629

629

PCIe数据卡, VU9P, VU9P板卡, VU9P处理板, VU9P核心板

2025-09-19 09:36:06 448

448

Camera Link 输出子卡, K7软件无线电处理平台, 软件无线电处理, 软件无线电处理平台

2025-09-18 11:05:22 609

609

的Kintex-7系列FPGAJFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在FP

2025-09-16 16:59:19 1236

1236

的Kintex-7系列FPGA JFM7K325T16作为协处理单元,具有1个FMC子卡接口,具有4路SFP+万兆光纤接口,具有2路RJ45千兆以太网接口,其中1路挂在

2025-09-16 16:54:30

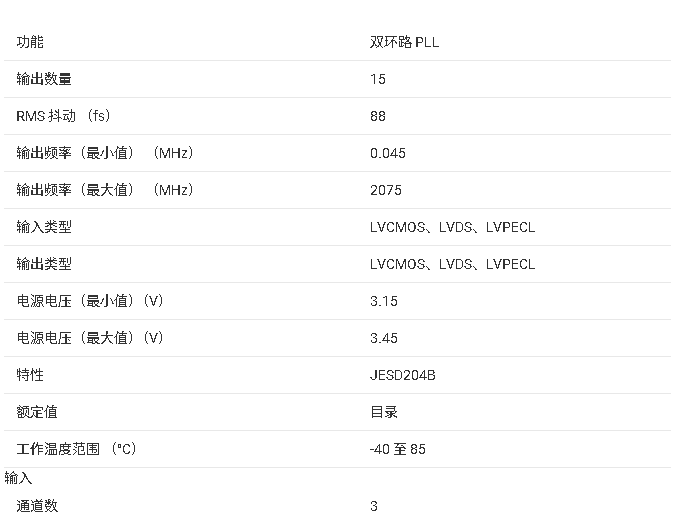

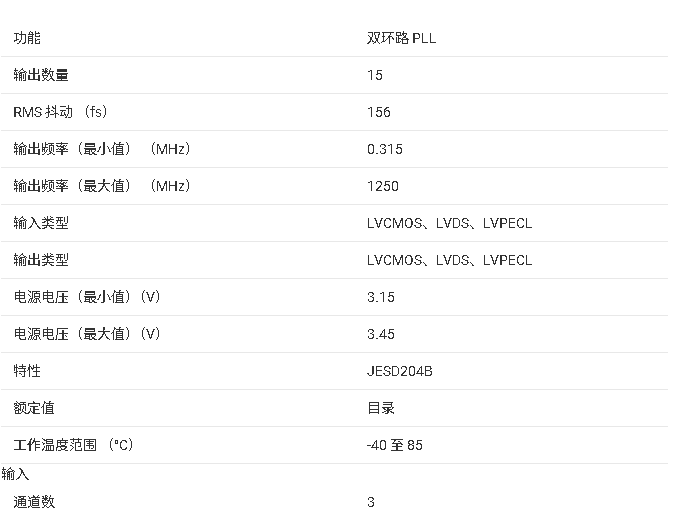

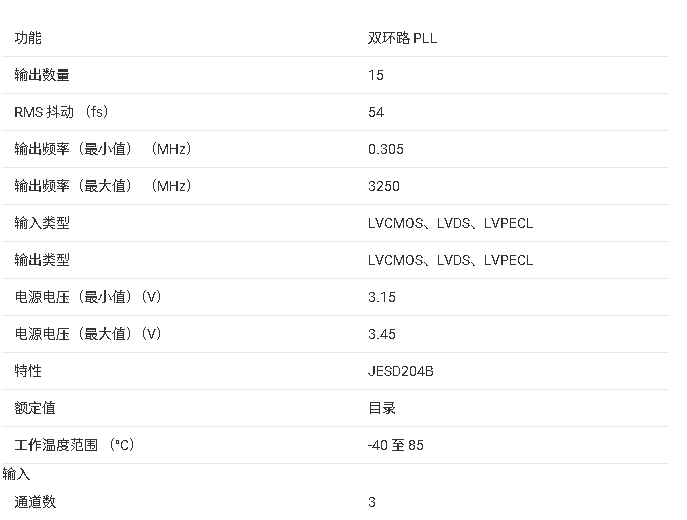

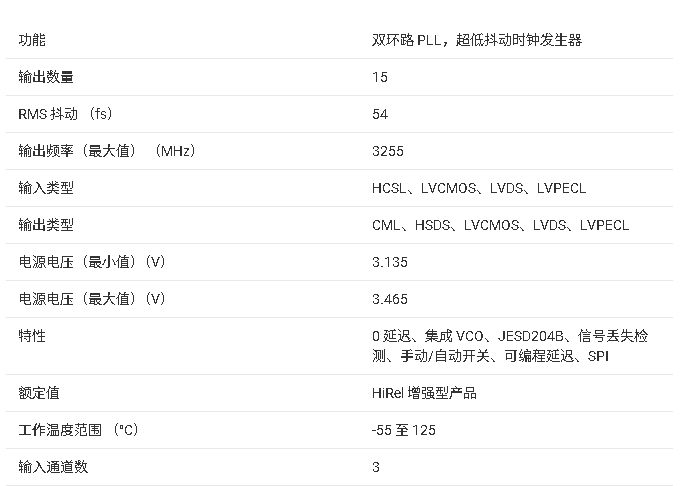

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

2025-09-15 10:10:11 848

848

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

2025-09-15 10:03:34 665

665

LMK0482x 系列是业界性能最高的时钟调节器,支持 JEDEC JESD204B。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个 JESD204B

2025-09-14 11:07:35 901

901

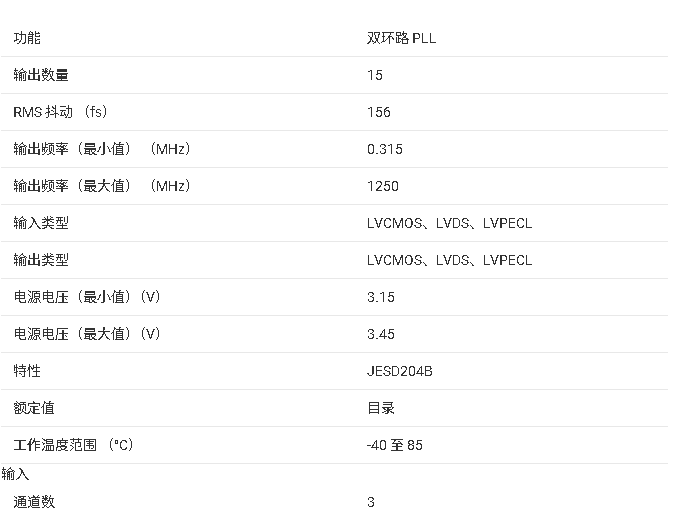

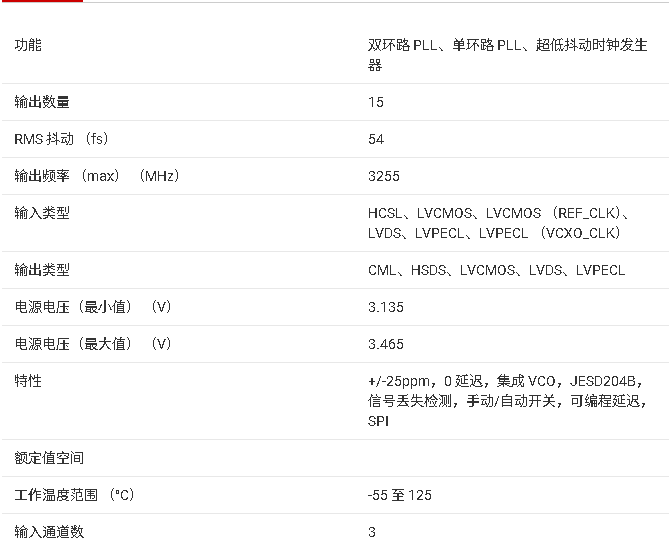

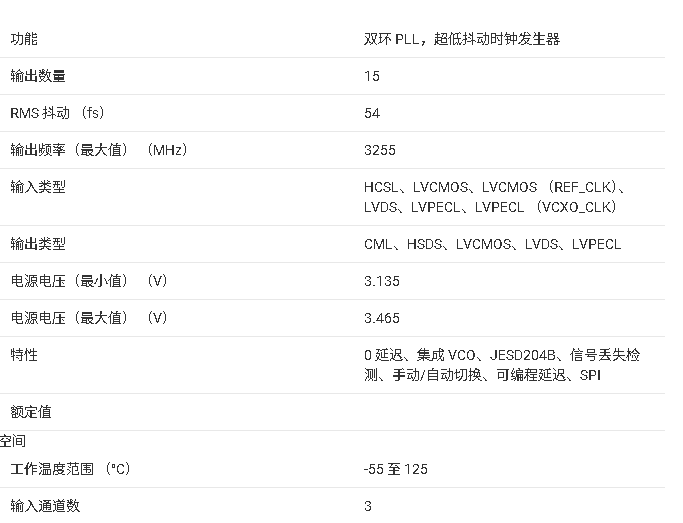

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。

2025-09-13 09:35:35 1028

1028

LMK0461x 器件系列是业界性能最高、功耗最低的抖动清除器,支持 JESD204B。16 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 8 个 JESD204B 转换器或其他逻辑器件。第 17 个输出可配置为提供来自 PLL2 的信号或来自外部 VCXO 的副本。

2025-09-12 16:50:34 907

907

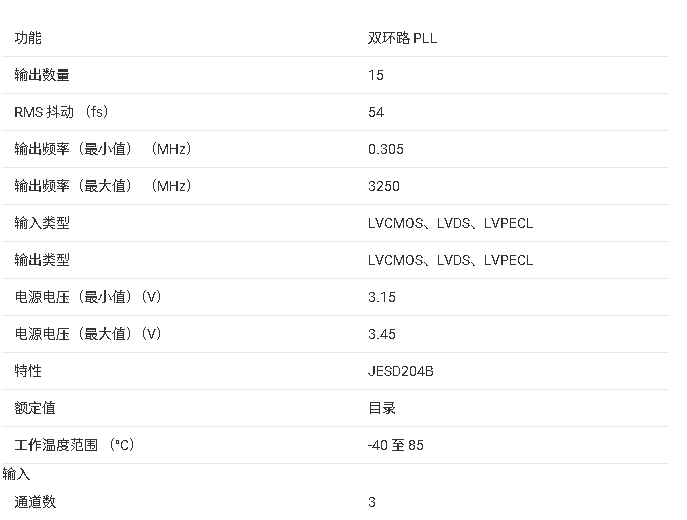

LMK04828-EP 器件是业界性能最高的时钟调理器,支持 JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件

2025-09-12 16:13:11 831

831

LMK04228 器件是业界高性能时钟调节器,支持 JEDEC JESD204B。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或其他逻辑器件

2025-09-12 15:02:13 611

611

该LMK04832是一款超高性能时钟调节器,支持 JEDEC JESD204B,还与 LMK0482x 系列器件引脚兼容。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个

2025-09-12 14:11:12 929

929

LMK04832-SP 是一款高性能时钟调节器,支持 JEDEC JESD204B,适用于太空应用。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B转换器或

2025-09-11 18:19:56 875

875

LMK04832-SEP 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2的14个时钟输出可配置为使用器件和SYSREF时钟驱动7个JESD204B

2025-09-11 10:43:33 649

649

LMK04368-EP 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个

2025-09-11 10:23:20 652

652

LMK04714-Q1 是一款高性能时钟调节器,支持 JEDEC JESD204B/C,适用于太空应用。

PLL2 的 14 个时钟输出可配置为使用器件和 SYSREF 时钟驱动 7 个

2025-09-11 10:07:11 560

560

)。

3. Subclass 2(严格子类)

• 同步机制 :

采用 SYSREF 周期性触发 + 严格时钟对齐的双重机制,是 JESD204B 中最严格的同步规范。

•SYSREF 需为周期性、低抖动、相位

2025-09-05 21:18:18

FMC213 是我司自主研制的一块基于 FMC 标准的 8 路万兆光纤 子卡模块。该板卡符合 VITA57.1 标准,该板卡可以作为一个理想的 IO模块耦合至FPGA前端,8路SFP+的高速串行信号

2025-09-02 11:27:51 496

496

FMC213 是我司自主研制的一块基于 FMC 标准的 8 路万兆光纤 子卡模块。该板卡符合 VITA57.1 标准,该板卡可以作为一个理想的 IO模块耦合至FPGA前端,8路SFP+

2025-09-02 11:24:23

该板卡支持 SDI 双向输入/输出,可以通过配置实现输入或者输出的切换。

该 FMC 子卡与基于 Xilinx FPGA 开发板配合,快速搭建起高速SDI 视频图像传输的验证平台,可广泛适用于 4K 图像处理等应用场景。

2025-08-27 15:13:46 880

880

产品概述FMC214 是我司自主研制的一块基于 VITA57.1 标准的 4 路3G/6G/12G SDI 高清视频传输 FMC 子卡模块,该板卡可以作为一个理想的 IO 单元耦合至 FPGA 前端

2025-08-27 11:32:57

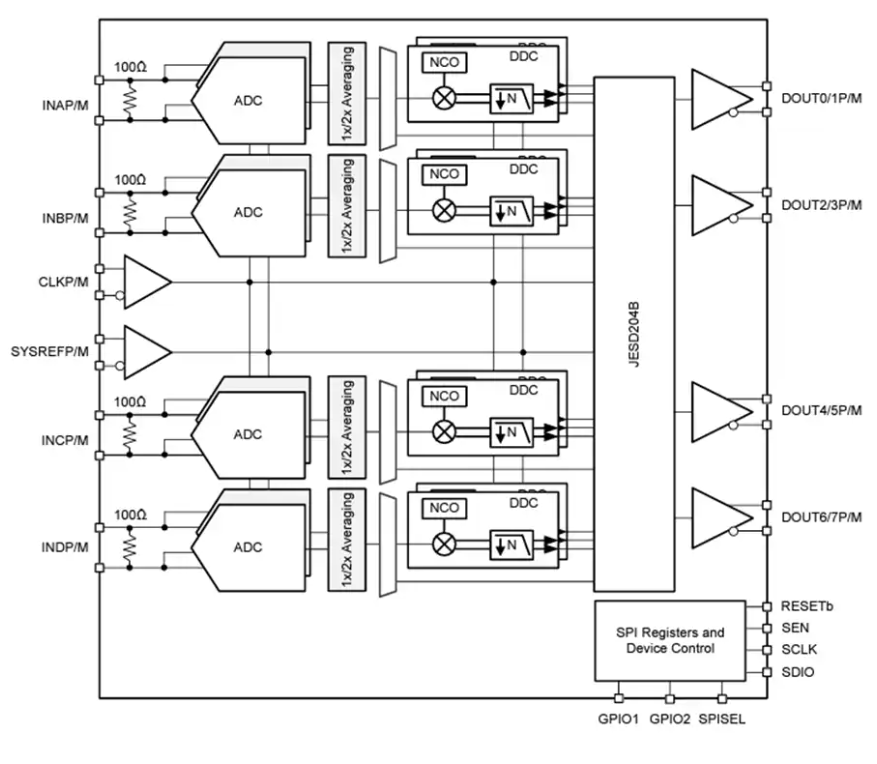

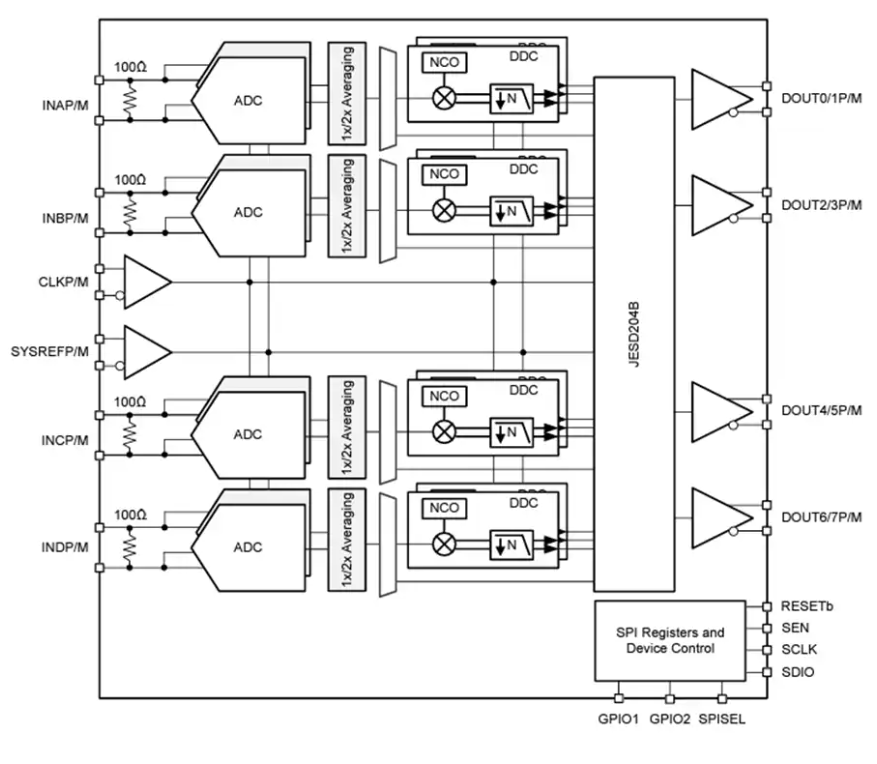

Texas Instruments ADC34RF55 14位RF采样模数转换器(ADC)是一款单核14位、3GSPS、四通道ADC,支持RF采样,输入频率高达3GHz。该设计的噪声频谱密度为

2025-08-14 15:37:13 1137

1137

Texas Instrument LMK04714-Q1双环时钟抖动清除器是一款高性能时钟调节器,支持JEDEC JESD204B/C,适用于航天应用。PLL2的每个14时钟输出均可配置为驱动七个

2025-08-08 15:05:57 843

843

(如医疗成像)三、TI替代方案1. DAC38J84(DDS+高速DAC)- 关键参数:- 1.5GSPS DAC,支持数字正交上变频- 可配置为DDS模式,支持相位连续跳频- JESD204B接口

2025-08-08 09:53:07

FMC-1AD2DA是我司自主研发的一款1路1G AD采集、1路2.5G DA回放的FMC子卡。板卡采用标准FMC子卡架构,可方便的与其他FMC板卡实现高速互联,可广泛用于高频模拟信号采集、雷达系统测试等场合。 AD DA FMC子卡 , AD采集卡 , 高密度计算 , 高速信号采集卡 ,

2025-08-07 11:02:53 765

765

3U VPX, FMC子卡, JFM7K325T板卡, 软件无线电处理平台, 数据采集IO卡

2025-08-01 10:20:27 1019

1019

DDR3,每组容量4GB,一个HPC FMC接口。VPX接口连接4组x4 GTH,24组LVDS,一路RS422,一路1000Base-T。板卡的电气与机械设计依据VPX标准(VITA 46.0

2025-08-01 10:13:45 890

890

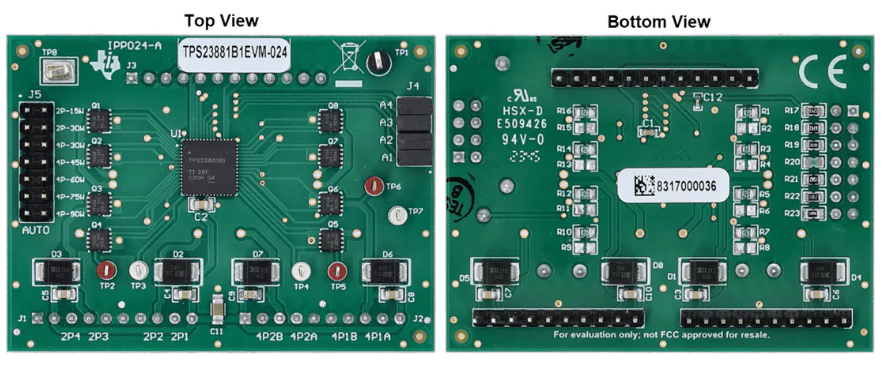

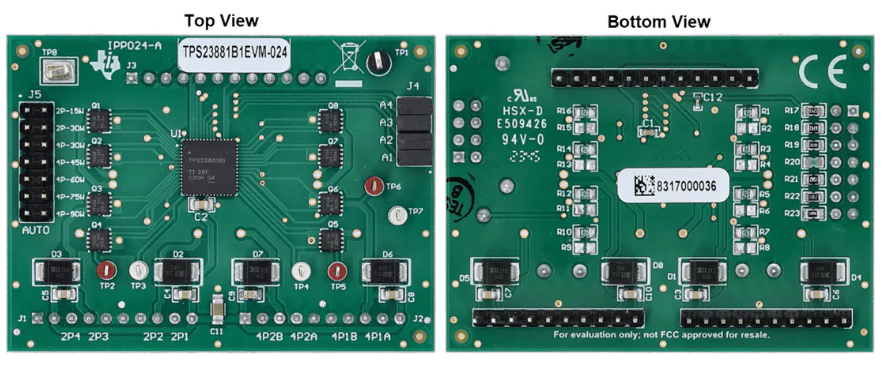

Texas Instruments TPS23881B1EVM-024子卡设计用于评估具有自主模式的四对、四类、八通道以太网供电(POE)PSE TPS23881B。该子卡为Texas Instruments TPS23881B器件提供了评估和参考电路,适用于大功率PSE应用。

2025-07-30 09:50:20 601

601

LTM4644第一路输出1.9V,第二路输出1.5V,第三和第四路并联使用,输出3.3V,原理图如图片所示,实际测试发现,3,4路输出9.3V,断开反馈电阻,FB引脚电压从0.4V缓慢升到1V

2025-07-14 06:22:07

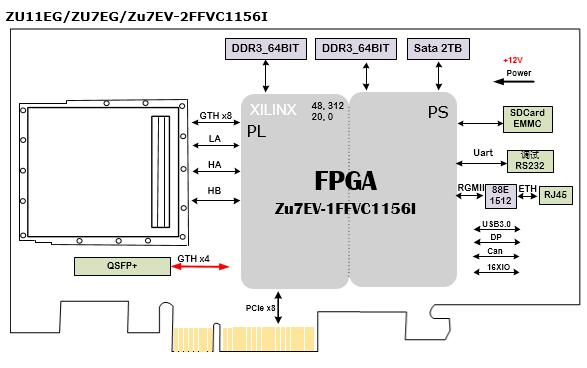

XCZU7EV 通用PCIe卡 , 图像信号分析处理卡 , 视觉处理卡 , 工业控制卡 , 存储扩展卡

2025-07-08 10:47:25 1161

1161

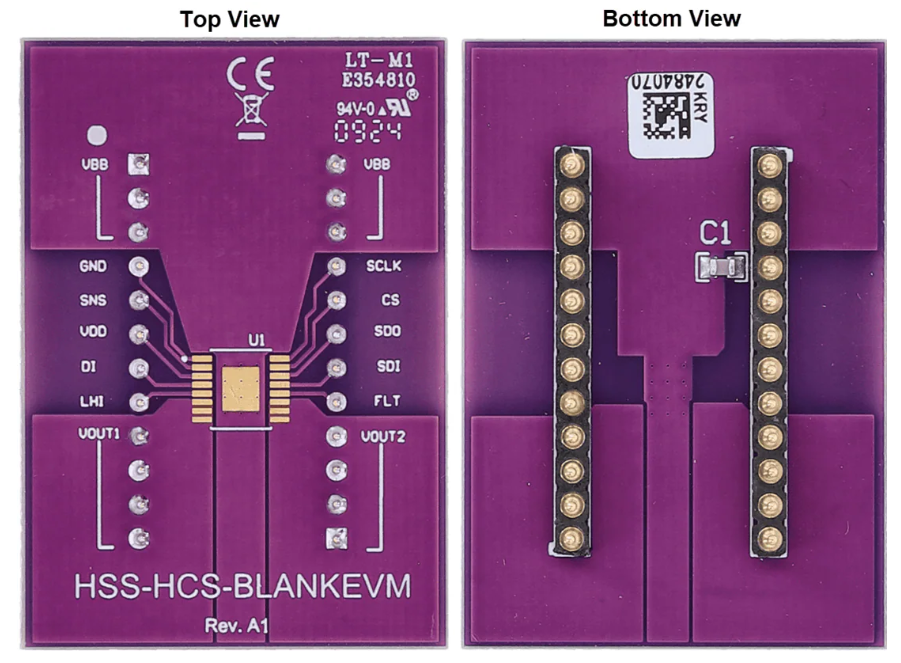

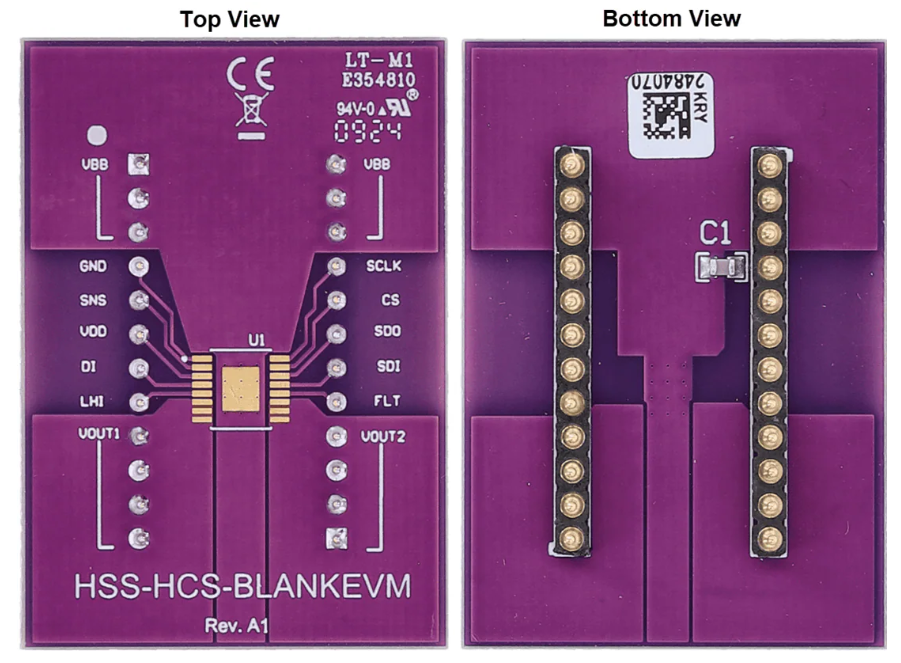

Texas Instruments HSS-HCS-BLANKEVM智能保险丝子卡设计用于与智能保险丝评估模块HSS-HCMOTHERBRDEVM搭配使用。这些工具组合展示了TI智能保险丝产品组合的功能。该空白子卡在运行破坏性测试时非常有用,可与任何兼容的HCS高侧开关配合使用。

2025-07-04 11:39:46 665

665

3U PXIe, FMQL45T900I, K7图形图像硬件加速器, PXIe接口卡, JFM7K325T 芯片

2025-07-03 14:13:51 552

552

, 数字信号处理卡, FMC接口通用计算平台, FMQL45T900I, 前端信号处理

2025-07-03 11:23:35 489

489

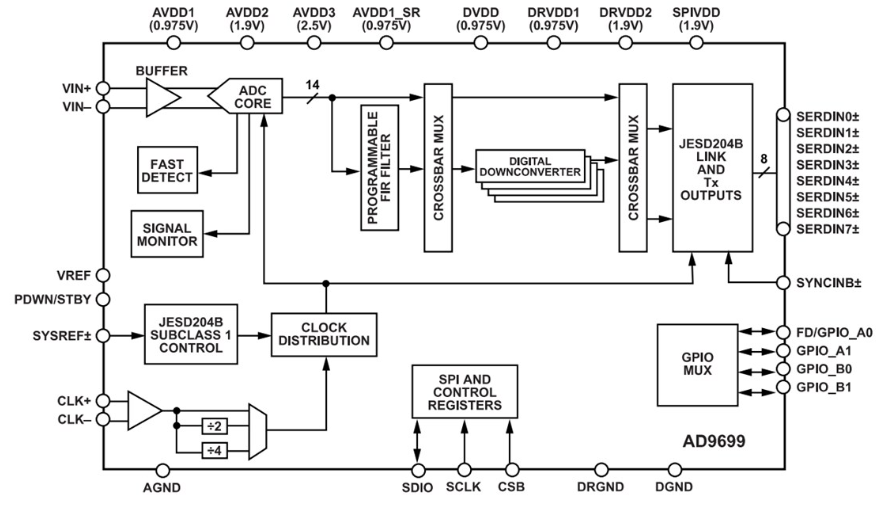

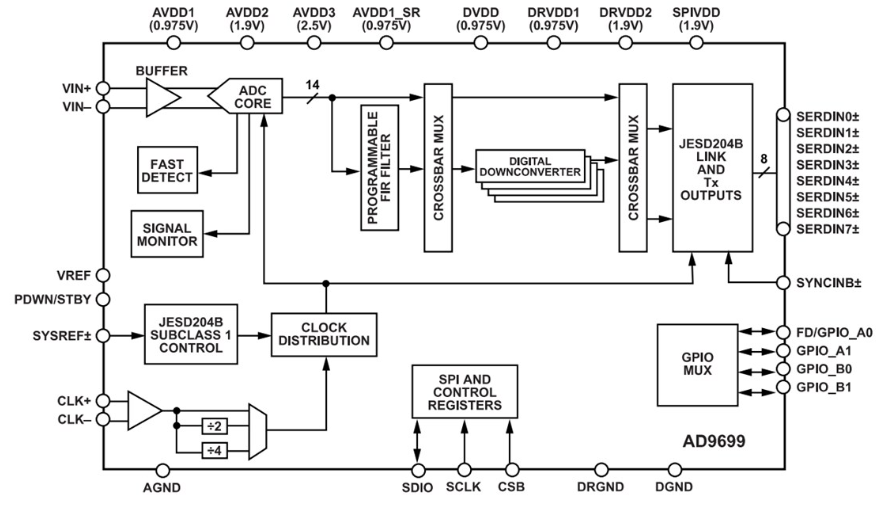

Analog Devices Inc. AD9699 14位3GSPS模数转换器 (ADC) 内置片内缓冲器和采样保持电路,设计实现低功耗、小尺寸以及简单易用。该产品设计支持能够直接采样高达5GHz

2025-06-25 13:45:32 672

672

芯片型号是XC7Z020CLG484-2I。开发板由核心板+底板组成,外设资源丰富,板载2路千兆以太网接口、一个FMC LPC座,HDMI输入和输出接口、LVDS LCD接口、音频接口和RGB LCD

2025-05-30 16:55:44

实用JESD204B来自全球数据转换器市场份额领导 者的技术信息、提示和建议

2025-05-30 16:31:21 0

0 物理层的位置,一种是物理层在JESD204 IP里;另外一种是物理层在JESD204 IP外部,需要再配置JESD204 phy IP核进行使用。

2025-05-24 15:05:00 1827

1827

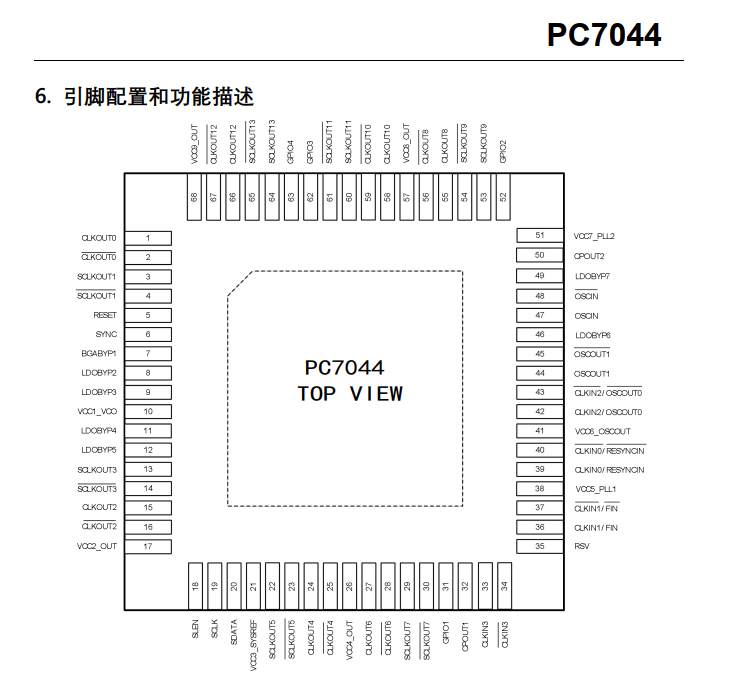

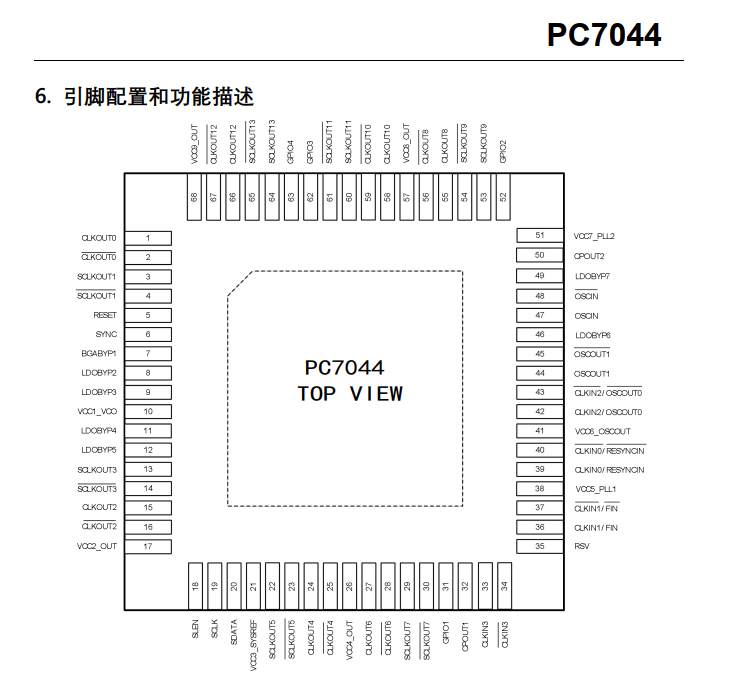

1. 概述 PC7044 是一款高性能双环路的整数时钟抖动消除器,可以为具有并行或串(JESD204B 型)接口的高速数据转换器执行参考时钟选择和超低噪声频率的生成。 PC7044 具有两个整数

2025-05-08 16:01:36 655

655

VCO 输入,支持高达 3200MHz车载调节器可实现出色的电源抑制比3. 应用• JESD204B 时钟生成• 蜂窝基础设施(多载波 GSM、 LTE、 W-CDMA)• 数据转换器时钟• 微波基带卡• 相控阵参考时钟分布

2025-05-08 15:57:20

基于通用PCIe ,实现FMC的数据接口和主控计算,广泛应用于工业控制,检测,视觉处理。支持工业级温度工作。

2025-05-07 09:10:28 814

814

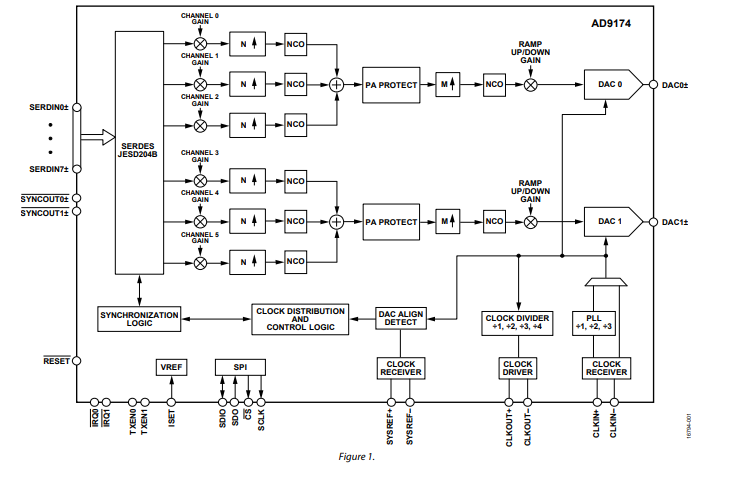

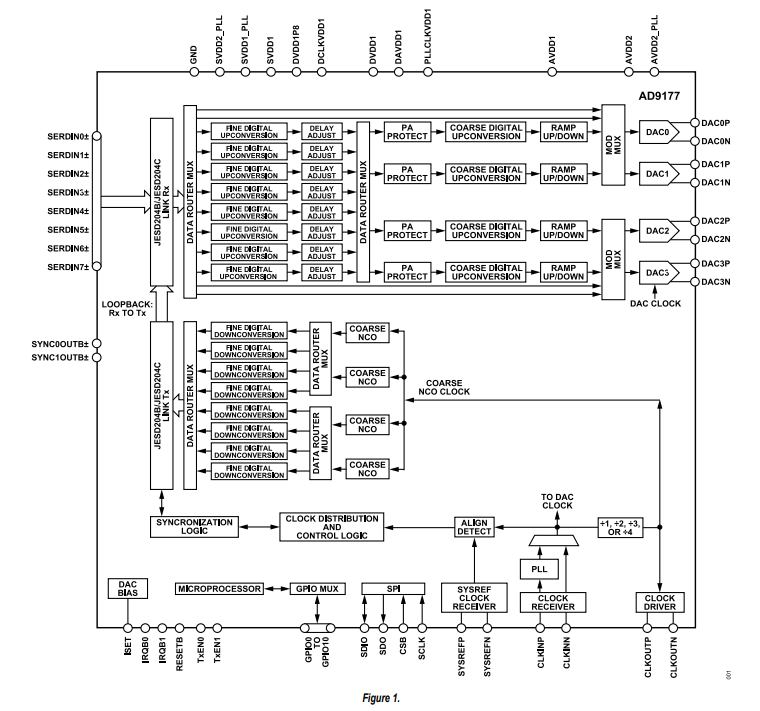

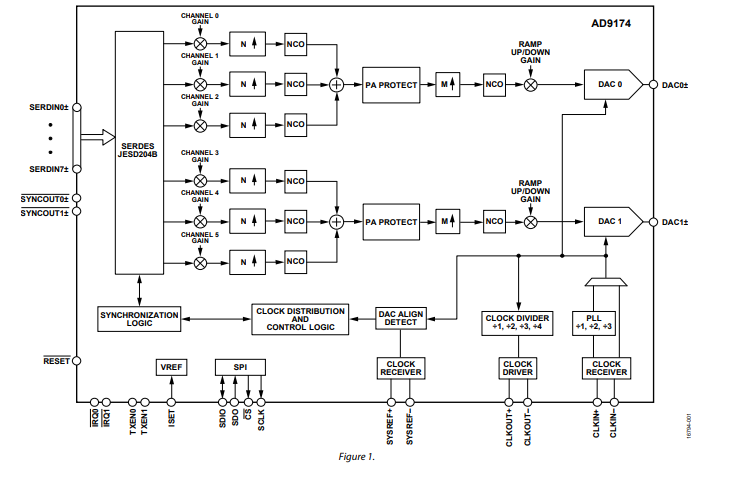

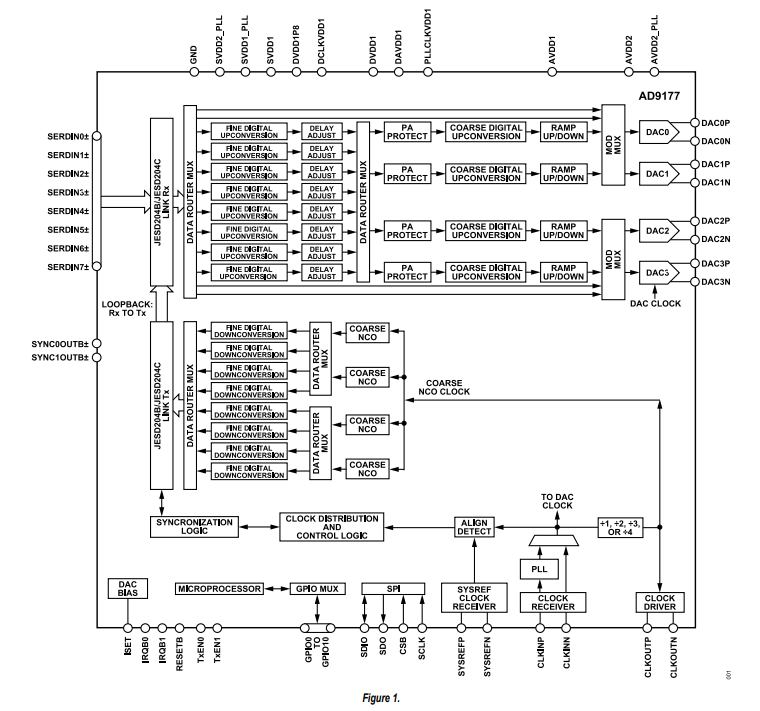

AD9174是一款高性能、双通道、16位数模转换器(DAC),支持高达12.6 GSPS的DAC采样速率。该器件具有8通道、15.4 Gbps JESD204B数据输入端口、高性能片内DAC时钟倍频器和数字信号处理功能,适合单频段和多频段直接至射频(RF)无线应用。

2025-04-30 15:42:42 1156

1156

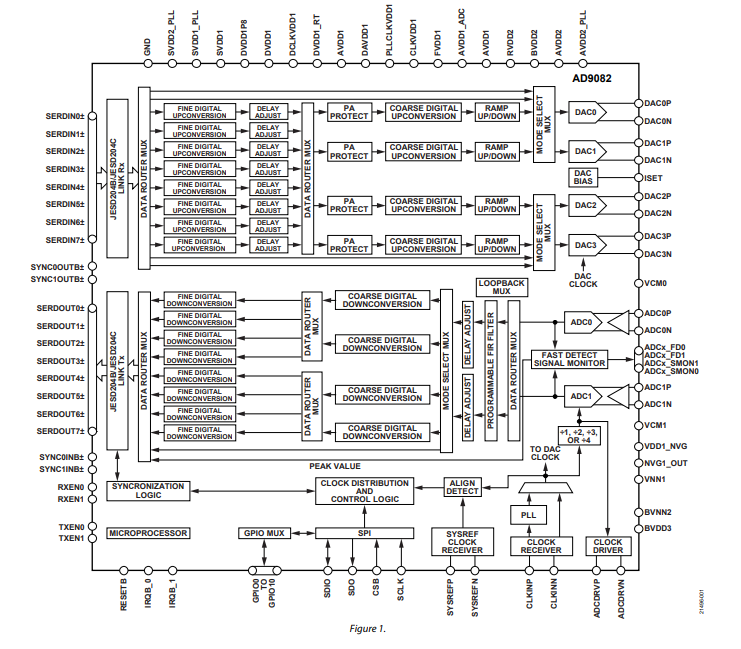

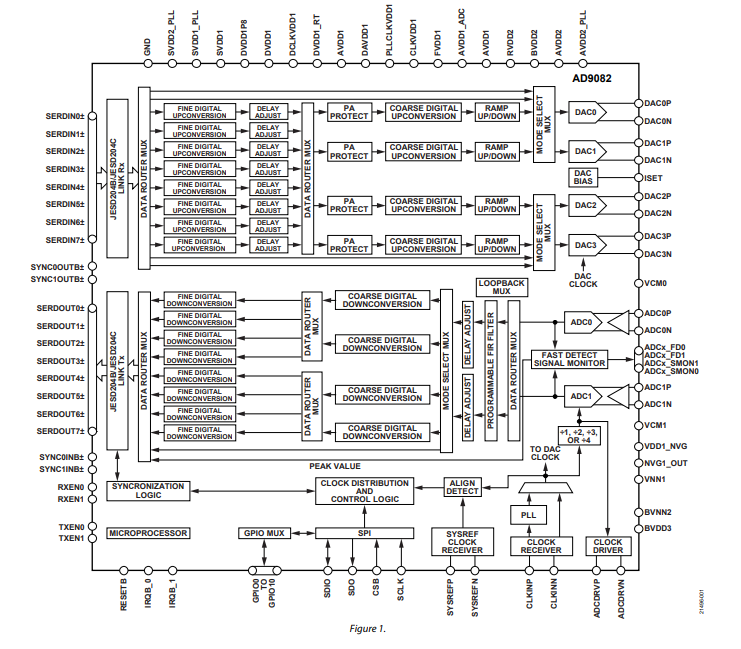

JESD204B数据收发器端口、片内时钟倍频器和数字信号处理(DSP)功能,适合宽带或多频段直接至RF应用。AD9082还具有旁路模式,允许ADC和/或DAC内核的全宽带功能旁路DSP数据路径。此器件还具有低延迟回送和跳频模式,适用于相控阵雷达系统和电子战应用。

2025-04-28 09:51:06 1123

1123

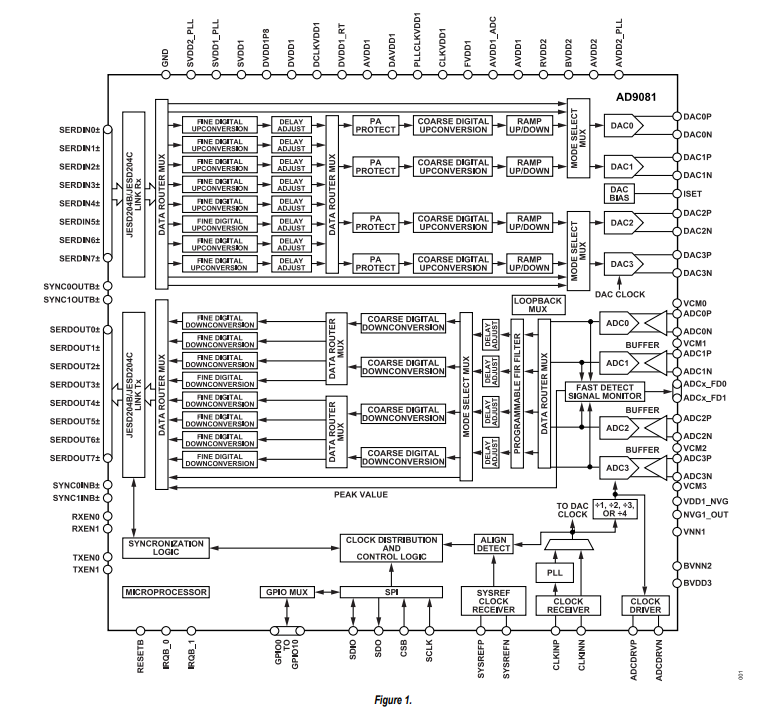

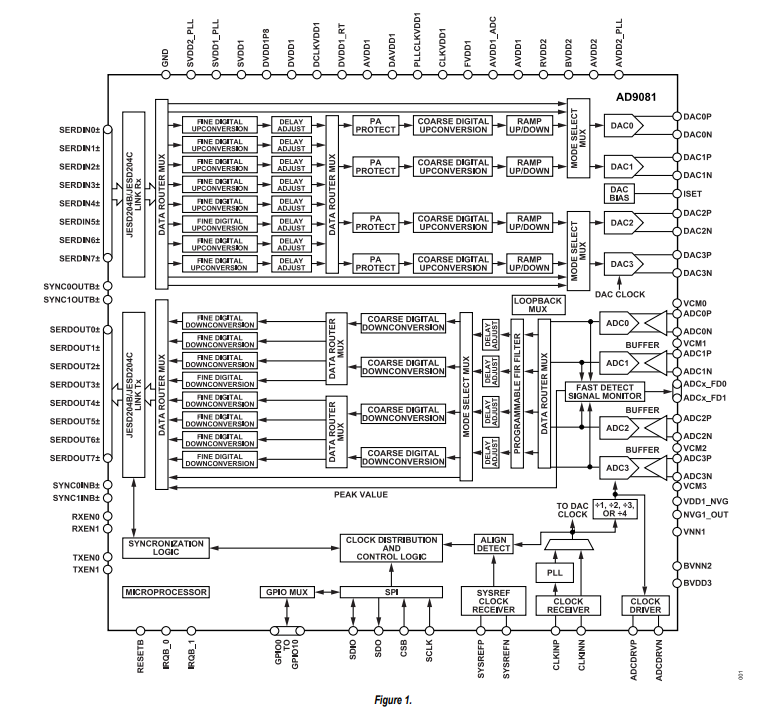

Gbps/通道 JESD204B 标准。该套件还具有片内时钟乘法器,以及直接针对 RF 应用的宽带或多频带数字信号处理(DSP)功能。可以绕过 DSP 数据路径,以允许转换器内核与 JESD204

2025-04-28 09:44:03 1128

1128

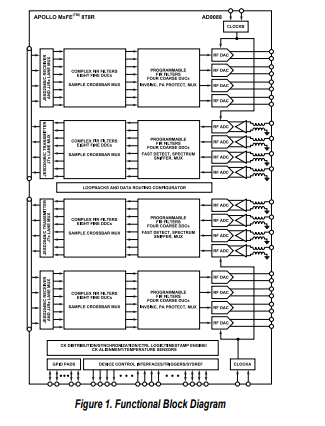

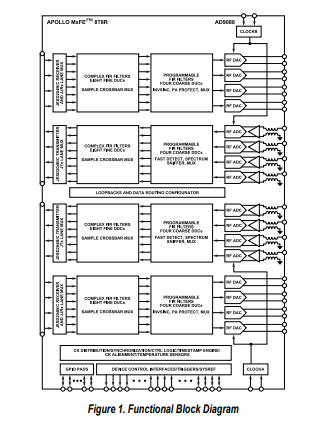

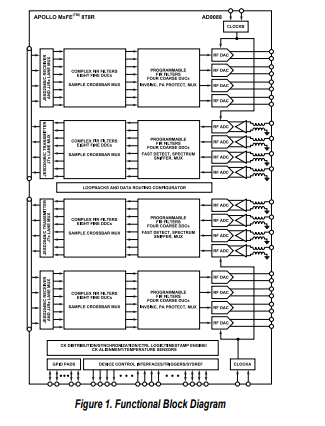

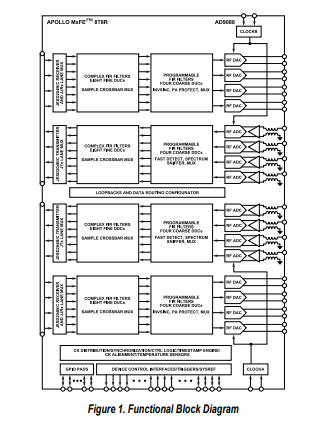

JESD204C 或 20 Gbps JESD204B 数据收发器端口、一个片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9088 还具有旁路模式,允许 ADC

2025-04-28 09:35:17 893

893

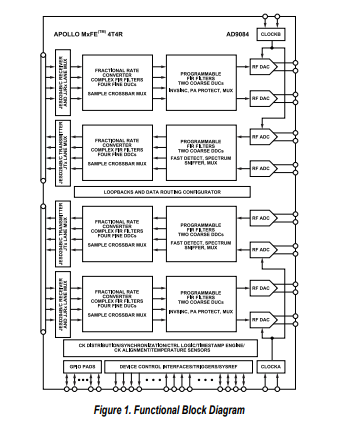

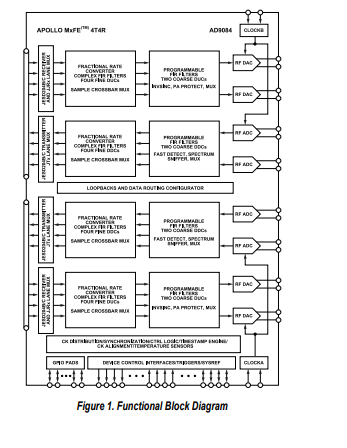

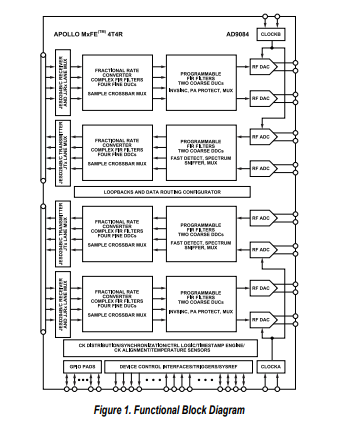

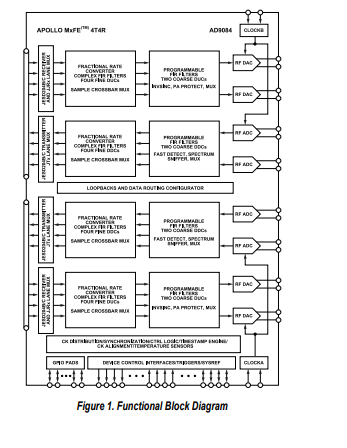

Gbps JESD204C 或 20 Gbps JESD204B数据收发器端口、片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9084 还具有旁路模式,允许

2025-04-28 09:32:20 1365

1365

JESD204B是逻辑器件和高速ADC/DAC通信的一个串行接口协议,在此之前,ADC/DAC与逻辑器件交互的接口大致分为如下几种。

2025-04-24 15:18:36 4481

4481

的应用。该套件具有 8 通道、24.75 Gbps JESD204C 或 15.5 Gbps JESD204B 数据接收器 (JRx) 端口、片内时钟乘法器和数字信号处理 (DSP) 数据通路,能够处理

2025-04-18 17:22:55 1026

1026

JESD204C 或 20 Gbps JESD204B 数据收发器端口、一个片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9088 还具有旁路模式,允许 ADC

2025-04-18 15:58:18 1055

1055

JESD204C 或 20 Gbps JESD204B数据收发器端口、片上时钟乘法器以及针对宽带或多频段、直接到 RF 应用的数字信号处理 (DSP) 功能。AD9084 还具有旁路模式,允许 ADC

2025-04-18 15:47:45 1770

1770

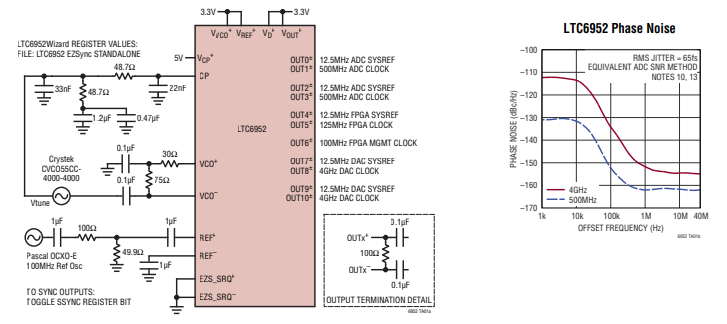

LTC6953 是一款高性能、超低抖动的 JESD204B/JESD204C 时钟分配 IC。LTC6953 的 11 个输出可配置为最多 5 个 JESD204B/JESD204

2025-04-16 14:28:18 1023

1023

HMC7044B 是 [HMC7044]的修订版本,是一款高性能、双环路、整数 N 抖动衰减器,能够为具有并行或串行(JESD204B 和 JESD204C 类型)接口的高速数据转换器执行参考选

2025-04-16 11:27:05 1623

1623

AD采集芯片为AD9680-1000,时钟芯片为AD9528。当 AD 采样时钟为 500MHz 时,jesd204B (串行线速 = 5 Gbps) 稳定。但是,当 AD 采样时钟为 800MHz

2025-04-15 06:43:11

来都来了,我们就来好好讲讲为什么万能的FPGA如此青睐FMC?WhyFMC?FMC即FPGAMezzanineCard(FPGA中间层板卡),由子板模块和载卡两部分构成。FMC载卡:为子板模块提供

2025-04-14 09:52:40 1404

1404

AD9528是一款双级PLL,集成JESD204B/JESD204C SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理

2025-04-10 10:19:13 1141

1141

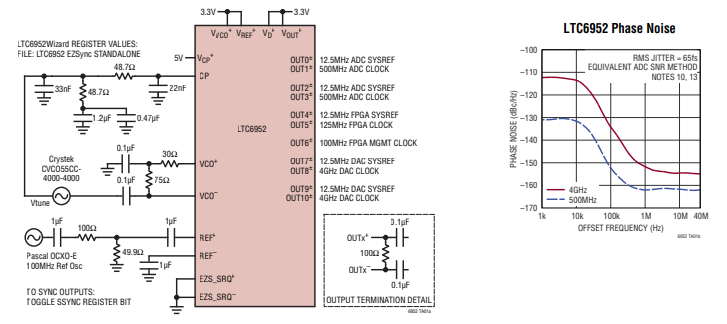

LTC6952 是一款高性能、超低抖动 JESD204B/C 时钟生成和分配 IC。该器件包括一个锁相环 (PLL) 内核,由基准分频器、具有锁相指示器的相位频率检波器 (PFD)、超低噪声充电

2025-04-09 17:26:48 830

830

全互联,可适配各种FMCAD/DA卡,可适配国内外标准的各种FMC或FMC+子卡

GTH速率:≥10Gbps

单电源+12V供电,(具有独立电源输入连接器接口);

使用50A电源对其供电,保证在

2025-04-09 11:25:05

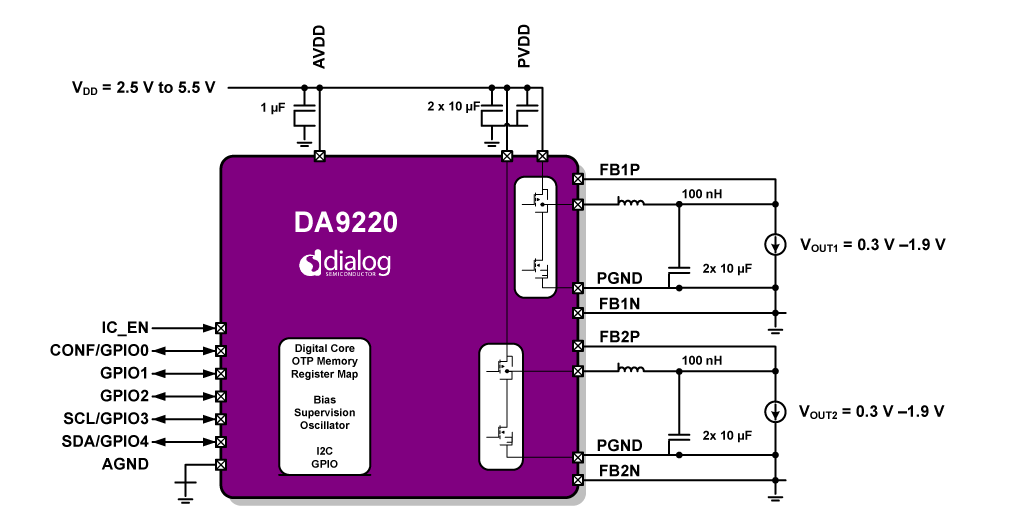

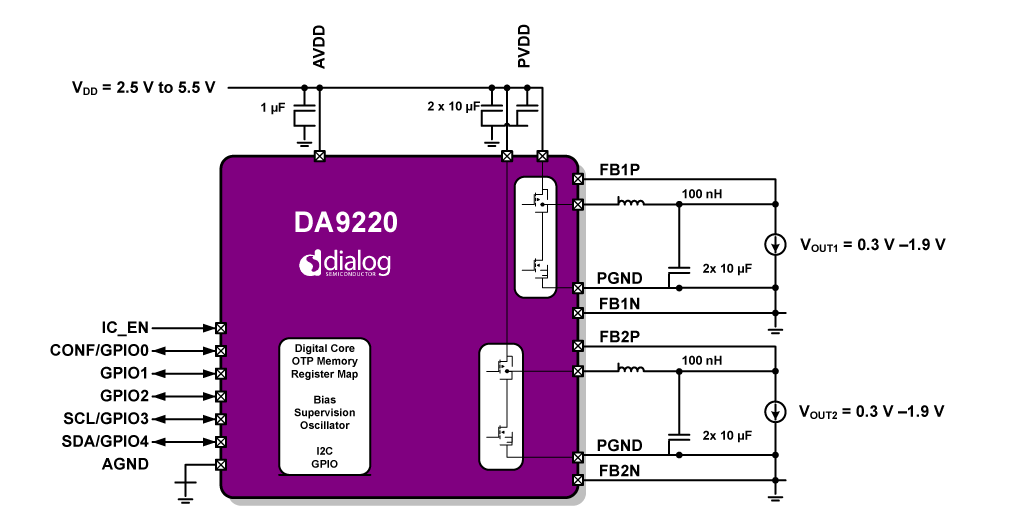

的应用。 *附件:DA9220可配置的双路输出3A + 3A Sub-PMIC数据手册.pdf 优势 输入电压范围灵活,可通过单节锂离子电池或标准 3

2025-04-08 15:55:44 694

694

DDR3x4、千兆以太网x2、HDMI接口x2(输入输出各一个)、PCIe2.0x8、SFPx2和FMC_HPC等高速接口,非常适合工业控制、图像处理、高速通信、AI等领域。

图 3 Kintex7开发板

2025-03-25 15:21:18

电子发烧友网为你提供AIPULNION(AIPULNION)FD50-18S15B3C2相关产品参数、数据手册,更有FD50-18S15B3C2的引脚图、接线图、封装手册、中文资料、英文资料,FD50-18S15B3C2真值表,FD50-18S15B3C2管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-24 18:46:29

电子发烧友网为你提供AIPULNION(AIPULNION)FD60-36S24B3R2相关产品参数、数据手册,更有FD60-36S24B3R2的引脚图、接线图、封装手册、中文资料、英文资料,FD60-36S24B3R2真值表,FD60-36S24B3R2管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-21 18:33:05

电子发烧友网为你提供AIPULNION(AIPULNION)PFD50-36S24B3R2相关产品参数、数据手册,更有PFD50-36S24B3R2的引脚图、接线图、封装手册、中文资料、英文资料,PFD50-36S24B3R2真值表,PFD50-36S24B3R2管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-21 18:31:39

电子发烧友网为你提供AIPULNION(AIPULNION)FD50-36S24B3(R)2相关产品参数、数据手册,更有FD50-36S24B3(R)2的引脚图、接线图、封装手册、中文资料、英文资料,FD50-36S24B3(R)2真值表,FD50-36S24B3(R)2管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-21 18:31:29

电子发烧友网为你提供AIPULNION(AIPULNION)FD50-18S15B3(C)2相关产品参数、数据手册,更有FD50-18S15B3(C)2的引脚图、接线图、封装手册、中文资料、英文资料,FD50-18S15B3(C)2真值表,FD50-18S15B3(C)2管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-21 18:30:00

我们已连接 VIDEO-DC-USXGMII (USXGMII FMC 子卡) (https://www.microchip.com/en-us/development-tool

2025-03-20 06:04:51

电子发烧友网为你提供AIPULNION(AIPULNION)DA60-220S15G2N3相关产品参数、数据手册,更有DA60-220S15G2N3的引脚图、接线图、封装手册、中文资料、英文资料,DA60-220S15G2N3真值表,DA60-220S15G2N3管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-18 19:02:17

电子发烧友网为你提供AIPULNION(AIPULNION)DA10-220S3V3P2D4相关产品参数、数据手册,更有DA10-220S3V3P2D4的引脚图、接线图、封装手册、中文资料、英文资料,DA10-220S3V3P2D4真值表,DA10-220S3V3P2D4管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-18 18:46:14

电子发烧友网为你提供AIPULNION(AIPULNION)DA3-220S15G2N4相关产品参数、数据手册,更有DA3-220S15G2N4的引脚图、接线图、封装手册、中文资料、英文资料,DA3-220S15G2N4真值表,DA3-220S15G2N4管脚等资料,希望可以帮助到广大的电子工程师们。

2025-03-18 18:33:06

ila_2.xcix

-a---2025/3/12 17:193437424 jesd204_0.xcix

-a---2025/3/12 17:093409671 jesd204

2025-03-12 22:21:51

USB576X 是同一系列隔离模拟输入同步采集卡,该系列采集卡提供了 16 位、8路差分模拟输入通道,采样率最高支持 2MS/s;300Vrms 的通道间 CAT II 隔离和 3300 Vrms

2025-02-21 17:12:56 968

968

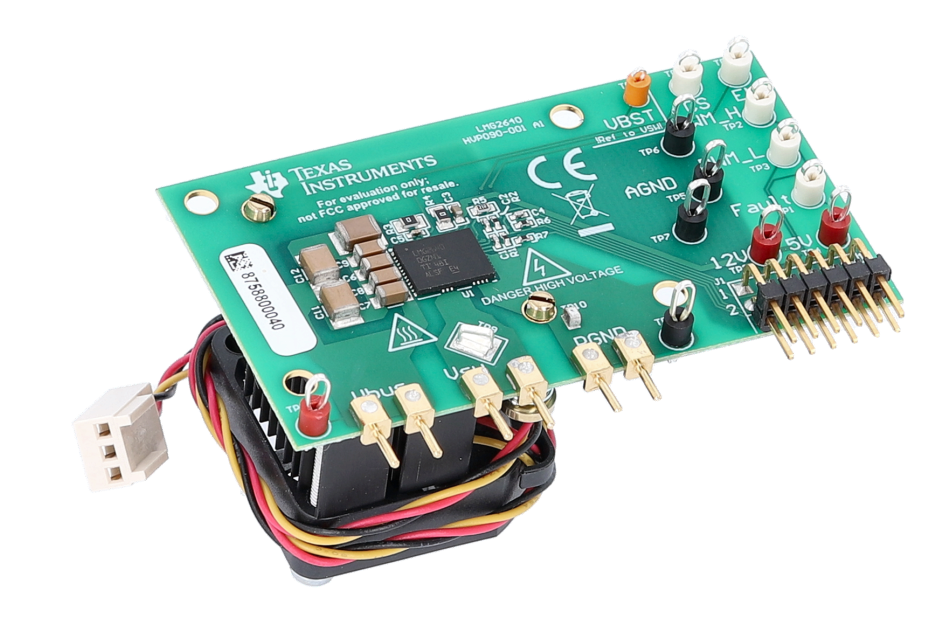

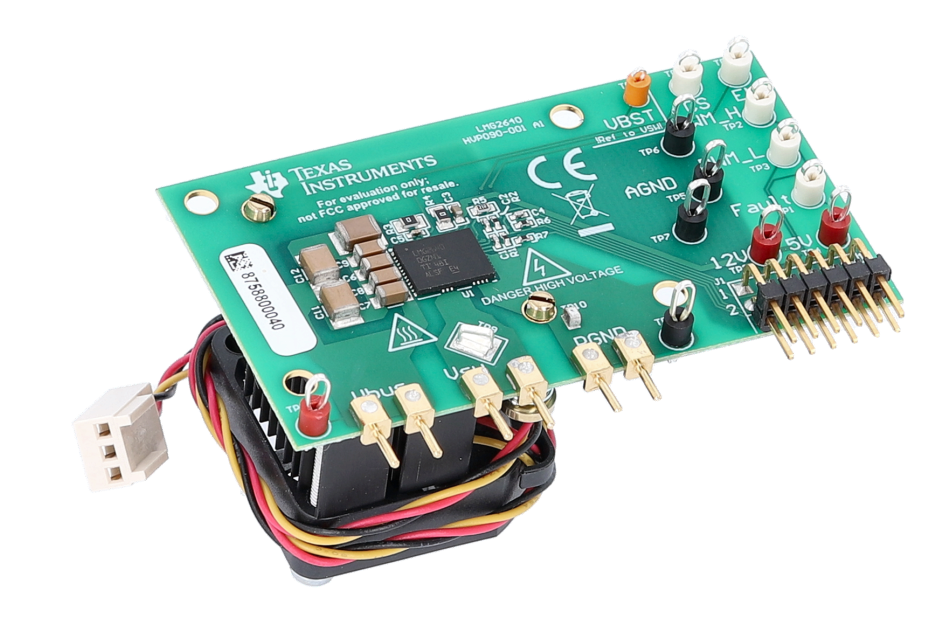

LMG2640 子卡评估模块 (EVM) 旨在提供一个快速简便的平台,以评估任何半桥拓扑中的 TI 集成 GaN 器件。该板设计为使用板底部边缘的 6 个电源引脚和 10 个数字引脚与更大的系统连接

2025-02-21 14:21:12 847

847

电子发烧友网站提供《HEF4001B-Q100四路2输入或非门规格书.pdf》资料免费下载

2025-02-20 14:13:52 0

0 电子发烧友网站提供《HEF4001B四路2输入或非门规格书.pdf》资料免费下载

2025-02-20 14:03:02 0

0 其实使用到ADI的东西,基本也就没有太去关注协议这些东西,只是简简单单的有个了解就行,在实际调试的时候,用的也是Xilinx的评估版的JESD的IP,基本不需要自己做什么工作就能够把整个系统运行起来了。

2025-02-08 13:45:55 3990

3990

请问各位大侠:JESD204B专用于ADC/DAC和FPGA或ASIC的接口吗,该接口同Rapid/PCIe的物理层Serdes接口有何区别,谢谢!

2025-02-08 09:10:29

DA2932是一款双路输出DA,我用一路输出锯齿波(iout1),一路输出rom里存储的正弦波(iout2),iout1那路的信号是正确的,但不知为何iout2那路的信号明显叠加上了iout1的信号,让我无法继续接下来的工作了

这张更容易说明问题

2025-02-06 07:50:52

SD

SPI

1

DAT2

X

2

CD/DAT3

CS

3

CMD

DI

4

VDD

VDD

5

CLK

SCLK

6

VSS

VSS

7

DAT0

DO

8

DAT1

X

图2.3 TF卡引脚定义

2025-01-20 14:38:42

SD

SPI

1

DAT2

X

2

CD/DAT3

CS

3

CMD

DI

4

VDD

VDD

5

CLK

SCLK

6

VSS

VSS

7

DAT0

DO

8

DAT1

X

图2.3 TF卡引脚定义

2025-01-20 14:24:32

大家好,近来接触JESD204B接口协议,采用SUBCLASS1方案,在系统设计上遇到诸多问题。首先SYSREF和DEVICE CLK 一般有不同的电气特性,一个可能是TTL的,另一个是CML

2025-01-10 07:25:47

最近在使用JESD204B协议,遇到一下问题。我使用的是FPGA与DAC38J84。

1:有关SYSREF时钟问题,DAC的时钟为1.2GHz, FPGA中JESD204B IP核配置为发射

2025-01-06 08:08:15

电子发烧友App

电子发烧友App

评论