HDMI接口显示使用DMT时序+TMDS编码来实现。当用FPGA控制HDMI的数据传输时,通常可以采用纯RTL实现TMDS算法或者使用专门的HDMI芯片(如ADV7513)这两种方案来完成。本文主要是介绍如何用FPGA控制ADV7513实现HDMI画面显示和音频播放。

2025-12-02 11:05:29 4543

4543

应用。

FPGA的开发是逻辑实现+约束+综合+仿真,嵌入式的开发是编码+编译+调试,如果是对数字电路设计感兴趣,可以考虑FPGA。

⭕在了解下就业机会哪个多?

✅1、嵌入式的就业机会很多,优点就是就业容易,因为

2025-11-20 07:12:55

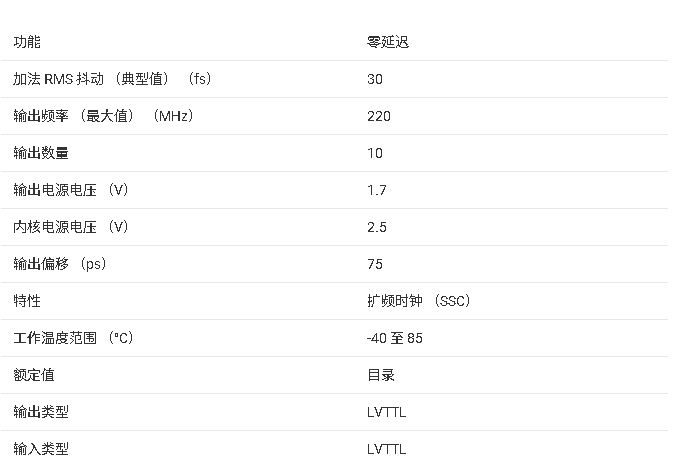

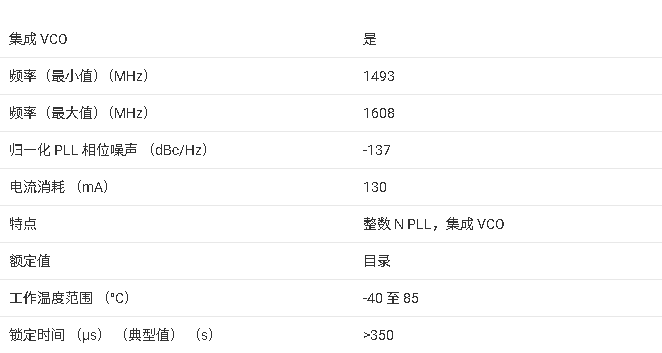

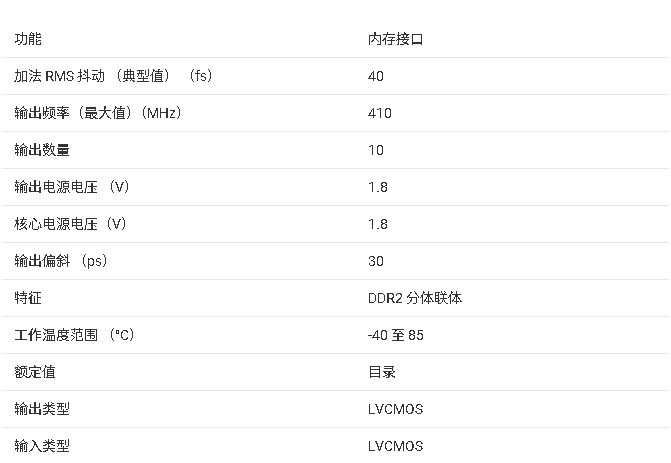

AC1571 是用于 5G 基站应用的基于 PLL的时钟发生器,该芯片采用全数字锁相环技术,以实现最佳的高频低相噪性能,并具有低功耗和高PSRR能力。典型应用场景:· 无线基站·

2025-11-11 16:43:24

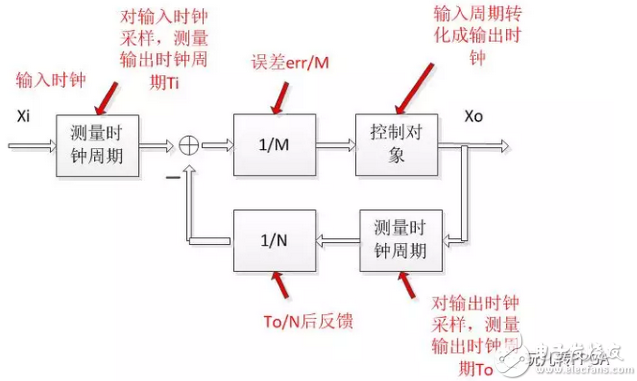

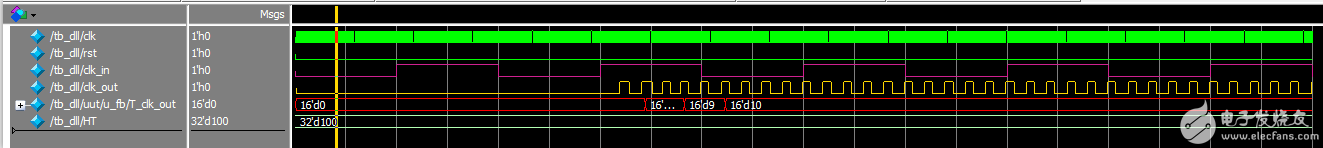

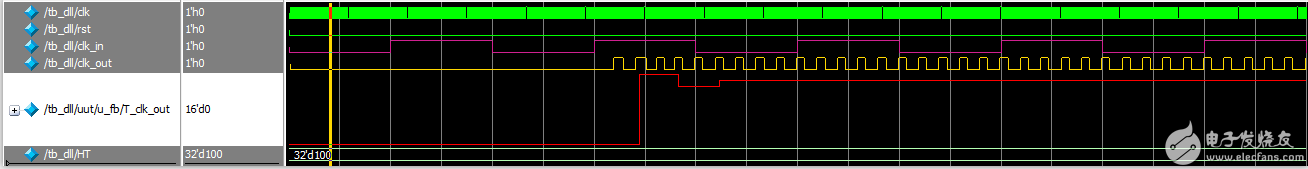

FPGA引脚中,在基于逻辑的边沿变化采集时并不能对准数据稳定的时刻,而不能正确采集到数据。为了在时钟跳变时能对准数据的稳定时刻,通常在设计时可以采用以下方法:专用IP核延迟、锁相环移相和门电路延迟。逻辑

2025-10-29 07:38:04

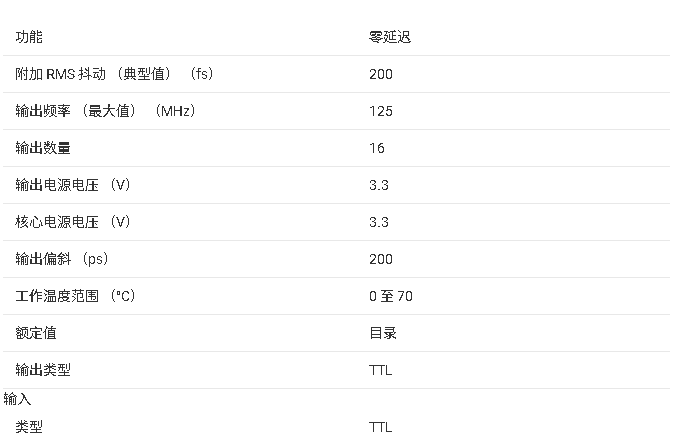

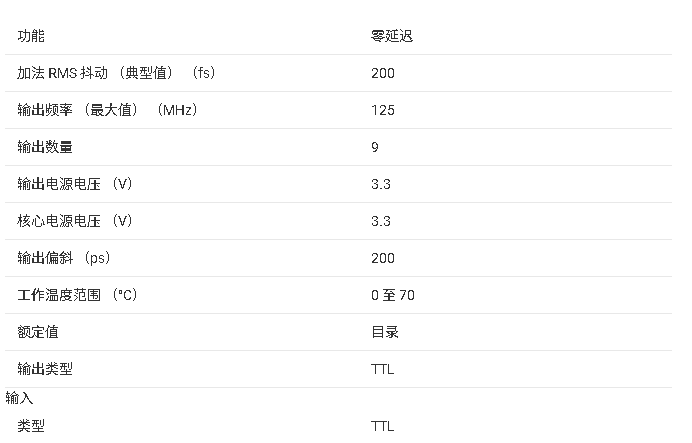

该CDCVF2510是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用锁相环 (PLL) 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对齐。它专为

2025-10-08 10:00:00 662

662

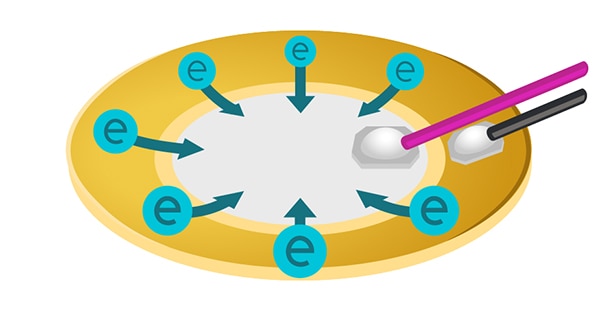

用来描述集成到设备中的力或触觉反馈机制,以增强人机互动。 从工程学的角度来看,触觉反馈通常通过机械致动器来实现。这些致动器可产生受控振动、运动或力,具体包括偏心旋转质量块 (ERM) 电机、线性谐振致动器 (LRA) 和压电元件,可模拟现实世界中的物理感觉,如压力、重

2025-10-03 17:45:00 1735

1735

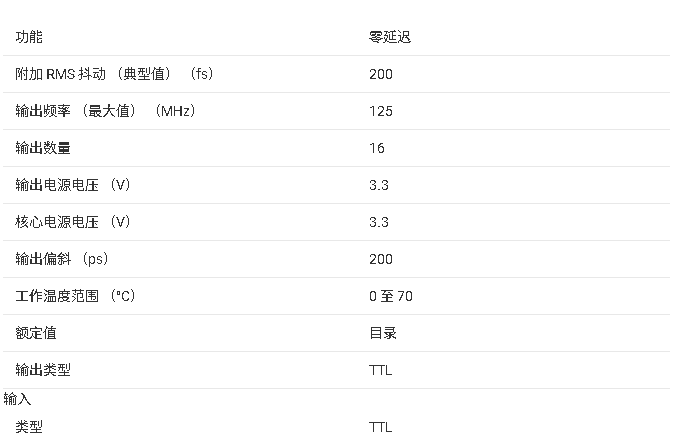

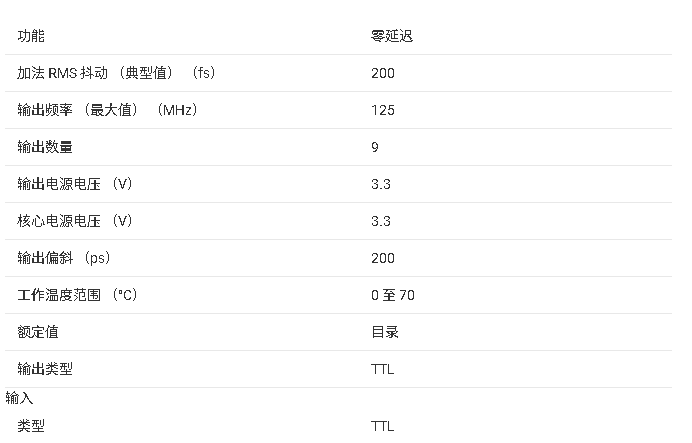

CDC2536是一款高性能、低偏斜、低抖动的时钟驱动器。它使用锁相环 (PLL) 将时钟输出信号在频率和相位上精确对齐到时钟输入 (CLKIN) 信号。它专门设计用于同步 DRAM 和流行的微处理器

2025-09-24 14:10:43 642

642

CDC536 是一款高性能、低偏斜、低抖动的时钟驱动器。它使用锁相环 (PLL) 来精确地 在频率和相位上,将时钟输出信号与时钟输入 (CLKIN) 信号对齐。具体来说 设计用于同步 DRAM

2025-09-24 10:15:48 1091

1091

CDC516 是一款高性能、低偏斜、低抖动、锁相环时钟驱动器。它使用锁相环 (PLL) 将反馈输出 (FBOUT) 与时钟 (CLK) 输入信号在频率和相位上精确对齐。它专为与同步 DRAM 一起使用而设计。CDC516 的工作电压为 3.3V V~CC~设计用于驱动每个输出多达五个时钟负载。

2025-09-23 10:15:40 761

761

CDC509 是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。它使用 PLL 在频率和相位上将反馈 (FBOUT) 输出精确对齐到时钟 (CLK) 输入信号。它专为与同步 DRAM 一起使用而设计。CDC509 的工作电压为 3.3V V~CC~设计用于驱动每个输出多达五个时钟负载。

2025-09-23 10:09:13 795

795

该CDCVF2509是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。该器件使用 PLL 将反馈 (FBOUT) 输出与时钟 (CLK) 输入信号在频率和相位上精确对齐。该器件专为与同步

2025-09-22 16:22:01 761

761

CDCVF25081是一款高性能、低偏斜、低抖动、锁相环时钟驱动器。它使用 PLL 将输出时钟在频率和相位上精确对齐输入时钟信号。输出分为 2 个组,总共 8 个缓冲 CLKIN 输出。当不存在 CLKIN 信号时,该器件会自动将输出置于低电平状态(掉电模式)。

2025-09-22 15:39:14 675

675

、FBOUT)。时钟输出由时钟输入(CLK、CLK)、反馈时钟(FBIN、FBIN)和模拟电源输入(AVDD)控制。当PWRDWN为高电平时,输出与CLK在相位和频率上切换。当PWRDWN为低电平时,所有输出

2025-09-22 09:59:19 503

503

该CDCVF2510A是一款高性能、低偏斜、低抖动、锁相环 (PLL) 时钟驱动器。该CDCVF2510A使用锁相环 (PLL) 将反馈 (FBOUT) 输出在频率和相位上精确对齐到时钟 (CLK

2025-09-22 09:21:33 359

359

该TLC2932A专为锁相环(PLL)系统而设计,由压控振荡器(VCO)和边沿触发型相位频率检测器(PFD)组成。VCO的振荡频率范围由外部偏置电阻(R ~偏见~ ).VCO在输出级有一个1/2

2025-09-19 15:09:18 724

724

该TLC2933A专为锁相环(PLL)系统设计,由压控振荡器(VCO)和边沿触发型相位频率检测器(PFD)组成。VCO的振荡频率范围由外部偏置电阻(R ~偏见~ ).VCO在输出级有一个1/2分频器

2025-09-19 14:50:41 738

738

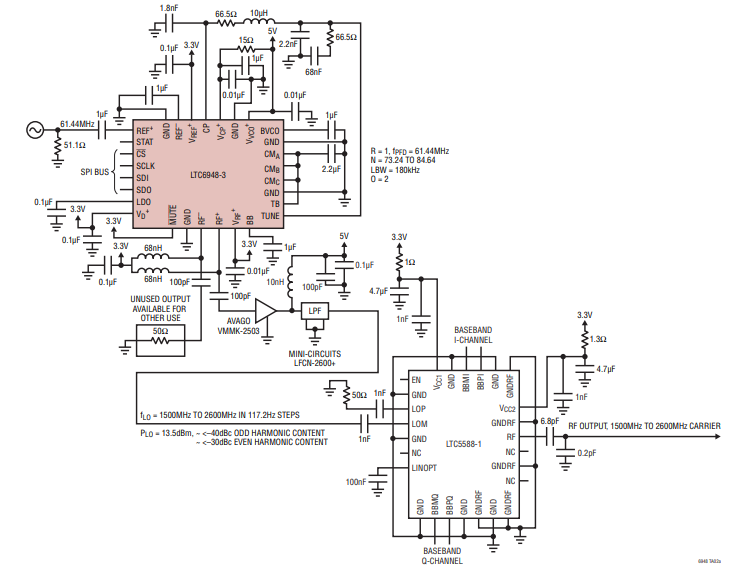

1、2 或 4 选项,以实现更灵活的输出频率 范围。它通过 3 线串行编程接口 (SPI) 接口进行控制。对于电源 敏感应用TRF3761可以通过 SPI 接口或通过外部 chip_en引脚 2。

2025-09-18 10:55:55 1455

1455

时钟(CK、CK)、反馈时钟(FBIN、FBIN)、LVCMOS控制引脚(OE、OS)和模拟电源输入(AV ~DD~ ).当OE为低电平时,除FBOUT/FBOUT外,时钟输出被禁用,而内部PLL继续

2025-09-12 09:52:57 602

602

指定的人对话的“超级耳朵”。SR860则是这个类别中的顶级产品之一。

核心定位:数字锁相放大器 (DSP Lock-in Amplifier)

SR860的核心功能是从极强的噪声中提取出极其微弱的信号

2025-09-09 10:00:00

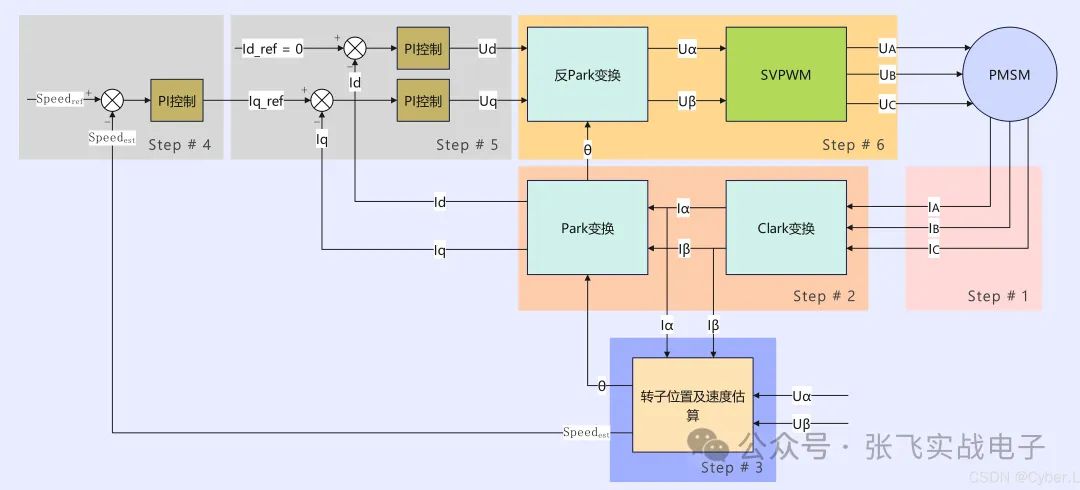

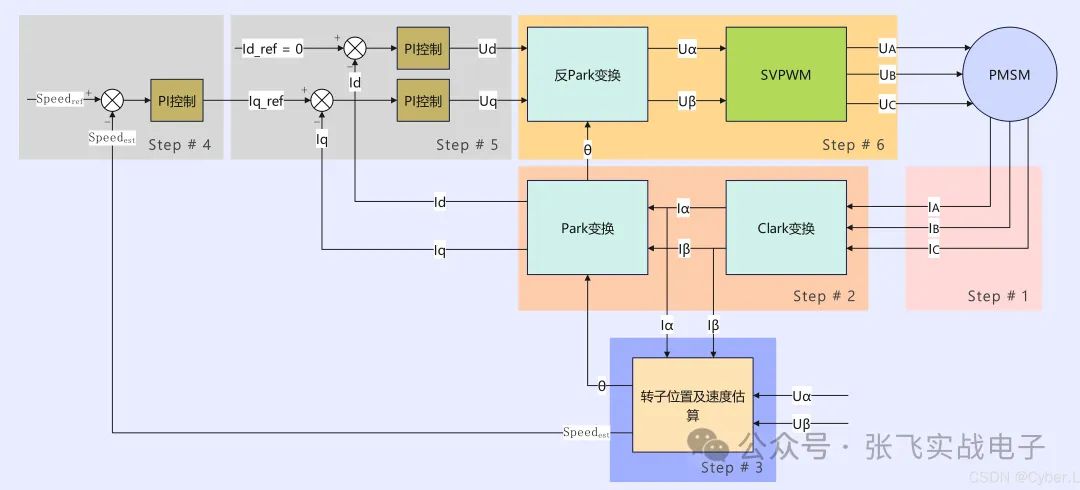

的问题,涵盖工作原理、特性、采集方法及影响因素等多方面内容。 一、电流环的工作原理与基本构成 电流环本质上是一个反馈控制系统,目标是精确控制电路中的电流。 在电机驱动系统中,电流环负责保障电机以恒定电流运转,产生稳

2025-09-03 13:39:29 611

611 在自动驾驶、电动滑板车、无人机甚至工业自动化领域,高性能电机控制是不可或缺的核心技术。而如果你对硬件有足够的热情,你会发现:传统用 MCU 实现 FOC(Field-Oriented Control,磁场定向控制)也能“搬”到 FPGA 上运行,并大大提升实时性和可扩展性。

2025-08-21 15:27:37 5012

5012

统高速并行仿真需求。

▷ 单模型分割运行: 允许单模型分割 CPU 和 FPGA 中独立运行,实现电力电子主电路、控制算法和PWM生成模块的分布式仿真,提升大规模系统测试效率。

▌易用

2025-08-20 18:31:48

Diodes 公司 (Nasdaq:DIOD) 宣布推出AP7372低噪声低压差 (LDO) 稳压器,用于为数据转换器 (ADC、DAC)、电压控制振荡器 (VCO) 和锁相环 (PLL) 等精密元器件供电。

2025-08-18 09:32:25 892

892 通过FPGA对模数转换芯片(LTC2308)的采样控制,实现一个简易的数字电压表。

2025-08-16 08:58:07 5307

5307

一直以来,传统的伺服产品选择将硬件电流环放在FPGA里,这样的硬件方案需要消耗MCU更多引脚资源用于和FPGA进行数据传输,双芯片占用板子面积,导致PCB布局布线困难;再者,使用FPGA后也会增加

2025-08-07 15:44:03 4340

4340

针对无刷直流电机传统控制的不足,在 STM32 控制框架内设计了无位置传感器电机矢量控制系统,采用基于锁相环的滑模观测器对转子位置及转速精确估计并完成电机矢量控制。给出控制系统的总体设计框架及其实现

2025-08-04 14:42:11

使用场合。为实现无轴承同步磁阻电机高速超高速、低成本、实用化运行,提出了一种基于锁相环法的无速度传感自检测技术。通过应用锁相环原理,设计出无轴承同步磁阻电机无速度传感器,并基于 Matlab

2025-07-29 16:22:56

、数字识别、HDMI显示四个主要模块,成功识别到纯底色上的一位数字,并在显示屏上的数字表中选中该数字,基本实现了本次设计的功能。

2025-07-16 14:28:38 1238

1238

硬件语言編程实现了 PI 调节模块、过零检测模块,脉冲宽度调制发生模块、换相模块、启动模块等功能,整个控制系统响应速度快、超调小,稳态误差小,可靠性高、灵活性强,实现了全数字控制,在无位置传感器直流

2025-07-10 16:35:19

: Window11 PDS2022.2-SP6.4

芯片型号: PG2L50H-484

2.实验原理

2.1. PLL 介绍

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号来控制环路内部

2025-07-10 10:28:07

SRAM、ROM等),到大量数模混合 IP(如物理层接口 PHY、锁相环 PLL 等)——这些模块经过“K 库”流程,形成预先定义好、经过参数特征化的标准模块集合,方可被数字 IC 设计流程所调用。设计师无需从零开始,直接调用这些“积木”,即可高效搭建复杂的电路系统,从而大幅提升设计效率与可靠性。

2025-07-09 10:14:12 2369

2369

,沿任一回路,所有支路电压的代数和恒等于零。

2、描述反馈电路的概念,列举他们的应用。

反馈,就是在电子系统中,把输出回路中的电量输入到输入回路中去。

反馈的类型有:电压串联负反馈、电流串联负反馈

2025-06-27 15:05:18

液压缸上的电液伺服阀。控制上与液压缸的位移传感器构成位移闭环,与力传感器构成力闭环控制:可以实现规则波和阶机波的移动控制。

纯分享帖,需要者可点击附件免费获取完整资料~~~*附件:双电机驱动数字液压阀

2025-06-19 10:59:58

品质的因素,包括电流环的动态耦合,速度环的未知扰动等。然后,在介绍扩张状态观测器的原理及功能的基础上,设计了三个扩张状态观测器分别估计速度环和电流环的总扰动,进而设计出具有扰动前馈补偿和误差反馈律相结合

2025-06-09 16:11:47

实验名称: 锁相环稳定重复频率的系统分析 实验内容: 针对重复频率的漂移,引入两套锁相环系统反馈控制两个激光器的重复频率,将其锁定在同一个稳定的时钟源上。本章主要阐述了经典锁相环的原理,稳定重复

2025-06-06 18:36:04 559

559

Analog Devices ADF4382x小数N分频锁相环 (PLL) 是一款高性能、超低抖动、小数N分频锁相环 (PLL)。它集成了压控振荡器 (VCO),是5G或数据转换器时钟应用生成

2025-06-04 11:15:21 861

861

锁相晶体振荡器(PLDRO)是一种结合了介质振荡器(DRO)和锁相环(PLL)技术的先进振荡器。它在需要高度稳定和精确的微波频率的应用中广泛使用,如卫星通信、雷达系统和测试及测量设备。PLDRO

2025-05-30 14:51:29

内容概况:

§1 反馈的概念及判断

§2 负反馈放大电路的方框图及放大倍数的估算

§3 交流负反馈对放大电路性能的影响

§4 负反馈放大电路的稳定性

§5 放大电路中反馈的其它

2025-05-29 14:41:51

有规范的,也就是可以百度到,所以高云官网的文档其实没有细说,每个FPGA厂家也是通用的。如有迷糊的大家可以在百度上补充一下相关的知识,反正不要被吓到就好。

接着我们继续看主程序的代码,这里有个锁相环

2025-05-17 20:23:37

,特别是第4章介绍负反馈电路的基本分析方法以及实现稳定放大器的负反馈设计方法。本书也给出了大量的实验数据和计算机模拟结果,尽可能使所学的知识具体化。

纯分享贴,有需要可以直接下载附件获取完整资料!

(如果内容有帮助可以关注、点赞、评论支持一下哦~)

2025-05-17 17:03:18

晶闸管)设计,并配备了先进的直接转矩控制(DTC)技术。这些技术为变频器的稳定运行和精确控制提供了坚实的基础。 二、同步切换控制原理 同步切换控制的核心在于利用锁相环(PLL)技术,使变频器输出电压的频率、幅值和相位与电网电压保持一致。这样,在

2025-05-11 16:54:35 902

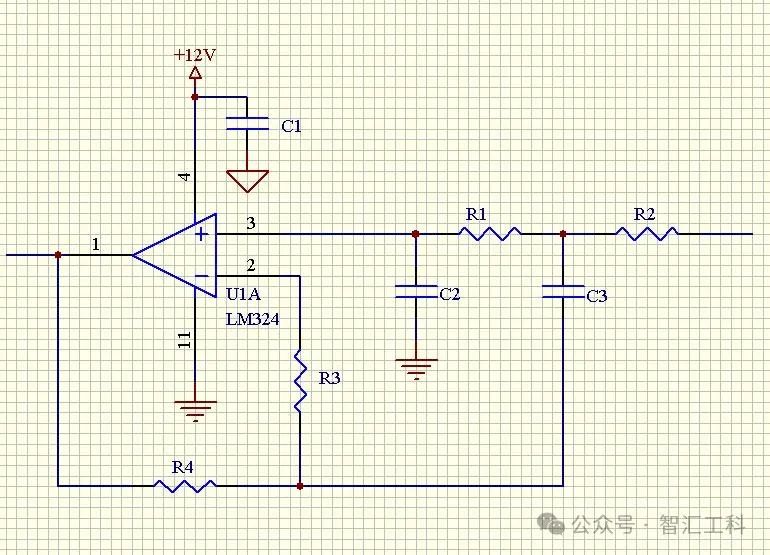

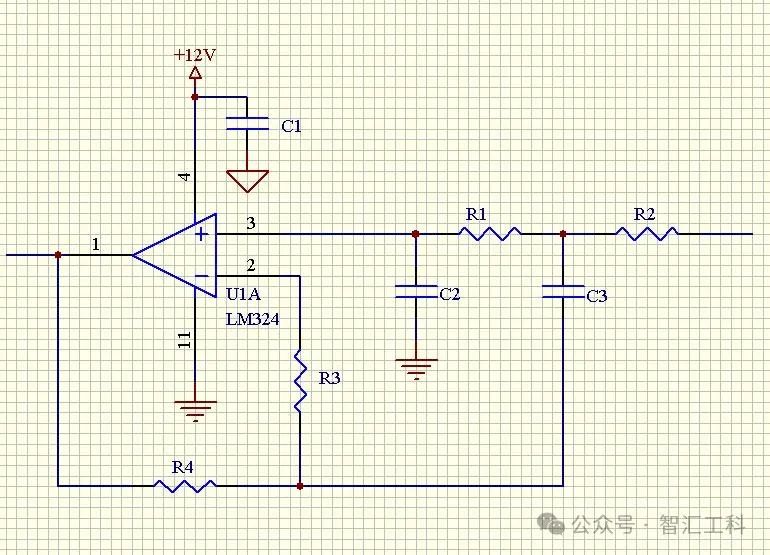

902 1. 理论讲解 本文将讲述实际环路补偿的设计步骤。 对于硬件工程师来说,开关电源和运放的信号处理电路是最常遇到的,都是典型的带负反馈的闭环控制系统。因此,这两类电路设计的稳定性和控制理论密切相关

2025-04-28 17:02:43

这是本人经典收藏的电子类书籍,有的是参加设计类大赛时翻阅的参考类文案,有的是参加培训时藏有的经典教程,在此平台上分享,希望能够帮助到有电子兴趣好爱的你,请且行且珍惜,好好收藏吧!

2025-04-25 17:05:15

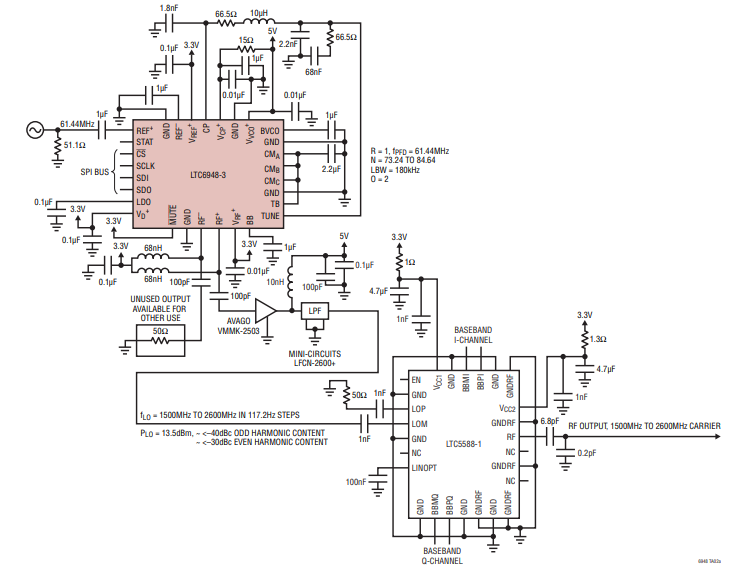

LTC6948 是一款具全集成型 VCO 的高性能、低噪声、6.39GHz 锁相环 (PLL),其包括一个基准分频器、相位-频率检测器 (PFD)、超低噪声充电泵、分数反馈分频器和 VCO 输出分频器。

2025-04-25 14:08:33 723

723

,要求实现电流——电压信号的转换时,应在放大电路中引入电压并联负反馈等。

纯分享贴,有需要可以直接下载附件获取文档!

(如果内容有帮助可以关注、点赞、评论支持一下哦~)

2025-04-25 13:29:21

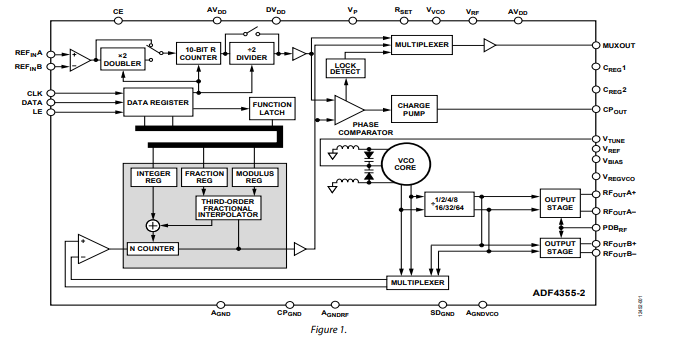

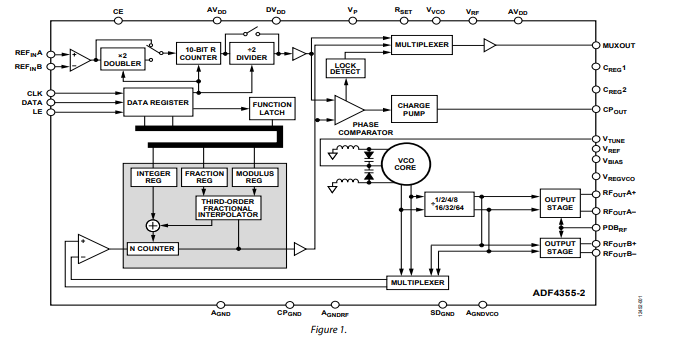

ADF4355-2结合外部环路滤波器和外部参考频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。 一系列分频器可实现54 MHz至4400 MHz的工作频率。

2025-04-25 11:42:53 914

914

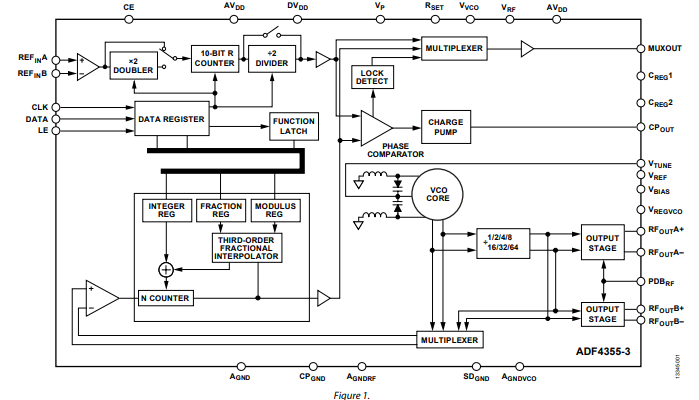

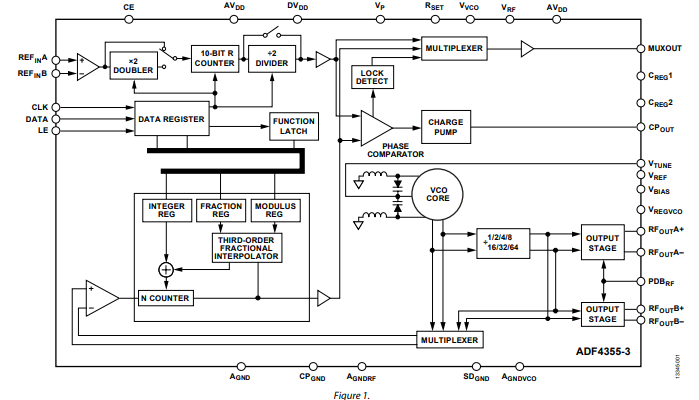

ADF4355-3结合外部环路滤波器和外部参考频率使用时,可实现小数N分频或整数N分频锁相环(PLL)频率合成器。 其他频率输出的一系列分频器可实现51.5625 MHz至6600 MHz的工作频率。

2025-04-25 11:06:46 848

848

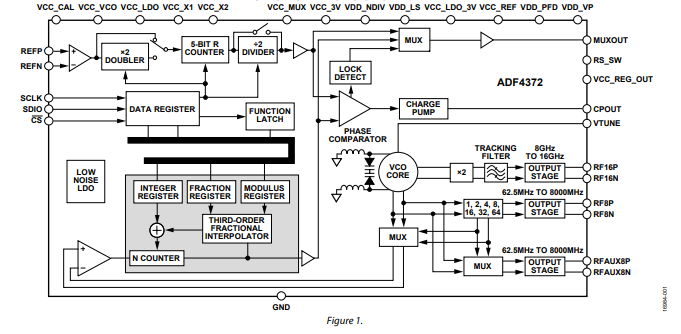

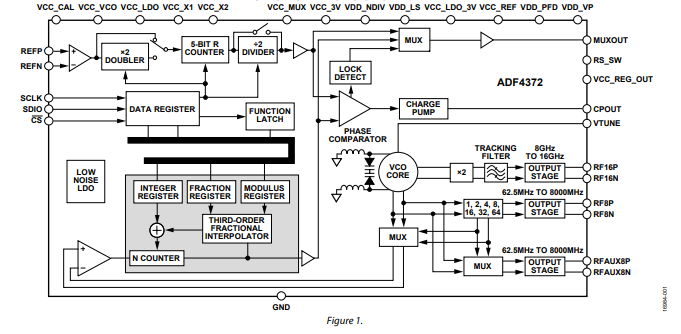

ADF4372 结合外部环路滤波器和外部基准频率使用时,可实现小数 N 分频或整数 N 分频锁相环 (PLL) 频率合成器。宽带微波压控振荡器 (VCO) 设计允许产生 62.5 MHz 至 16 GHz 的频率。

2025-04-25 09:57:01 1058

1058

摘要本题目中,振荡器采用输出波形好,频率稳定度高的具有波段切换功能的改进型电容三点式振荡电路。在每一个波段内,频率的调节是通过改变压控振荡器的变容二极管的直流反压实现的。采用锁相环频率合成电路,以

2025-04-22 14:54:08

内容介绍本文档主要介绍锁相环(PLL)电路的设计与应用,内容包括PLL工作原理与电路构成、PLL电路的传输特性、PLL电路中环路滤波器的设计方法、PLL电路的测试与评价方法、PLL特性改善技术

2025-04-18 15:34:51

问题。第三部分(第9-13章)着重介绍面向各种应用的电路设计方法,包括非线性电路、信号发生器、电压基准和稳压电源、D-A和A-D转换器以及非线性放大器和锁相环等。可用作通信类、控制类、遥测遥控、仪器仪表等相关

2025-04-16 14:34:16

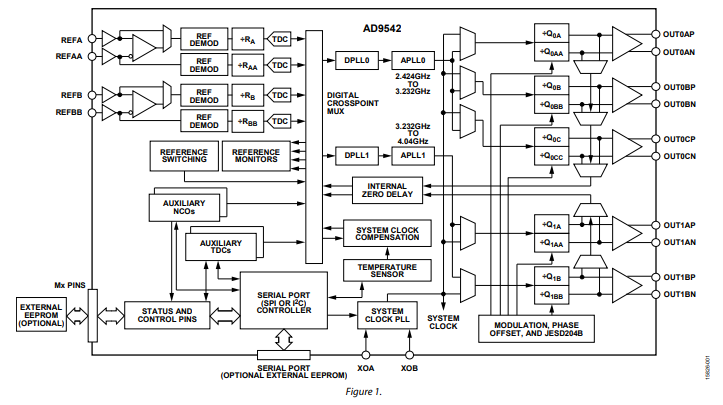

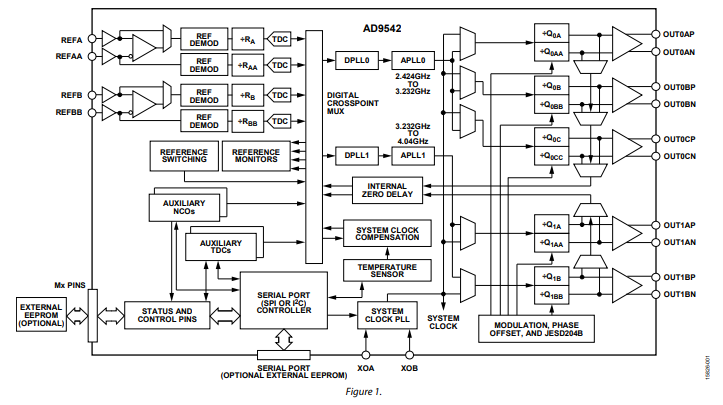

AD9542的10个时钟输出与最多四个输入基准电压源之一同步。数字锁相环(DPLL)可减少与外部基准电压源相关的时序抖动。借助数字控制环路和保持电路,即使所有参考输入都失效,也能持续产生低抖动输出信号。

2025-04-16 10:58:58 871

871

相电流检测及重构(单电阻、双电阻及三电阻采样)6.转子位置及速度提取(滑膜观测器、低通滤波器、锁相环)7.PMSM无感控制的启动计划写完上述内容后再开始写一些别的控制

2025-04-15 19:33:08 3164

3164

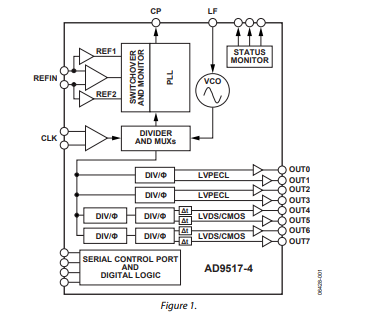

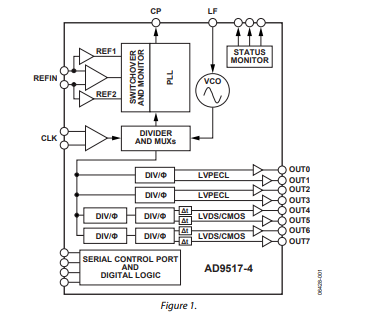

AD9517-4提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.45 GHz至1.80 GHz。也可以使用高达2.4 GHz的外部VCO/VCXO。

2025-04-14 10:10:38 953

953

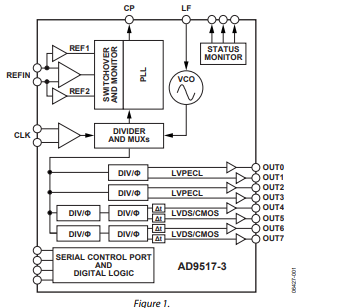

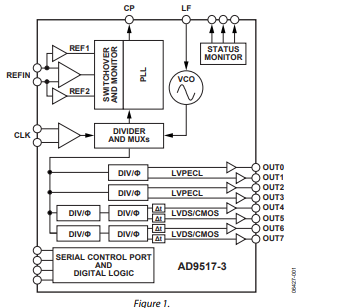

AD9517-3提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.75 GHz至2.25 GHz。也可以使用高达2.4 GHz的外部VCO/VCXO。

2025-04-14 10:04:19 922

922

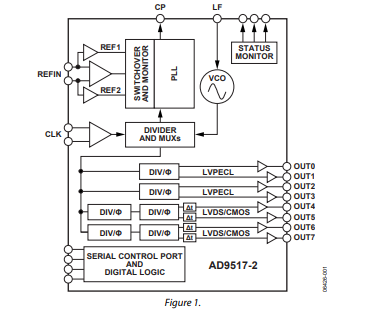

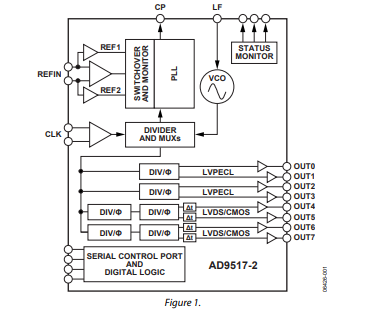

AD9517-2提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.05 GHz至2.33 GHz。也可以使用高达2.4 GHz的外部VCO/VCXO。

2025-04-14 09:53:49 848

848

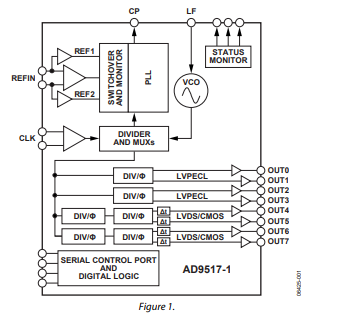

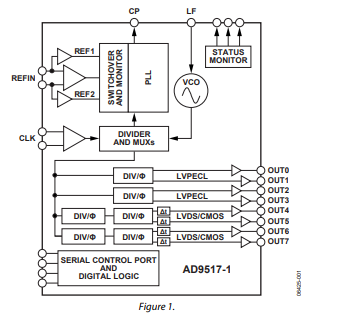

AD9517-1提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.30 GHz至2.65 GHz。也可以使用高达2.4 GHz的外部VCO/VCXO。

2025-04-14 09:41:50 852

852

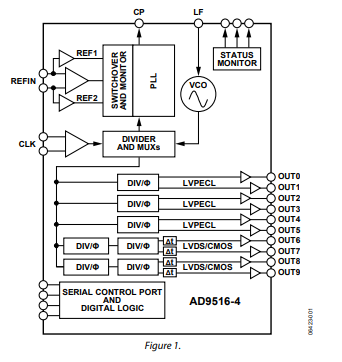

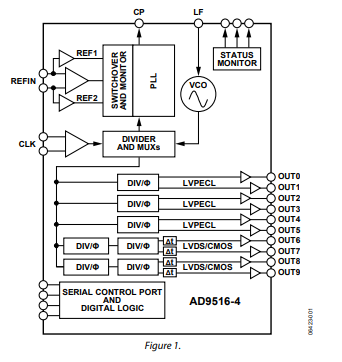

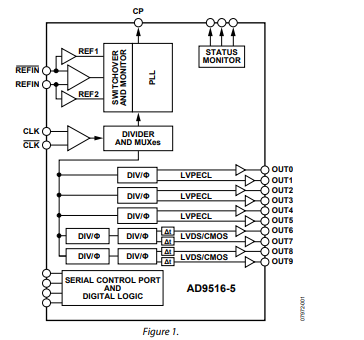

AD9516-4*提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.45 GHz至1.80 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:36:38 1017

1017

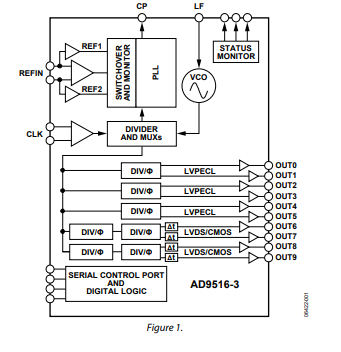

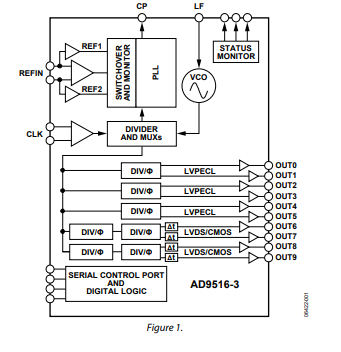

AD9516-3提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.75 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:29:24 1046

1046

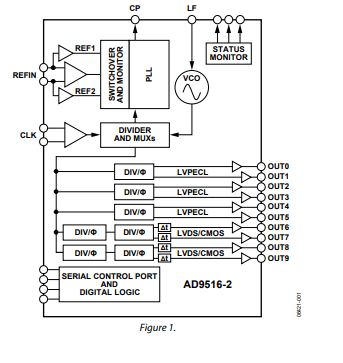

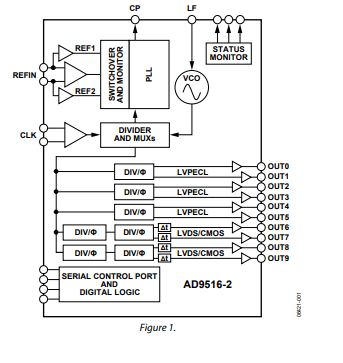

AD9516-2提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.05 GHz至2.33 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:18:10 1056

1056

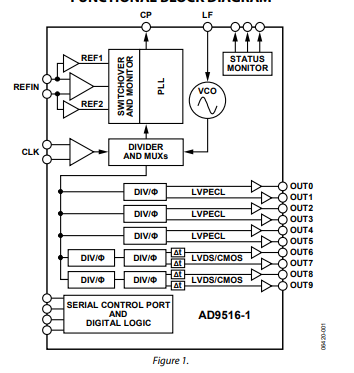

AD9516-1提供多路输出时钟分配功能,具有亚皮秒级抖动性能,还配有片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.30 GHz至2.65 GHz。或者,也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:11:24 1095

1095

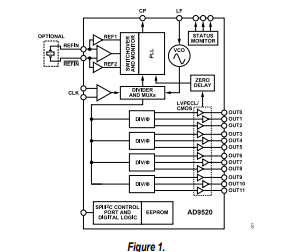

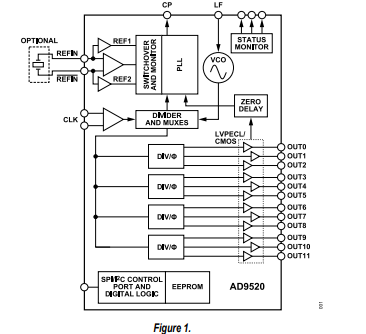

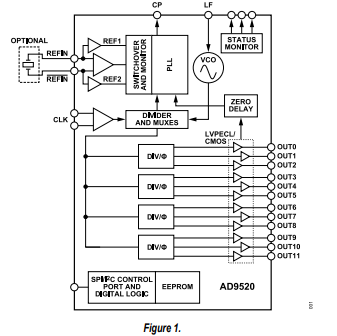

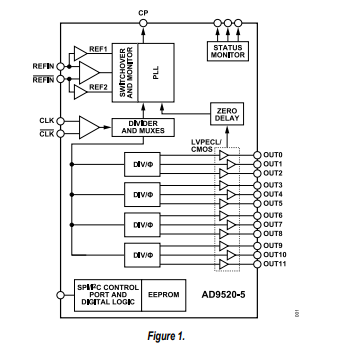

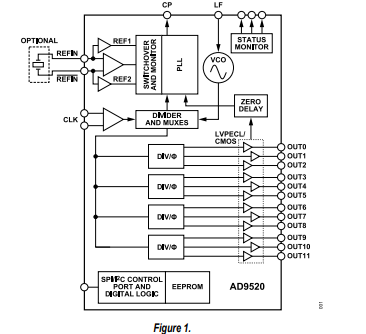

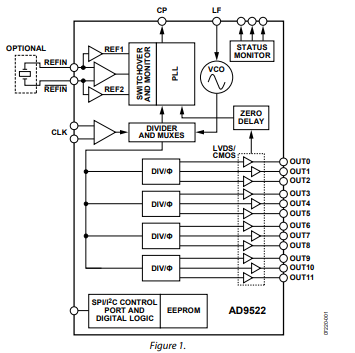

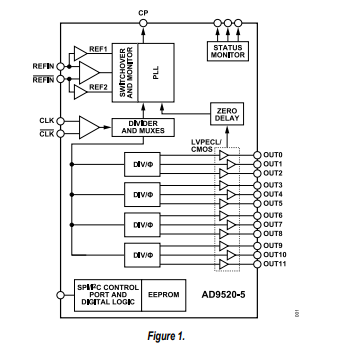

AD9520-4提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.4 GHz至1.8 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 15:38:15 688

688

AD9520-3提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.72 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 15:29:51 807

807

AD9520-2提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.02 GHz至2.335 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 14:38:24 768

768

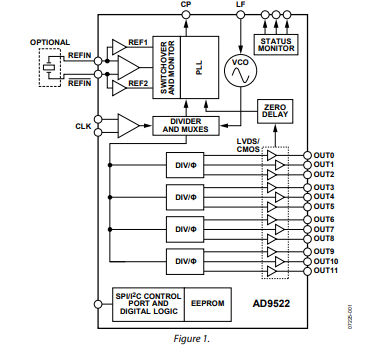

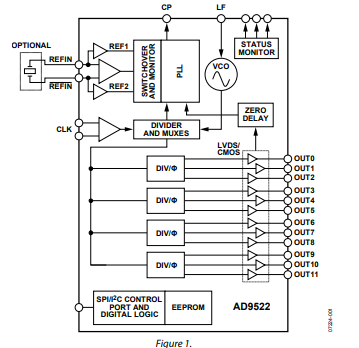

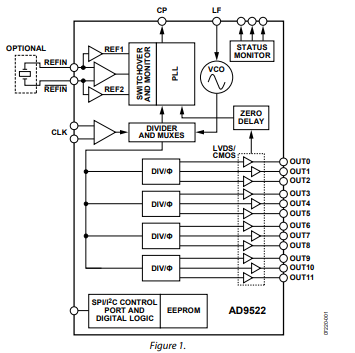

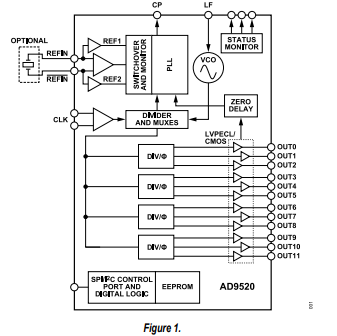

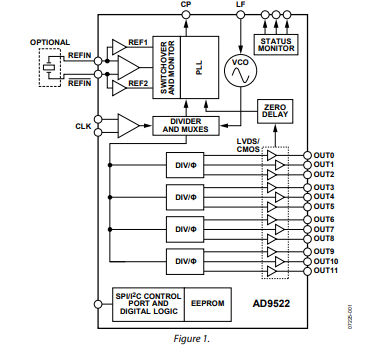

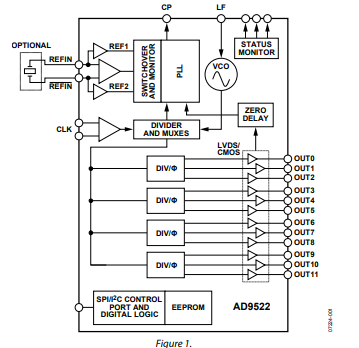

AD9522-4提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.4 GHz至1.8 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 14:14:08 822

822

AD9522-3提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.72 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 11:50:33 733

733

AD9522-1提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.27 GHz至2.65 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 11:34:42 770

770

AD9520-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO使用。

2025-04-11 11:17:07 720

720

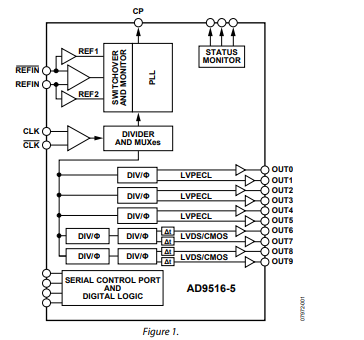

AD9516-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO/VCXO使用。

2025-04-11 11:00:50 719

719

AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考时钟之一同步。数字锁相环(PLL)可以降低与外部参考时钟

2025-04-11 09:37:58 757

757

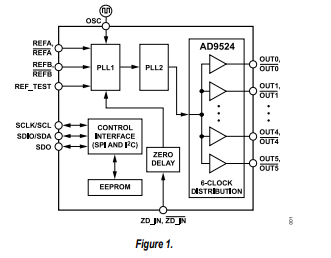

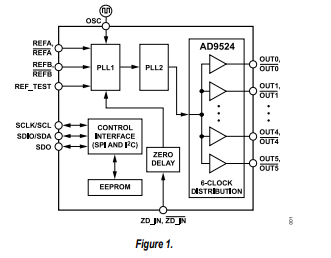

AD9524提供低功耗、多路输出时钟分配功能,具有低抖动性能,还配有片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为3.6 GHz至4.0 GHz。

2025-04-10 15:57:05 714

714

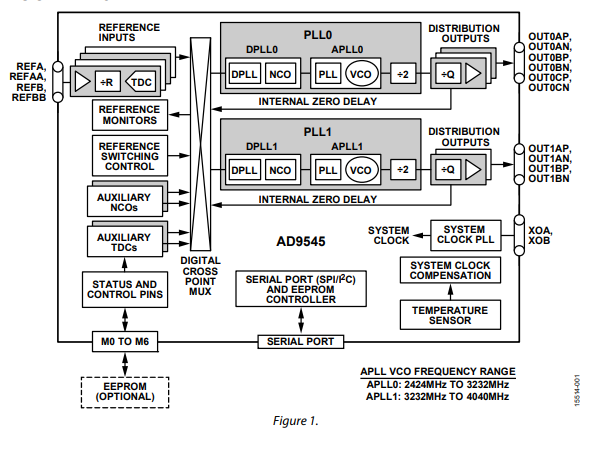

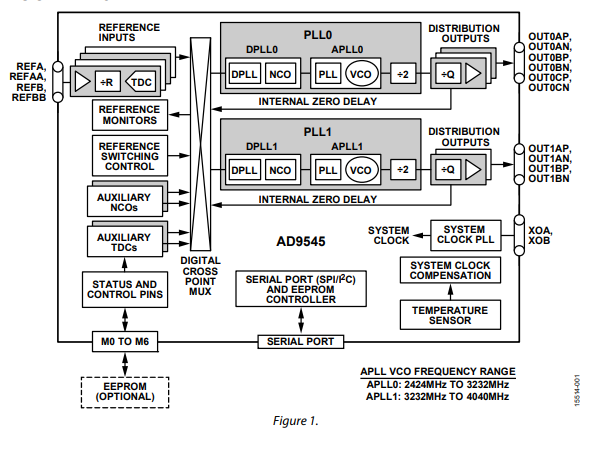

AD9545 支持针对在服务提供商包交换网络上提供频率、相位和当日时间的现有和新兴 ITU 标准。

将 AD9545 的 10 个时钟输出同步为多达四个输入基准电压源中的任意一个。数字锁相环

2025-04-09 18:04:59 1100

1100

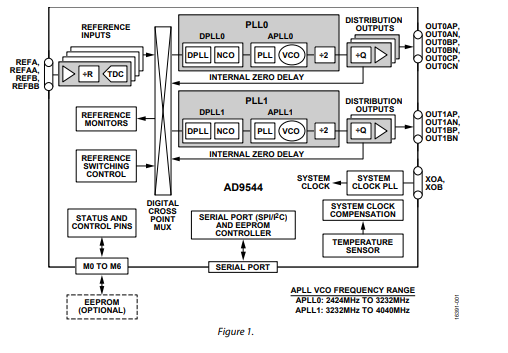

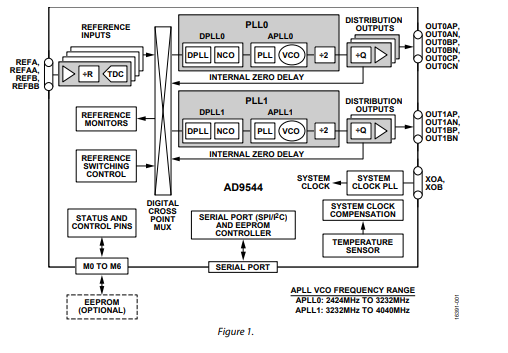

AD9544的10个时钟输出与最多四个输入基准电压源之一同步。数字锁相环(DPLL)可减少与外部基准电压源相关的时序抖动。借助数字控制环路和保持电路,即使所有参考输入都失效,也能持续产生低抖动输出信号。

2025-04-09 17:48:46 1083

1083

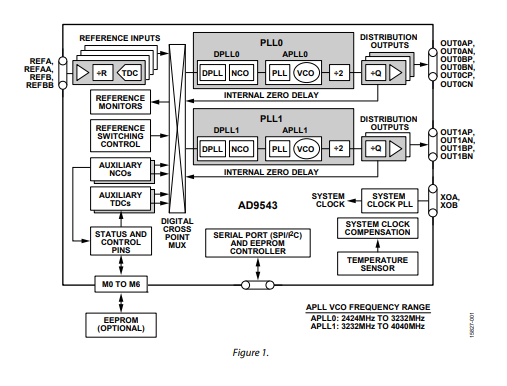

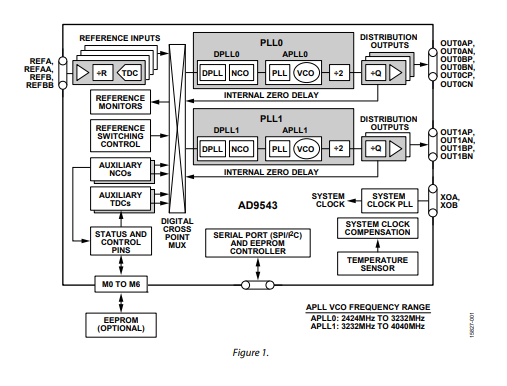

AD9543支持现有和新兴的ITU标准,可通过服务提供商分包网络传输频率、相位和当前时间。

AD9543的10个时钟输出与最多四个输入基准电压源之一同步。数字锁相环(DPLL)可减少与外部基准电压源相关的时序抖动。借助数字控制环路和保持电路,即使所有参考输入都失效,也能持续产生低抖动输出信号。

2025-04-09 17:35:04 1053

1053

~

01、数字信号处理的FPGA实现

旨在讲解前端数字信号处理算法的高效实现。首先概述了当前的FPGA技术、器件以及用于设计最先进DSP系统的工具。阐述了计算机算法的概念、理论、FIR和IIR滤波器

2025-04-07 16:41:58

CS5228替代AG7120HDMI线缆延长方案包含 TypeC双模式 DP 线缆适配器寄存器,可用于识别线缆适配器的性能。抖动清理 PLL(锁相环)能够消除输入抖动,并完全重置系统抖动容限,因此能

2025-04-02 10:54:38

反馈的概念及判断,负反馈放大电路的方框图及放大倍数的估算,交流负反馈对放大电路性能的影响,负反馈放大电路的稳定性,放大电路中反馈的其它问题

2025-04-01 10:29:41

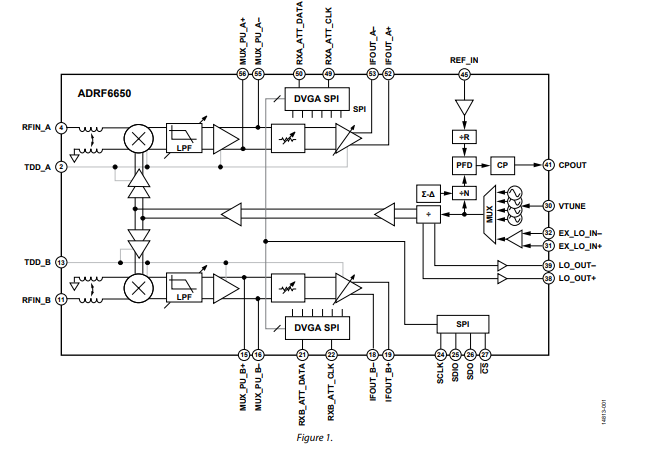

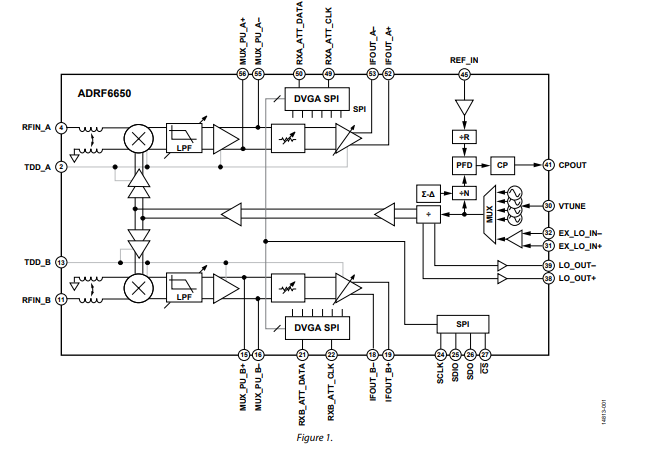

ADRF6650是一款高度集成的下变频器,集成了双混频器、双数字交换衰减器、双数字可变增益放大器、锁相环(PLL)和压控振荡器(VCO)。此外,ADRF6650还集成了两个射频(RF)巴伦、串行增益控制(SGC)控制器和快速启用输入以实现分时双工(TDD)运行。

2025-03-26 10:56:55 921

921

的单闭环调速系统可以实现无静差调速。但电机在启动过程中,为了实现最快启动,需要电流迅速达到最大值并且在一定时间内保持恒定,而主电路中存在的电感使得电流不能发生突变,因此,可以采用电流负反馈控制来实现这一

2025-03-21 17:32:55

控 制电机转速来完成的,因而调速系统是其最核心的控制 系 统 \" 。在电机的速度达到稳态的情况下,转速负反馈和PI调节器的单闭环调速系统可以实现无静差调速。但电机在启动过程中,为了实现最快

2025-03-20 13:03:04

电枢电流构成电流环。软件编程实现改进的转速、电流双闭环PI控 制器,利用单片机的定时器生成占空比可调的PWM信号,光耦隔离后经功率驱动放大,通过 控制H桥驱动电路对直流电机进行无级平滑调速。实验表明该系统控制精度高,可靠性和稳定 性加强。

全文点击下方附件查看*附件:直流电机双闭环数字调速系统设计与实现.pdf

2025-03-20 12:55:42

锁相介质振荡器(点频源)简介盛铂科技PDROUxxxx系列超低相位噪声锁相介质振荡器可实现在1GHz至44GHz范围内基于参考频率整数倍的任意固定频率高质量信号输出。PRDOUxxxx系列通过双环

2025-03-13 11:35:08

负反馈环是所有线性电源和开关电源的核心部分,它使电源的输出电压保持恒定。为了实现这一功能,采用误差放大器来减小输出电压与理想参考电压的误差。从理论上讲,采用极高增益的反相放大器就行了。但实际上

2025-03-11 14:40:08

基于不同的标准和电路特性进行分类,以下是几种主要的类型: 1. 按照反馈极性分类: ● 正反馈:输出信号增强了输入信号,导致净输入信号增加。这种反馈常用于振荡器和某些放大电路中。 ● 负反馈:输出信号削弱了输入信号,使净

2025-03-05 12:07:38 2664

2664

技术的革新潮流。 精准定位,奠定高效生产基石 磁环编码器通过内置的磁感应元件与精密的信号处理电路,能够实现对旋转轴位置的实时监测与精准反馈。无论是高速运转的机械臂,还是精密装配线上的旋转平台,磁环编码器都能

2025-02-28 08:54:34 1002

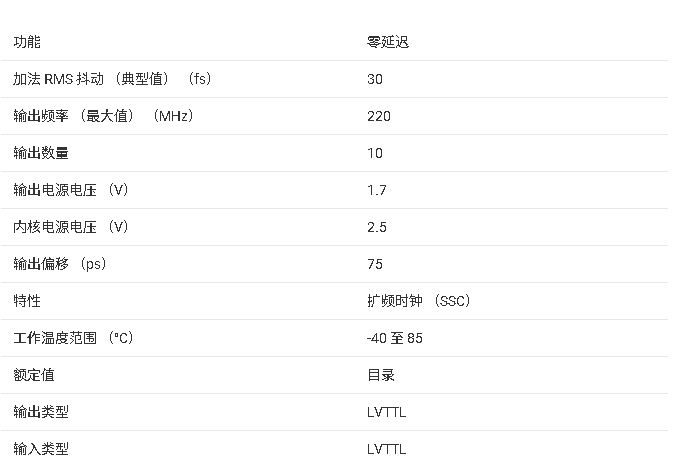

1002 路LVDS差分时钟信号。本器件片内集成锁相环模块,锁相环输入频率范围20MHz~135MHz。I/O电压支持1.8V/3.3V,core电压为1.8V/3.3V的

2025-02-17 14:03:13

1.放大电路负反馈特性总结 2.放大电路负反馈电路种类 3.放大电路对电路放大倍数及稳定性影响 4. 放大电路对电路波形及带宽影响 5. 放大电路对电路输入电阻的影响 6. 放大电路对电路输出电阻的影响

2025-02-11 10:05:19 969

969

的参考信号。测试设备:用于频率测量和信号源。深圳市立维创展科技是Synergy的经销商,主要提供Synergy微波压控振荡器、晶体振荡器、锁相振荡器、锁相环频率合成器、混频器等产品,产品位于美国北部的直接

2025-02-11 09:29:16

tlk2711发送端出来的眼图较差,tlk2711接收端的锁相环不能锁定,我们在示波器上观察恢复时钟老是调相,如何解决?

2025-02-06 07:06:50

特定的路径送回到输入端的过程。依据反馈信号对输入信号的影响,可分为正反馈和负反馈两大类型。 正反馈,顾名思义,是指反馈信号与输入信号相加后,使得输入信号得到增强。这种反馈机制能够促使电路输出迅速增大,在一些

2025-02-04 14:32:00 1719

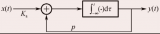

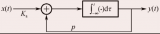

1719 锁相环(Phase-Locked Loop,简称PLL)是一种广泛应用于电子系统中的反馈控制系统,主要用于频率合成和相位同步。本文将从锁相环的工作原理、基本组成、应用案例以及设计考虑等方面进行详细阐述,以帮助读者全面理解这一重要技术。

2025-02-03 17:48:00 2317

2317 和 1.5MHz;-上行端口内置1.5K上拉电阻和下行端口内置15K下拉电阻;-片内集成5V、3.3V、1.8V电压调整器;-内置12MHz晶振启动电阻和电容;-40倍频到480MHz的PLL锁相环电路;-可以通过外置EEPROM控制VID、PID等设置;-SSOP-28无铅封装。管脚配置

功能框图

2025-01-24 12:16:06

在生物体和工程系统中,反馈调节是一种普遍存在的控制机制,它通过监测系统的状态并作出相应的调整来维持系统的稳定性或实现特定的功能。正反馈调节和负反馈调节是两种基本的反馈类型,它们在行为和效果上有着本质

2025-01-18 09:47:36 9557

9557 电子发烧友网站提供《使用独立于内核的外设实现降压转换器设计和反馈控制器.pdf》资料免费下载

2025-01-15 15:31:16 0

0 一.依据模拟环设计数字环 根据信号与系统的分析理论,一个系统完全由系统函数来确定,因此我们可从系统函数的角度出发,找到模拟电路与数字电路的转换关系,最终根据环路滤波器的数字域系统函数进行数字

2025-01-14 11:14:00 1130

1130

电子发烧友网站提供《AN-1420:利用数字锁相环(DPLL)实现相位增建和无中断切换.pdf》资料免费下载

2025-01-13 14:07:28 0

0 管理:集成数字时钟管理器 (DCM)、锁相环 (PLL) 时钟发生器和高级配置选项。 连接选项:兼容 PCI Express® 的集成端

2025-01-11 10:01:05 841

841 锁相环(Phase-LockedLoop,PLL)是一个能够比较输出与输)入相位差的反馈系统,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,使振荡信号同步至参考信号。而锁相环

2025-01-08 17:39:41 1053

1053

电子发烧友网站提供《基于锁相环法的载波提取方案.pdf》资料免费下载

2025-01-07 14:41:16 2

2 ,基于相电压采样的锁相控制比较容易受干扰,以及电网不平衡时容易影响系统稳定性,提出基于线电压采样的锁相环以及相应的并网电流正负序分离控制策略。

2025-01-06 08:47:12 1734

1734

电子发烧友App

电子发烧友App

评论