概述

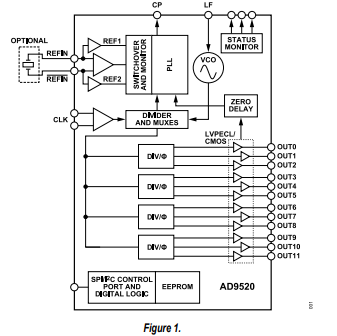

AD9520-2提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.02 GHz至2.335 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

数据表:*附件:AD9520-2 12路LVPECL 24路CMOS输出时钟发生器技术手册.pdf

AD9520-2串行接口支持SPI和I^2^C端口。封装内EEPROM能够通过串行接口进行编程,其可存储用于上电和芯片复位的用户定义寄存器设置。

AD9520-2具有12路LVPECL输出,分为四组。任何一路1.6 GHz LVPECL输出都可以重新配置为两路250 MHz CMOS输出。若应用需要LVDS驱动器而非LVPECL驱动器,请参考AD9522-2。每组3路输出具有一个分频器,其分频比(从1至32)和相位失调或粗调时间延迟均可设置。

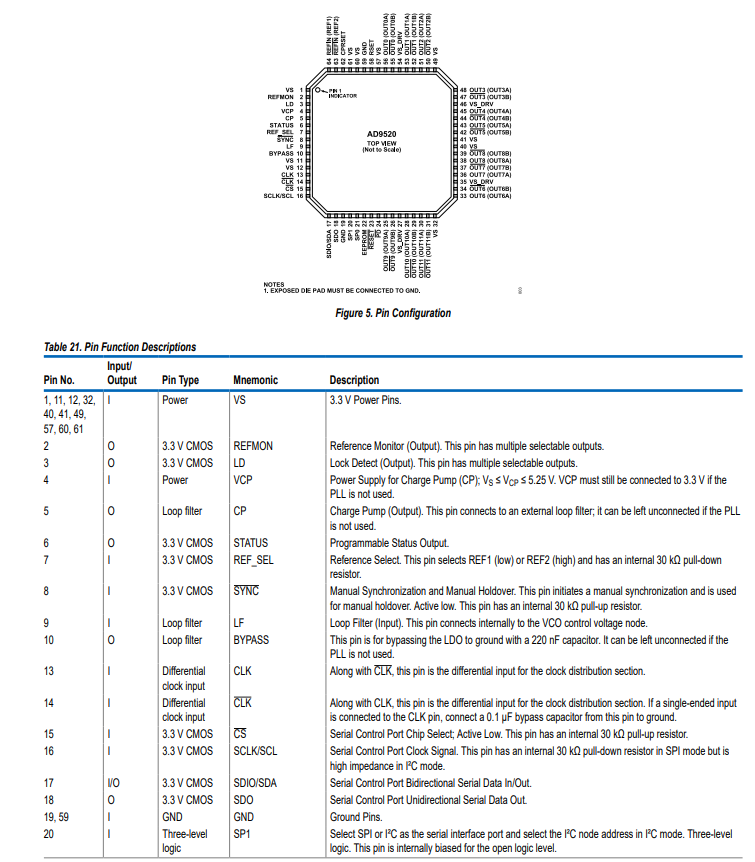

AD9520-2提供64引脚LFCSP封装,可以采用3.3 V单电源供电。外部VCO的工作电压可高达5.5 V。独立的输出驱动器电源可以为2.375 V至3.465 V。

AD9520-2的额定工作温度范围为−40°C至+85°C标准工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10GFC、同步以太网、OTU2/3/4的时钟产生和转换

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

- 宽带基础设施

特性

- 低相位噪声锁相环(PLL)

- 片内VCO的调谐频率范围为2.02 GHz至2.335 GHz

- 可选外部3.3 V/5 V VCO/VCXO至2.4 GHz

- 1路差分或2路单端基准输入

- 支持最高250 MHz的CMOS、LVDS或LVPECL参考

- 参考输入接受16.62 MHz至33.3 MHz晶振

- 可选参考时钟倍频器

- 参考监控功能

- 自动/手动参考保持和参考切换模式,恢复式切换

- 参考间无毛刺切换

- 从保持模式自动恢复

- 可选数字或模拟锁定检测

- 可选零延迟工作

- 12路1.6 GHz LVPECL输出分为4组

- 每组3路输出,共享一个带相位延迟的1至32分频器

- 加性输出抖动低至225 fs rms

- 分组输出的通道间偏斜 < 16 ps

- 可以将每路LVPECL输出配置为2路CMOS输出(f

OUT≤ 250 MHz)

- 上电时所有输出自动同步

- 提供手动输出同步

- SPI和I^2^C兼容型串行控制端口

- 64引脚LFCSP

- 非易失性EEPROM存储配置设置

框图

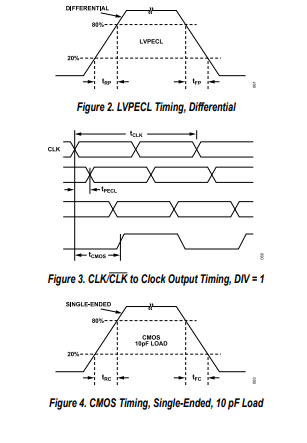

时序图

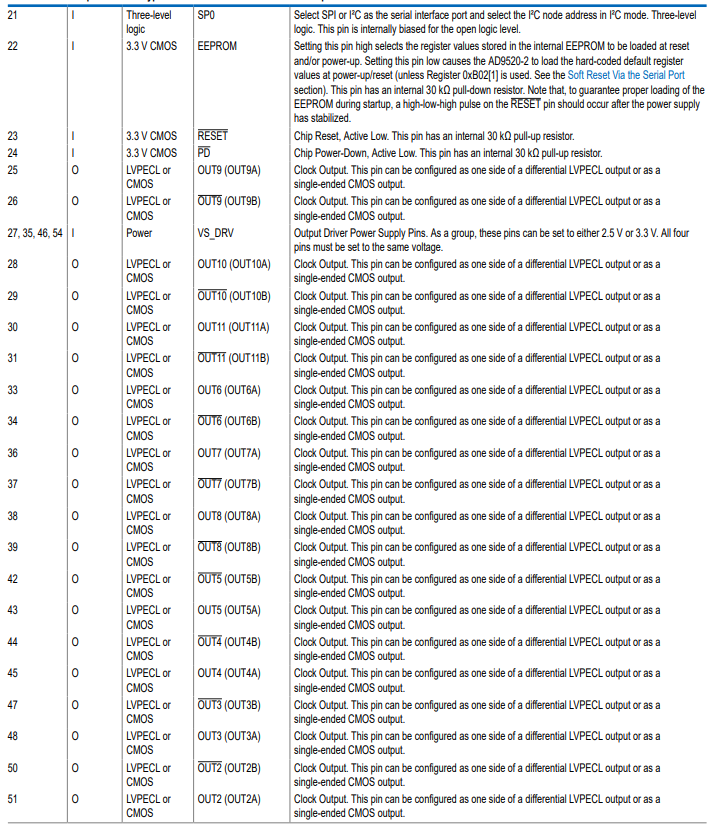

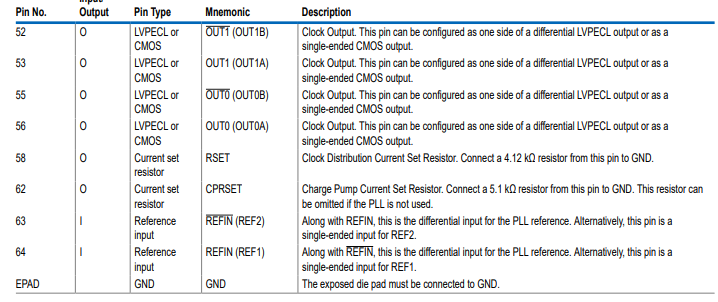

引脚配置描述

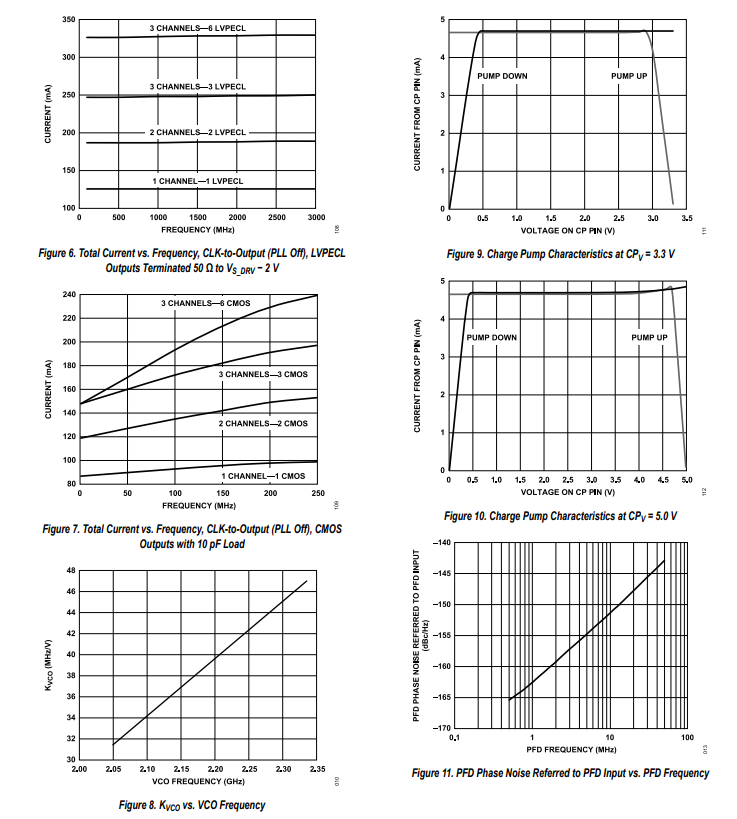

典型性能特征

这增加了驱动器所需的电压摆幅,并克服了偏移。差分参考输入可以由交流耦合LVDS或交流耦合LVPECL信号驱动。

单端输入可以由直流耦合CMOS电平信号或交流耦合正弦波或方波驱动。为避免单端交流耦合输入信号停止摆动时输入缓冲器抖动,用户可以设置寄存器0x18[7],将直流偏置点下移140 mV。为增加隔离和降低功耗,每个单端输入可以独立断电。

当选择差分参考输入时,差分参考输入接收器通电;当PLL断电时,该接收器断电。当选择单端参考输入时,单端缓冲器断电。当PLL断电或所选参考独立断电时,单端缓冲器断电。

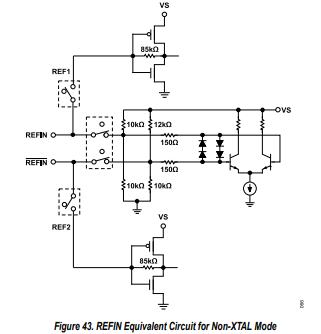

在差分模式下,参考输入引脚内部自偏置,因此它们可以接受交流耦合信号。如果差分REFIN由单端信号驱动,未使用的一侧({REFIN}})应通过合适的电容去耦到静地。图43展示了REFIN的等效电路。

晶体模式与差分模式非常相似。用户通过设置enable XTAL位,并在REFIN和**overline{text{REFIN}}**引脚之间连接一个串联谐振、基频切割晶体,来启用一个稳幅放大器。

参考切换

AD9520 - 2支持双单端CMOS输入,以及单差分参考输入。双单端参考输入(REF1引脚和REF2引脚)之间的PLL参考时钟切换,可确保参考时钟之间的相位连续性。此功能支持网络和其他应用,这些应用要求在不出现过多参考时钟瞬变的情况下切换参考时钟。与自动保持模式结合使用时,AD9520 - 2可实现最差情况下频率偏差在±10 ppm以内的参考时钟切换。

AD9520 - 2在单端模式下具有直流偏移功能。此功能旨在消除参考输入在交流耦合且参考时钟不连续时抖动的风险。使用参考切换器时,输入信号(启用AD9520 - 2的直流偏移功能时为直流耦合CMOS电平)应具有最小输入幅度。或者,输入可以交流耦合且启用直流偏移功能,但要注意直流偏移功能会增加输入幅度。

参考切换可以通过寄存器0x01C手动或自动执行,或使用REF_SEL引脚执行。要启用切换,必须通过将寄存器0x01C的第7位设置为1来禁用保持放大器。如果不满足此条件,PLL将不会切换。

自动相对切换可通过REFMON引脚启动。在编程寄存器0x01F为0x07且寄存器0x01C为0x06后,REFMON引脚被编程为在REF1有效时发出高电平信号,在REF2有效时发出低电平信号。当REF1再次有效时,REFMON引脚再次变为高电平,此部分监控锁定状态。STATUS引脚也可用于此功能,并且可以确保PLL在切换期间不会接收新选择的参考时钟的上升沿。对于与新选择的参考时钟对齐的故障切换功能,锁定到正在切换的参考时钟是必需的。可以通过禁用寄存器0x01C[7]中的直流偏移功能来禁用此功能。

不支持自动非相对切换。

参考分频器R

参考输入被路由到参考分频器R。R是一个14位计数器,可以设置为0到16,383之间的任何值(通过SPI接口写入时为0到16,382,因为有1个除法器)。R的输出除以VCO频率除以N分频器得到的PFD输入。应用的分频比必须不超过最大值(见规格),以防止PFD处出现反冲。

-

pll

+关注

关注

6文章

991浏览量

138426 -

时钟

+关注

关注

11文章

2000浏览量

135320 -

VCO

+关注

关注

14文章

321浏览量

71454 -

AD9520

+关注

关注

0文章

8浏览量

6719

发布评论请先 登录

AD9520-3BCPZ时钟发生器

AD9520-2超低噪声PLL时钟合成器评估板

AD9520-2 12路LVPECL/24路CMOS输出时钟发生器,集成2.2 GHz VCO

AD9523-1:低抖动时钟发生器,14路LVPECL/LVDS/HSTL输出或29路LVCMOS输出 数据手册

AD9520-3:12集成2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-1:12集成2.5 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-2:12集成2.2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

AD9520-4:12集成1.6 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-2 12路LVPECL/24路CMOS输出时钟发生器技术手册

AD9520-2 12路LVPECL/24路CMOS输出时钟发生器技术手册

评论