CDC2536是一款高性能、低偏斜、低抖动的时钟驱动器。它使用锁相环 (PLL) 将时钟输出信号在频率和相位上精确对齐到时钟输入 (CLKIN) 信号。它专门设计用于同步 DRAM 和流行的微处理器,在配置为半频输出的输出上以 50 MHz 至 100 MHz 或低至 25 MHz 的速度运行。该CDC2536工作电压为 3.3V VCC设计用于驱动 50 W 传输线。该CDC2536还提供片上串联阻尼电阻器,无需外部端接组件。

*附件:cdc2536.pdf

反馈 (FBIN) 输入用于将输出时钟的频率和相位与输入时钟 (CLKIN) 同步。六个输出时钟中的一个必须反馈给 FBIN,以便 PLL 保持 CLKIN 和输出之间的同步。用作反馈引脚的输出与 CLKIN 同步到相同的频率。

Y 输出可以配置为同相切换,频率与 CLKIN 相同。选择 (SEL) 输入将三个 Y 输出配置为以 CLKIN 频率的二分之一或两倍运行,具体取决于反馈到 FBIN 的引脚(见表 1 和表 2)。所有输出信号占空比都调整为50%,与输入时钟的占空比无关。

输出使能 (OE) 用于输出控制。当OE为高电平时,输出处于高阻抗状态。当 OE 为低电平时,输出处于活动状态。TEST 用于设备的工厂测试,可用于绕过 PLL。TEST 应绑在 GND 上才能正常运行。

与许多包含PLL的产品不同,CDC2536不需要外部RC网络。片内包含用于PLL的环路滤波器,可最大限度地减少元件数量、电路板空间和成本。

由于它基于PLL电路,因此CDC2536需要稳定时间才能实现反馈信号与参考信号的锁相。在 CLKIN 上电和应用固定频率、固定相位信号后,以及 PLL 基准或反馈信号发生任何变化后,需要此稳定时间。此类更改发生在更改 SEL 时,通过 TEST 启用 PLL,以及通过 OE 启用所有输出时。

该CDC2536的特点是在0°C至70°C范围内工作。

特性

- 低输出偏斜,适用于时钟分配和时钟生成应用

- 工作电压为 3.3V V

CC - 将一个时钟输入分配到六个输出

- 一个选择输入将三个输出配置为以输入频率的二分之一或两倍工作

- 无需外部 RC 网络

- 片内系列阻尼电阻器

- 外部反馈引脚 (FBIN) 用于将输出同步到时钟输入

- 同步DRAM高速微处理器的应用

- TTL 兼容输入和输出

- 输出驱动 50 条并联端接传输线

- 先进的 EPIC-II**B ™ BiCMOS 设计可显著降低功耗

- 分布式V

CC接地引脚可降低开关噪声 - 采用塑料 28 引脚收缩小外形封装

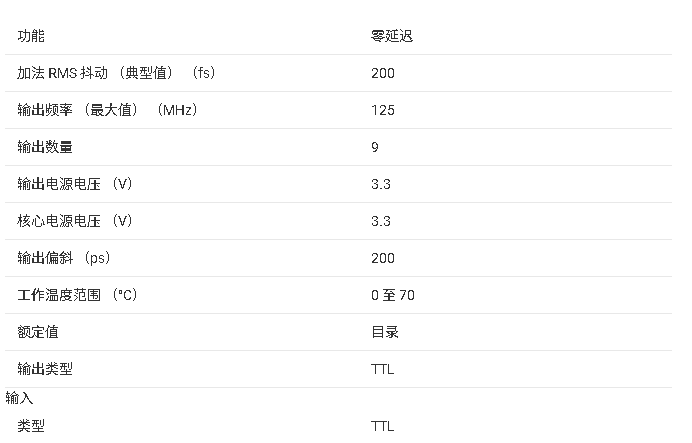

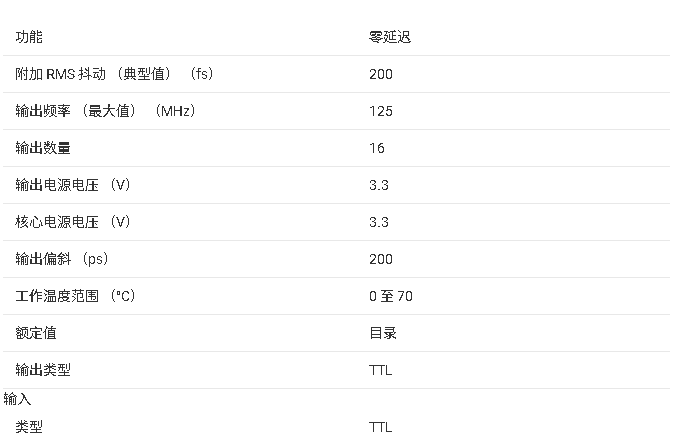

参数

1. 产品概述

CDC2536是德州仪器(TI)推出的 3.3V锁相环(PLL)时钟驱动器,具有低偏移、低抖动特性,专为同步DRAM和高速微处理器设计。核心功能包括:

- 信号分配:1路输入(CLKIN)驱动6路输出(1Y1-1Y3, 2Y1-2Y3),支持 50Ω传输线驱动。

- 频率配置:通过 SEL引脚 选择输出 1×、1/2×或2×输入频率(详见表1、表2)。

- 锁相环同步:需将任意输出反馈至 FBIN引脚 以同步频率和相位。

- 输出控制:OE引脚 使能/禁用输出(高阻态)。

- 低功耗设计:EPIC-IIB™ BiCMOS工艺,集成阻尼电阻减少外部元件。

- 封装:28引脚SSOP(DB),工作温度 0°C至70°C。

2. 关键特性

- 频率范围:

- 配置A(SEL=L):输入50-100MHz,输出1×或1/2×频率。

- 配置B(SEL=H):输入25-50MHz,输出1×或2×频率。

- 低抖动:RMS抖动≤200ps,输出偏移(tsk(o))≤0.5ns。

- 快速锁定:PLL稳定时间≤50μs(需固定频率/相位输入)。

- 集成功能:

- 片内环路滤波器,无需外部RC网络。

- 50%占空比输出(与输入占空比无关)。

3. 电气参数

| 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| **供电电压(VCC)** | - | 3.0 | 3.3 | 3.6 | V |

| **输出驱动电流(IOH/IOL)** | - | ±12 | - | - | mA |

| **输入电容(Ci)** | VI=3.3V/0V | - | 3 | - | pF |

| **功耗(ICC)** | 无负载 | - | 6 | 9 | mA |

4. 绝对最大额定值

- 电压范围:输入/输出 **-0.5V至7V ,VCC -0.5V至4.6V**。

- 功耗限制:最大 0.68W(55°C静止空气)。

- 存储温度:**-65°C至150°C**。

5. 应用设计要点

- 反馈路径:必须将任一输出连接至FBIN以实现PLL同步。

- 布局建议:

- 输入信号过渡时间≤2.5ns,避免振铃。

- 未使用的输入引脚(如TEST、CLR)需接地。

- 热管理:确保结温≤150°C。

总结:CDC2536是一款高精度时钟分配芯片,适用于需要低抖动、多频率配置的同步系统,其集成PLL和灵活的输出配置简化了电路设计。

-

锁相环

+关注

关注

36文章

637浏览量

91300 -

DRAM

+关注

关注

41文章

2402浏览量

189573 -

pll

+关注

关注

6文章

990浏览量

138378 -

输出信号

+关注

关注

0文章

311浏览量

12844 -

时钟驱动器

+关注

关注

0文章

124浏览量

14410

发布评论请先 登录

CDC2536具有三态输出的3.3锁相LO0P时钟驱动器数据表

CDC509高性能、低偏斜、低抖动、锁相环(PLL)时钟驱动器数据表

CDCVF2510 3.3V锁相环时钟驱动器技术文档总结

CDC509 3.3V相位锁定环时钟驱动器技术文档总结

CDC2536 锁相环时钟驱动器技术文档总结

CDC2536 锁相环时钟驱动器技术文档总结

评论