概述

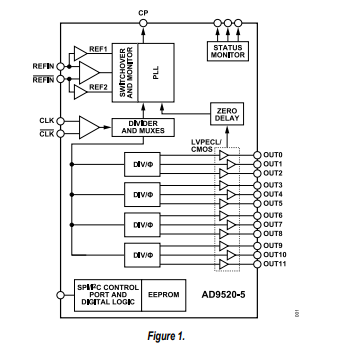

AD9520-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO使用。

数据表:*附件:AD9520-5 12 LVPECL 24 CMOS输出时钟发生器技术手册.pdf

AD9520-5串行接口支持SPI和I^2^C端口。封装内EEPROM能够通过串行接口进行编程,其可存储用于上电和芯片复位的用户定义寄存器设置。

AD9520-5具有12路LVPECL输出,分为四组。任何一路1.6 GHz LVPECL输出都可以重新配置为两路250 MHz CMOS输出。若应用需要LVDS驱动器而非LVPECL驱动器,请参考AD9522-5。每组3路输出具有一个分频器,其分频比(从1至32)和相位失调或粗调时间延迟均可设置。

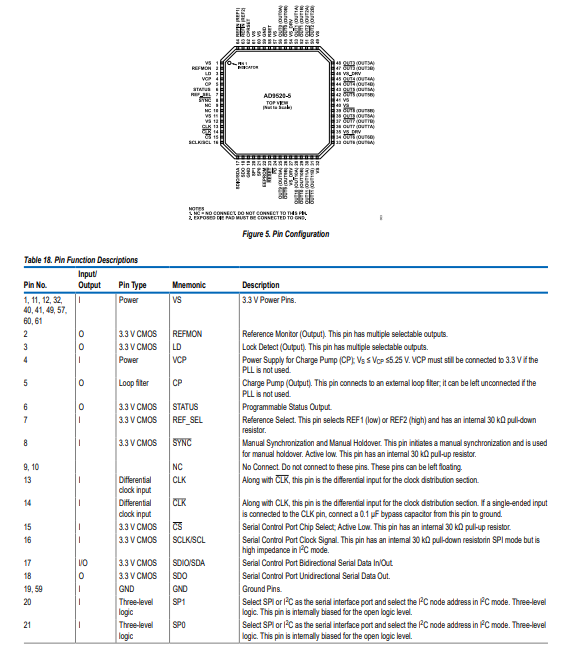

AD9520-5提供64引脚LFCSP封装,可以采用3.3 V单电源供电。外部VCO的工作电压可高达5.5 V。独立的输出驱动器电源可以为2.375 V至3.465 V。

AD9520-5的额定工作温度范围为−40°C至+85°C标准工业温度范围。

应用

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10GFC、同步以太网、OTU2/3/4的时钟产生和转换

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

- 宽带基础设施

特性

- 低相位噪声锁相环(PLL)

- 可选外部3.3 V/5 V VCO/VCXO至2.4 GHz

- 1路差分或2路单端基准输入

- 支持最高250 MHz的CMOS、LVDS或LVPECL参考

- 参考输入接受16.62 MHz至33.3 MHz晶振

- 可选参考时钟倍频器

- 参考监控功能

- 自动/手动参考保持和参考切换模式,恢复式切换

- 参考间无毛刺切换

- 从保持模式自动恢复

- 可选数字或模拟锁定检测

- 可选零延迟工作

- 12路1.6 GHz LVPECL输出分为4组

- 每组3路输出,共享一个带相位延迟的1至32分频器

- 加性输出抖动低至225 fs rms

- 分组输出的通道间偏斜 < 16 ps

- 可以将每路LVPECL输出配置为2路CMOS输出(f

OUT≤ 250 MHz)

- 上电时所有输出自动同步

- 提供手动输出同步

- SPI和I^2^C兼容型串行控制端口

- 64引脚LFCSP

- 非易失性EEPROM存储配置设置

框图

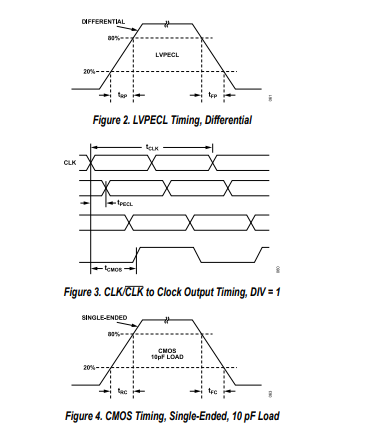

时序图

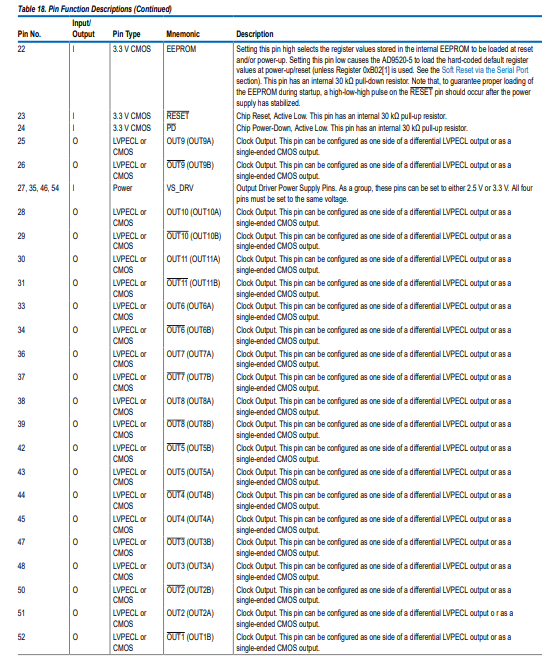

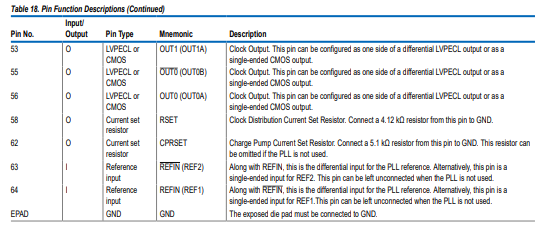

引脚配置描述

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

发生器

+关注

关注

4文章

1431浏览量

64674 -

pll

+关注

关注

6文章

990浏览量

138376 -

时钟

+关注

关注

11文章

1999浏览量

135231 -

AD9520

+关注

关注

0文章

8浏览量

6712

发布评论请先 登录

相关推荐

热点推荐

AD9520-3BCPZ时钟发生器

输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。 产品名称:时钟发生器 AD9520-3BC

发表于 07-09 11:50

超低噪声PLL时钟合成器的AD9520-5

AD9520-5 / PCBZ,用于AD9520-5的评估板是一款超低噪声PLL时钟合成器,具有集成VCO,时钟分频器和多达

发表于 04-06 15:26

具有自动hoLDOver和灵活的参考输入电路的AD9520

评估板AD9520-3 / PCBZ用于评估具有集成2GHz VCO的12 LVPECL / 24 CMOS

发表于 04-07 14:38

AD9520-5 12 LVPECL/24 CMOS输出时钟发生器

电子发烧友网为你提供(adi)AD9520-5相关数据表资料,例如:AD9520-5的引脚图、接线图、封装手册、中文资料、英文资料,AD9520-5真值表,

发表于 02-15 18:39

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO

AD9520-0:12路LVPECL/24路CMOS输出时钟

发表于 03-19 09:02

•0次下载

AD9520-3:12集成2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-3:12集成2 GHz压控振荡器数据表的LVPECL/24 CMOS

发表于 04-16 18:38

•3次下载

AD9520-1:12集成2.5 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-1:12集成2.5 GHz压控振荡器数据表的LVPECL/24 CMOS

发表于 04-18 11:48

•8次下载

AD9520-2:12集成2.2 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-2:12集成2.2 GHz压控振荡器数据表的LVPECL/24 CMOS

发表于 04-18 16:07

•6次下载

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

发表于 04-29 20:28

•11次下载

AD9520-4:12集成1.6 GHz压控振荡器数据表的LVPECL/24 CMOS输出时钟发生器

AD9520-4:12集成1.6 GHz压控振荡器数据表的LVPECL/24 CMOS

发表于 05-07 09:37

•9次下载

AD9520-1:高性能时钟发生器的全方位解析

AD9520-1:高性能时钟发生器的全方位解析 在电子电路设计领域,时钟发生器是至关重要的组件,它为系统提供稳定、精确的时钟信号,保障系统的正常运行。AD

AD9520-4:高性能时钟发生器的深度解析与应用指南

AD9520-4:高性能时钟发生器的深度解析与应用指南 引言 在电子设计领域,时钟发生器的性能对整个系统的稳定性和可靠性起着至关重要的作用。AD9520 - 4作为一款

AD9520-3:高性能时钟发生器的深度解析与应用指南

AD9520-3:高性能时钟发生器的深度解析与应用指南 在电子设计领域,时钟发生器是确保系统稳定运行的关键组件。AD9520-3作为一款12

AD9520-5 12 LVPECL/24 CMOS输出时钟发生器技术手册

AD9520-5 12 LVPECL/24 CMOS输出时钟发生器技术手册

评论