TRF3761 是高性能、高度集成的频率合成器系列, 针对高性能应用进行了优化。该TRF3761包括一个低噪声、电压控制的 振荡器 (VCO) 和整数 N PLL。

TRF3761集成了分频 1、2 或 4 选项,以实现更灵活的输出频率 范围。它通过 3 线串行编程接口 (SPI) 接口进行控制。对于电源 敏感应用TRF3761可以通过 SPI 接口或通过外部 chip_en引脚 2。

*附件:trf3761-a.pdf

特性

- 完全集成的VCO

- 低相位噪声:–137dBc/Hz(在600kHz时,f

VCO

1.9GHz) - 低本底噪声:10MHz失调时为–158dBc/Hz

- 整数-N PLL

- 输入参考频率范围:10MHz至

104MHz - VCO 频率除以 2-4 输出

- 输出缓冲器使能引脚

- 可编程电荷泵电流

- 硬件和软件断电

- 3线串行接口

- 单电源:4.5V至5.25V工作电压

参数

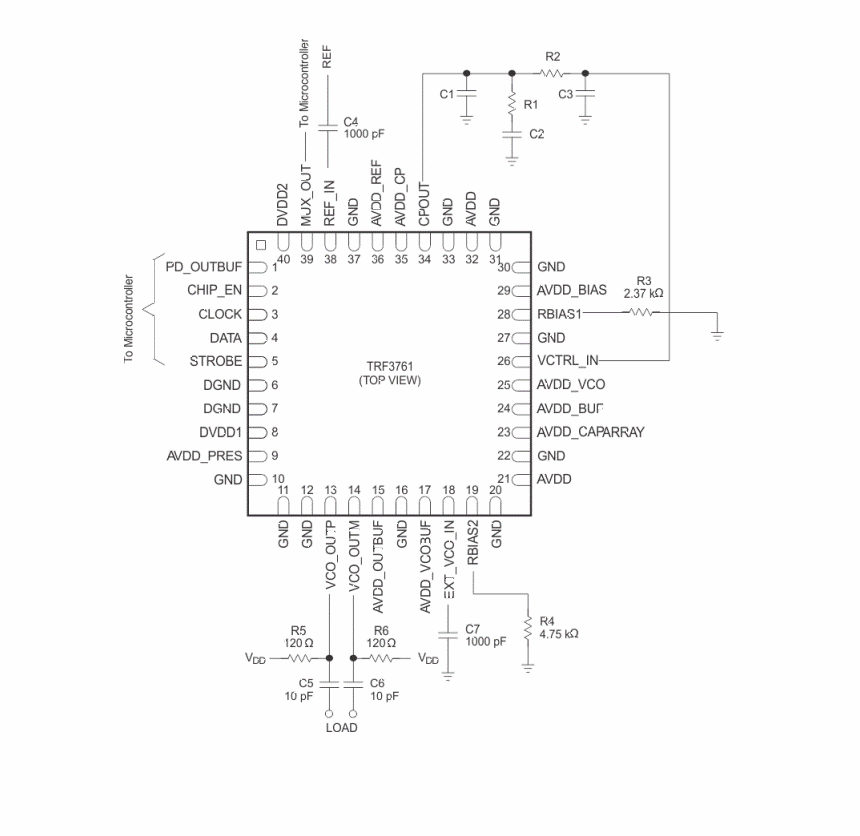

方框图

1. 产品概述

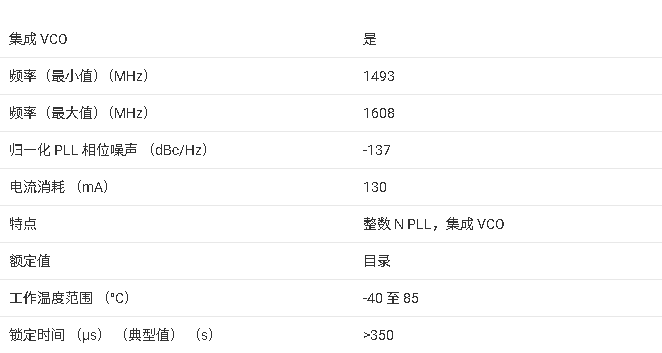

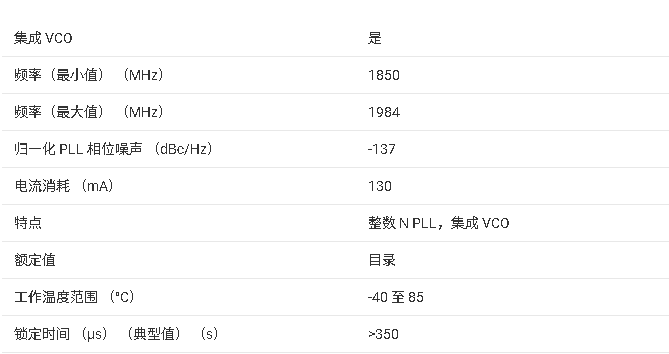

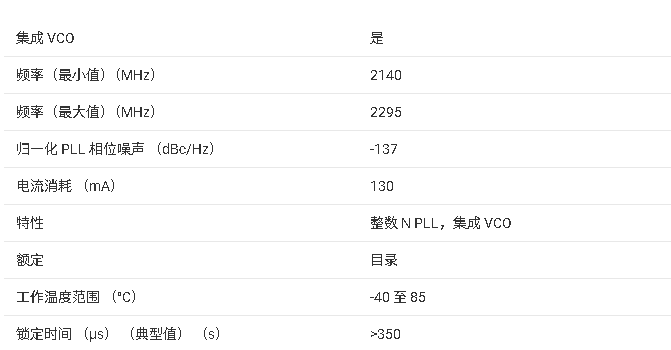

TRF3761是德州仪器(TI)推出的高性能频率合成器系列,包含TRF3761-A至TRF3761-K共11种型号,均采用40引脚VQFN封装(6mm×6mm)。核心特性包括:

- 集成VCO:支持1.49GHz至2.29GHz频率范围(具体频段因型号而异)

- 低相位噪声:典型值-137dBc/Hz @600kHz偏移(1.9GHz VCO频率)

- 整数N分频PLL:支持10MHz至104MHz参考输入频率

- 可编程输出分频:支持÷1/÷2/÷4输出模式

- 3线SPI接口:支持寄存器编程控制

2. 关键参数

- 电源电压:4.5V至5.25V单电源供电

- 相位噪声性能:典型值-158dBc/Hz @10MHz偏移

- 输出功率:单端0dBm,差分3dBm(典型值)

- 工作温度:-40°C至+85°C

3. 应用领域

4. 功能模块

- VCO核心:LC谐振腔设计,各型号优化不同频段

- 分频链:支持÷1/÷2/÷4可编程输出

- N分频器:包含双模预分频器(8/9至64/65)、6位A计数器(0-63)、13位B计数器(3-8191)

- 参考分频器:14位RDiv(1-16383分频比)

- 电荷泵:可编程电流(1.4mA至11.2mA)

5. 寄存器配置

- 寄存器1:控制电荷泵电流、输出分频模式、反冲脉冲宽度等

- 寄存器2:设置VCO校准频率和参考时钟

- 寄存器3:配置A/B计数器及锁相控制

6. 典型应用设计

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

振荡器

+关注

关注

28文章

4155浏览量

142310 -

频率合成器

+关注

关注

5文章

305浏览量

33412 -

pll

+关注

关注

6文章

976浏览量

137571 -

编程接口

+关注

关注

1文章

41浏览量

8231

发布评论请先 登录

相关推荐

热点推荐

锁相环知识

、压控振荡器(VCO) 四、环路滤波器(LPF) 五、固有频率ωn和阻尼系数x 的物 理意义 六、同步带和捕捉带 •第二部分:锁相环实验 •实验一、PLL参数测试 •一、压

发表于 12-21 17:35

PVA0865AF-LF锁相环

的步长。 PLL系列产品有几种不同尺寸可供选择从0.866英寸x 0.63英寸到小至0.5英寸x 0.5英寸。整数N和分数N低相位噪声紧凑的

发表于 04-03 17:00

基于adf4351锁相环相关硬件的设计资料分享

ADF4351锁相环介绍及相关硬件设计ADF4351是ADI公司推出的一款集成VCO的锁相环芯片。其输出频率范围可配置为35MHZ到4400

发表于 01-11 07:28

LabVIEW锁相环(PLL)

数据采集。通过锁相环同步多块板卡的采样时钟所需要的编程技术会根据您所使用的硬件板卡的不同而不同。对于基于PCI总线的产品(M系列数据采集卡,PCI数字化仪等),所有的同步都是通过RTSI总线上的时钟和触发线

发表于 05-31 19:58

pll锁相环倍频的原理

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快

pll锁相环的作用 pll锁相环的三种配置模式

基本PLL锁相环、整数型频率合成器和分数型频率合成器。下面将详细介绍这三种模式的作用和特点。 第一种:基本PLL锁相环 基本

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢?

锁相环(PLL)基本原理 当锁相环无法锁定时该怎么处理的呢? 锁相环(Phase Locked Loop, PLL)是一种电路系统,它可以将

锁相环PLL的工作原理 锁相环PLL应用领域

锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,它能够自动调整输出信号的相位,使其与输入信号的相位同步。这种电路在电子工程领域有着广泛的应用,特别是在频率合成、时钟恢复、调制

TRF3761系列整数分频锁相环(PLL)集成压控振荡器(VCO)技术手册总结

TRF3761 是高性能、高度集成的频率合成器系列, 针对高性能应用进行了优化。该TRF3761包括一个低噪声、电压控制的 振荡器 (VCO

TRF3761系列整数分频锁相环(PLL)集成压控振荡器(VCO)技术文档摘要

TRF3761 是高性能、高度集成的频率合成器系列, 针对高性能应用进行了优化。该TRF3761包括一个低噪声、电压控制的 振荡器 (VCO

TRF3761-F 低噪声整数N PLL频率合成器技术手册

TRF3761 是高性能、高度集成的频率合成器系列, 针对高性能应用进行了优化。该TRF3761包括一个低噪声、电压控制的 振荡器 (VCO

TRF3761系列整数分频锁相环(PLL)集成压控振荡器(VCO)技术文档总结

TRF3761 是高性能、高度集成的频率合成器系列,针对高性能应用进行了优化。该TRF3761包括一个低噪声、压控振荡器 (VCO) 和一个

TRF3761系列整数N锁相环(PLL)与集成VCO芯片技术文档总结

TRF3761系列整数N锁相环(PLL)与集成VCO芯片技术文档总结

评论