概述

AD9543支持现有和新兴的ITU标准,可通过服务提供商分包网络传输频率、相位和当前时间。

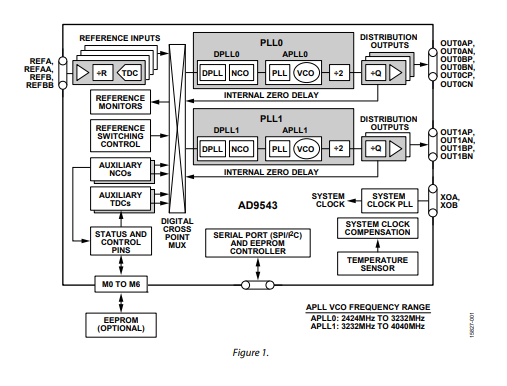

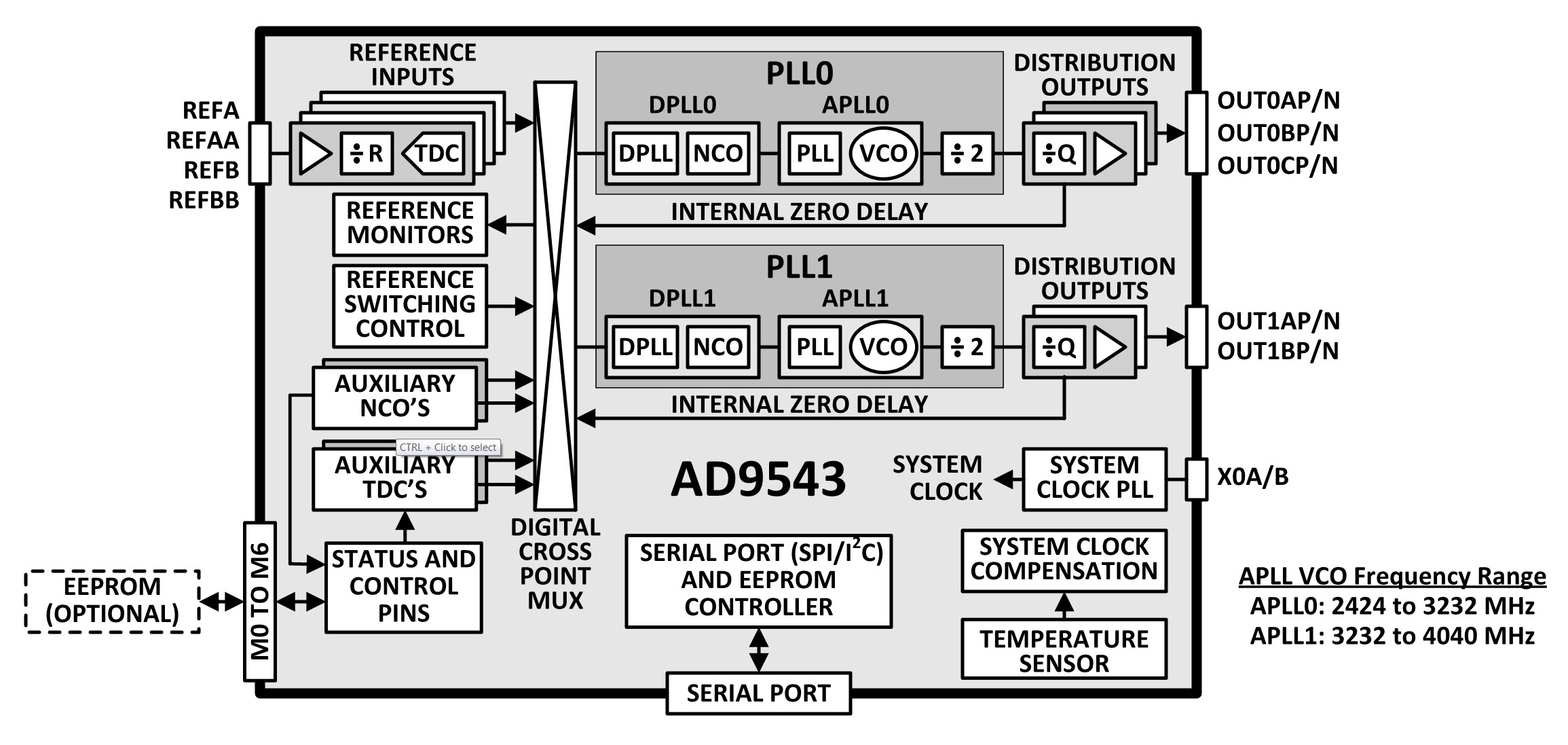

AD9543的10个时钟输出与最多四个输入基准电压源之一同步。数字锁相环(DPLL)可减少与外部基准电压源相关的时序抖动。借助数字控制环路和保持电路,即使所有参考输入都失效,也能持续产生低抖动输出信号。

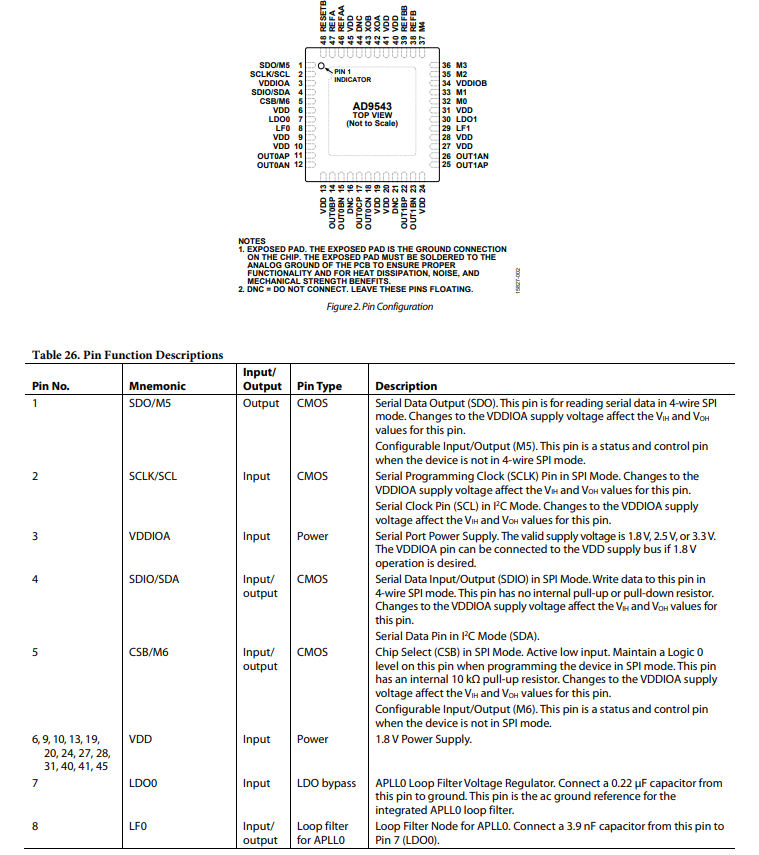

AD9543采用48引脚LFCSP (7 mm × 7 mm)封装,额定温度范围为−40°C至+85°C。

请注意,在整篇数据手册中,多功能引脚(如SDO/M5)由整个引脚名称或引脚的单个功能表示;例如M5即表示仅与此功能相关。

数据表:*附件:AD9543四通道输入、10路输出、双通道DPLL IEEE 1588同步器和抖动清除器技术手册.pdf

应用

- PTP (IEEE 1588) 和 SyncE 抖动清除和同步

- 光传输网络(OTN)、SDH、宏和小型蜂窝基站

- 具有抖动净化功能的OTN映射/解映射

- 小型基站时钟,包括基带和无线电

- Stratum 2、Stratum 3e 和 Stratum 3 保持、抖动清除及相位瞬态控制

- JESD204B 支持模数转换器 (ADC) 和数模转换器 (DAC) 时钟

- 有线基础设施

- 载波以太网

特性

- 双路DPLL可同步2 kHz至750 MHz物理层时钟,提供高噪声参考源的频率转换以及抖动净化功能

- 符合 ITU-T G.8262 和 Telcordia GR-253 标准

- 支持 Telcordia GR-1244、ITU-T G.812、G.813、G.823、G.824、G.825 和 G.8273.2

- 连续频率监控和参考验证,频率偏差低至50 ppb

- 两个DPLL具有24位小数分频器和24位可编程模数

- 可编程数字环路滤波器带宽:10^−4^ Hz 至 1850 Hz

- 两个独立的可编程辅助NCO(1 Hz至65,535 Hz,分辨率 < 1.4 × 10−12 Hz),适合IEEE 1588

- PTP 应用中的第 2 版伺服反馈

- 自动和手动保持和参考切换,提供零延迟、无中断或相位増建操作

- 基于优先级的可编程参考切换,支持手动、自动恢复和自动非恢复模式

- 5对时钟输出引脚,每对引脚均可用作差分LVDS/HCSL/CML或2路单端输出(1 Hz至500 MHz)

- 2 个差分或 4 个单端输入基准电压源

- 交叉点多路复用器将基准输入与 PLL 互连

- 支持嵌入式(调制)输入/输出时钟信号

- 快速 DPLL 锁定模式

- 提供内部功能,结合晶振或晶体振荡器的低相位噪声以及TCXO或OCXO的频率稳定性和精度

- 为自主初始化提供外部EEPROM支持

- 1.8 V 单电源供电,具有内部调节特性

- 内置温度监控器/警报和温度补偿,可增强零延迟性能

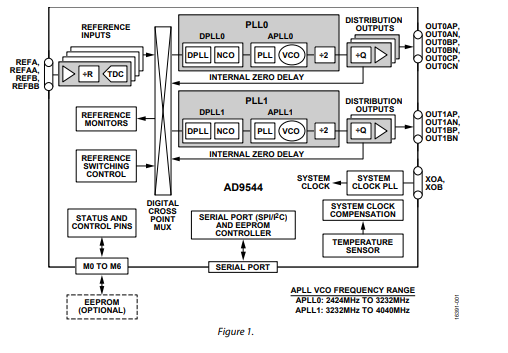

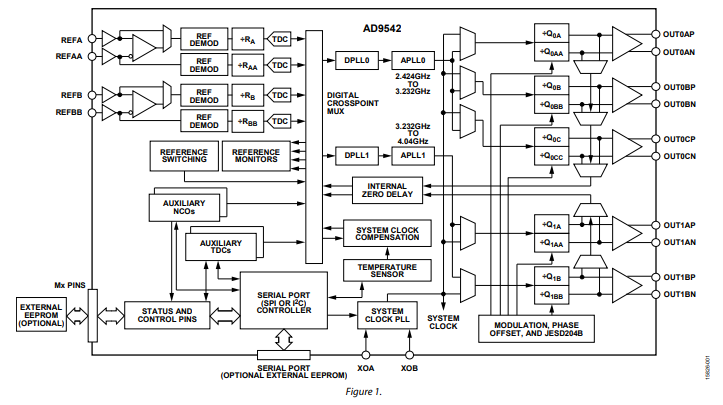

功能框图

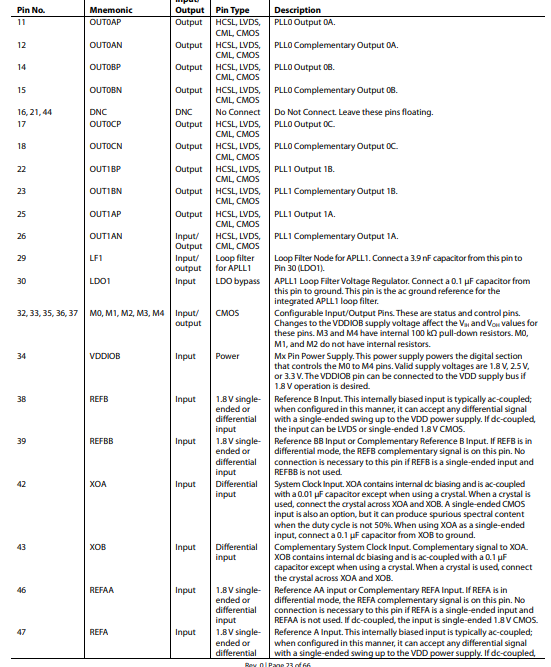

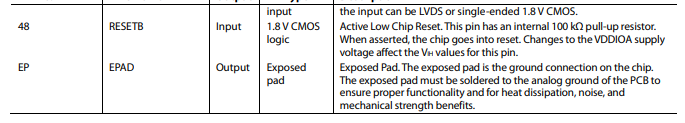

引脚配置描述

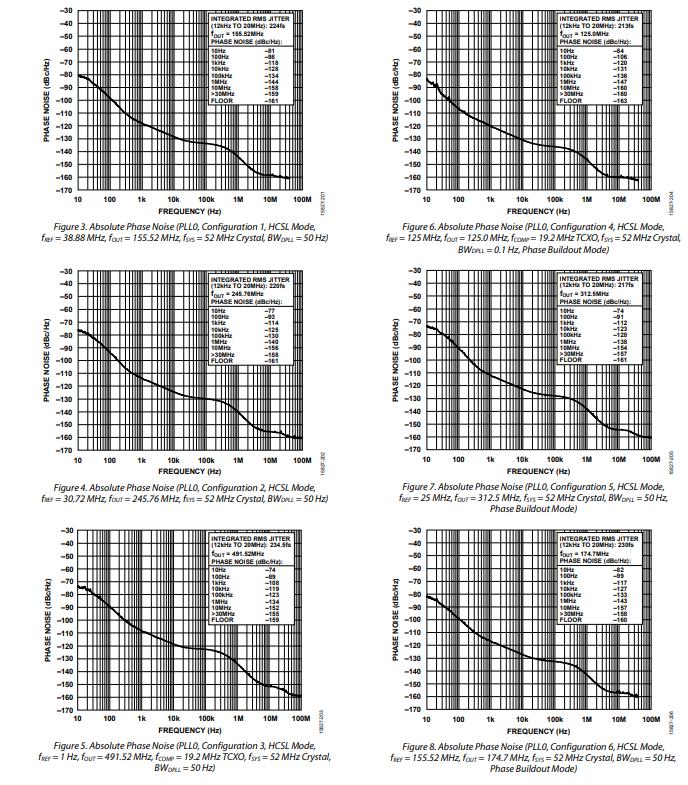

典型性能特征

应用信息

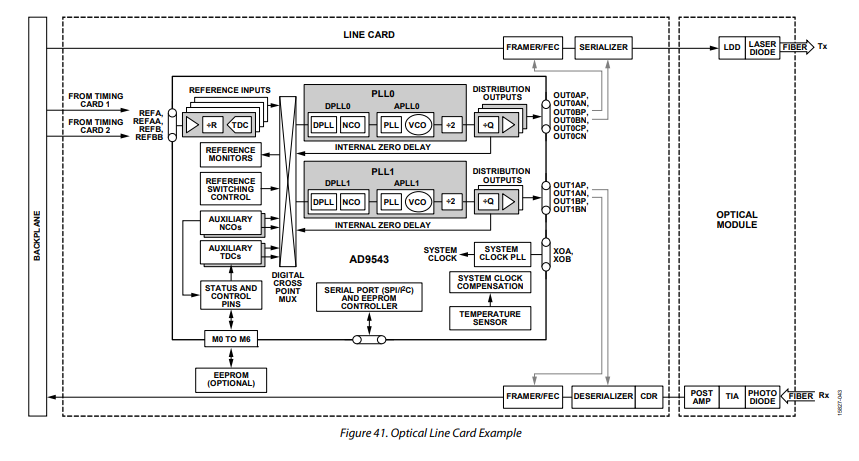

光网络线路卡

在该应用(如图41所示)中,AD9543有多种应用方式。

在环路定时(广域网)模式下,AD9543的其中一个数字锁相环(DPLL)锁定到时钟数据恢复(CDR)电路,用于去除接收路径上的抖动,并将该时钟发送至中央定时卡和成帧器。在某些应用中,AD9543还可执行多种频率转换任务,如乘以或除以前向纠错(FEC)比率,以及/或者从间隙时钟中去除抖动。另一个DPLL用于清理抖动,并为发射路径提供时钟。

其他任务包括对来自定时卡的参考时钟进行频率转换和抖动清理,以及无缝管理从定时卡1到定时卡2的参考切换。

鉴于光线路卡协议和功能不断发展,本节列出的功能绝非详尽无遗。

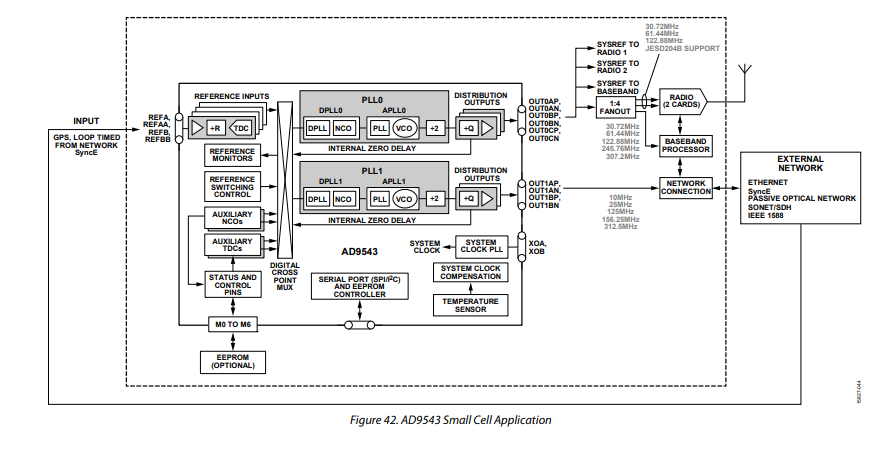

小基站

在该应用(如图42所示)中,AD9543为小基站的基带单元提供所有同步功能。其内置的JESD204B支持特性,使设计具备特别紧凑且高效的优势。

AD9543能够锁定到以下任意信号源:全球定位系统(GPS)、同步以太网(SyncE),和/或IEEE 1588(此情况需单独的IEEE 1588伺服器和软件栈),或针对SONET/SDH回传的线路定时。有关使用AD9543实现IEEE 1588版本2或版本3的详细信息,请见图43。AD9543在与IEEE 1588伺服器和软件栈配合使用时,也可按照辅助部分定时操作的定义,采用这些输入源(即SyncE、GPS)的混合组合方式运行。

AD9543的PLL0为设备时钟提供支持,并且可用于为多达四个系统参考时钟提供信号,这些时钟可用于为无线收发器(如AD9371)提供时钟。

AD9543的PLL1为回传接口提供时钟,还可根据需要选择为CPU接口提供时钟。

AD9543的电可擦可编程只读存储器(EEPROM)支持功能,使AD9543在加电时能够自动加载其配置。

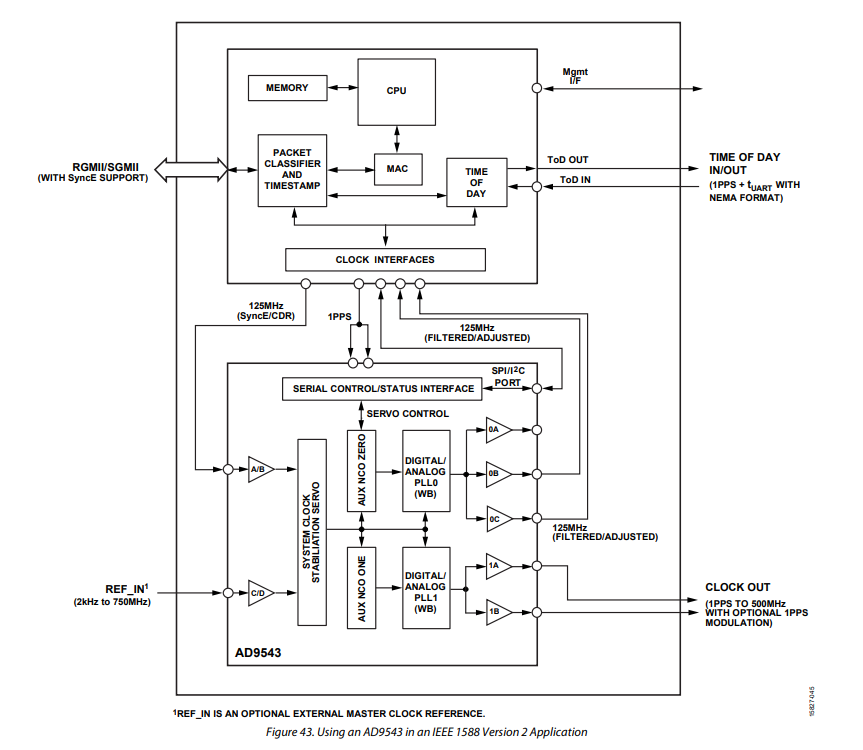

IEEE 1588伺服器

在该应用(如图43所示)中,AD9543为电信大楼通信(T - BC)中的IEEE 1588伺服器和软件栈提供所有的抖动消除、相移和同步功能,支持混合应用。该系统还可充当IEEE 1588主时钟和从时钟。

AD9543的PLL0提供经过滤波的125 MHz同步以太网(SyncE)时钟。

AD9543的PLL1提供1脉冲每秒(1 pps)至500 MHz的输出时钟,具备高分辨率输出相位调整和转换速率限制功能。例如,这使得GPS信号能够在适当的精确时间协议(PTP)软件支持下进行滤波和校正,从而提供PTP不对称校正。

AD9543的性能和特性使其成为实现最新IEEE 1588功能,以及4G和5G无线通信中最新国际电信联盟 - 电信标准化部门(ITU - T)数据包同步相关标准的理想选择。

-

数字控制

+关注

关注

2文章

200浏览量

26923 -

DPLL

+关注

关注

1文章

35浏览量

14391 -

清除器

+关注

关注

0文章

56浏览量

6112 -

同步器

+关注

关注

1文章

117浏览量

15696

发布评论请先 登录

可实现四通道模拟输入和双通道模拟输出的参考设计

TLK3134 具有集成时钟抖动清除器的高灵活性四通道Ser

美高森美IEEE1588平台新增超低抖动网络同步器产品

AD9543 四通道输入、10路输出、双通道DPLL/IEEE 1588同步器和抖动清除器

AD9545:快速输入,10输出,双DPLL/IEEE1588 1小步同步和Jetter Clearan数据Sheet

AD9554四路PLL、四通道输入、八通道输出多服务线路卡自适应时钟转换器技术手册

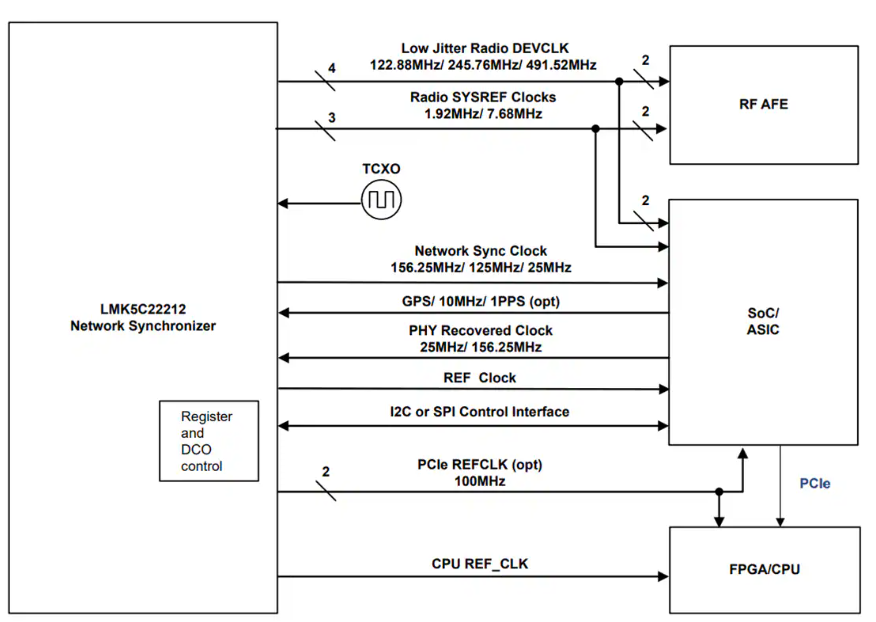

Texas Instruments LMK5C22212AS1网络同步器数据手册

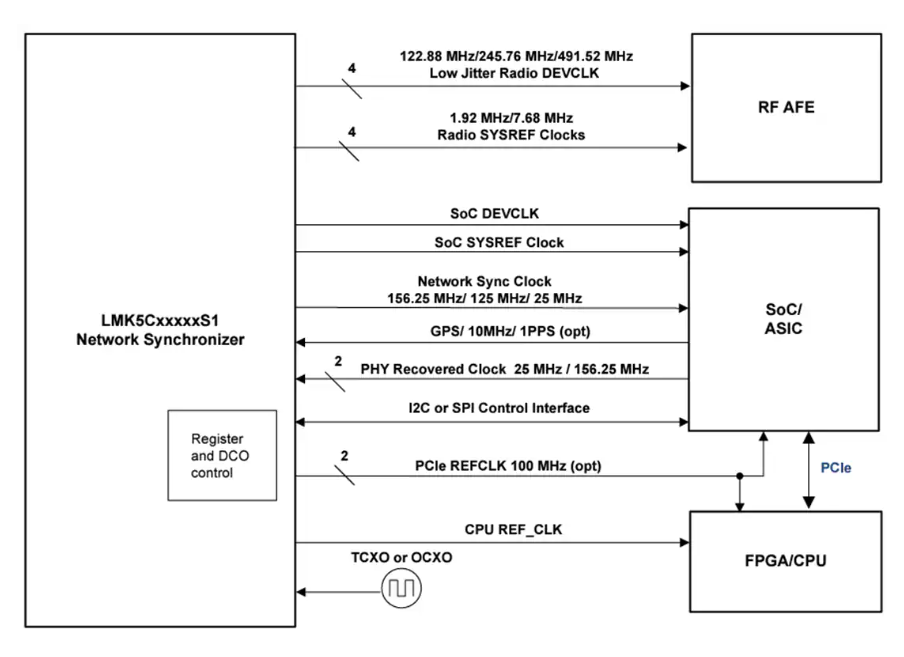

Texas Instruments LMK5C33216AS1网络同步器数据手册

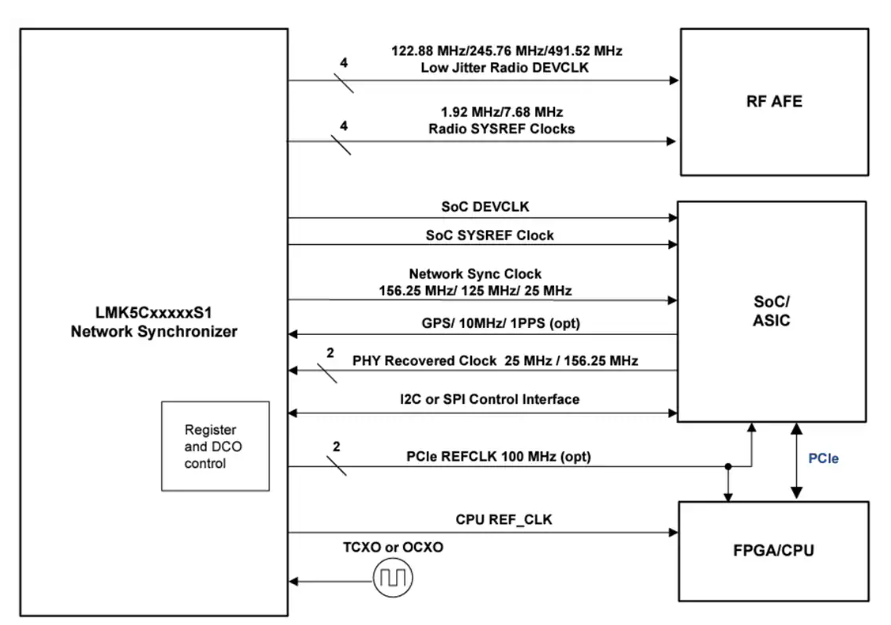

Texas Instruments LMK5C33414AS1网络同步器数据手册

LMK5C33216A 网络同步器与抖动清除器总结

AD9543四通道输入、10路输出、双通道DPLL/IEEE 1588同步器和抖动清除器技术手册

AD9543四通道输入、10路输出、双通道DPLL/IEEE 1588同步器和抖动清除器技术手册

评论