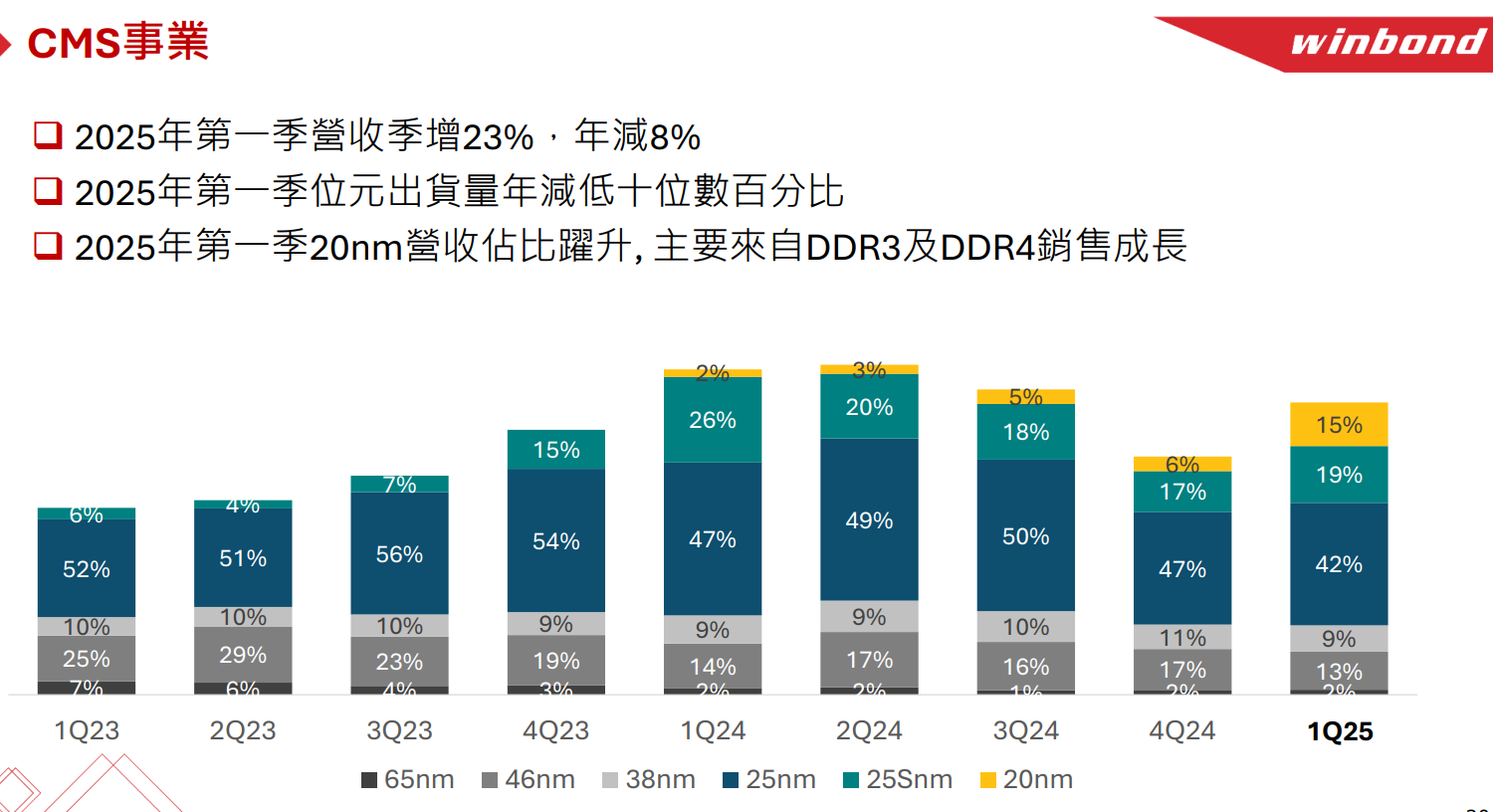

电子发烧友网报道(文/黄晶晶)前段时间,三星、SK海力士、美光等DRAM大厂已计划陆续退出部分DDR4市场,将产能转向DDR5、LPDDR5和HBM。由此引发DDR4供应链波动,同时在供给不足的担忧

2025-06-19 00:54:00 10155

10155

探索IDT74SSTUBF32866B:DDR2的25位可配置寄存器缓冲器 在DDR2内存模块的设计中,拥有高性能且稳定的寄存器缓冲器至关重要。Renesas的IDT74SSTUBF32866B就是

2025-12-24 16:30:09 124

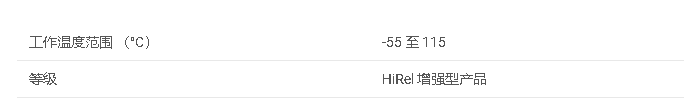

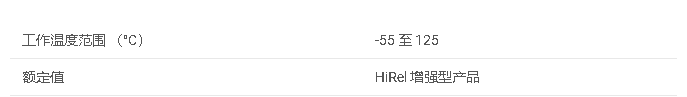

124 爱普生33.33MHz车规晶振X1E0003410500凭借±20ppm高稳、1ps低抖动及-40℃~125℃宽温,为FPGA时钟树提供AEC-Q100认证基准时钟。其6ms快启与抗振特性保障高速SerDes与DDR4接口信号完整性,满足ADAS与工业控制系统的严苛时序需求。

2025-12-18 10:15:00 222

222

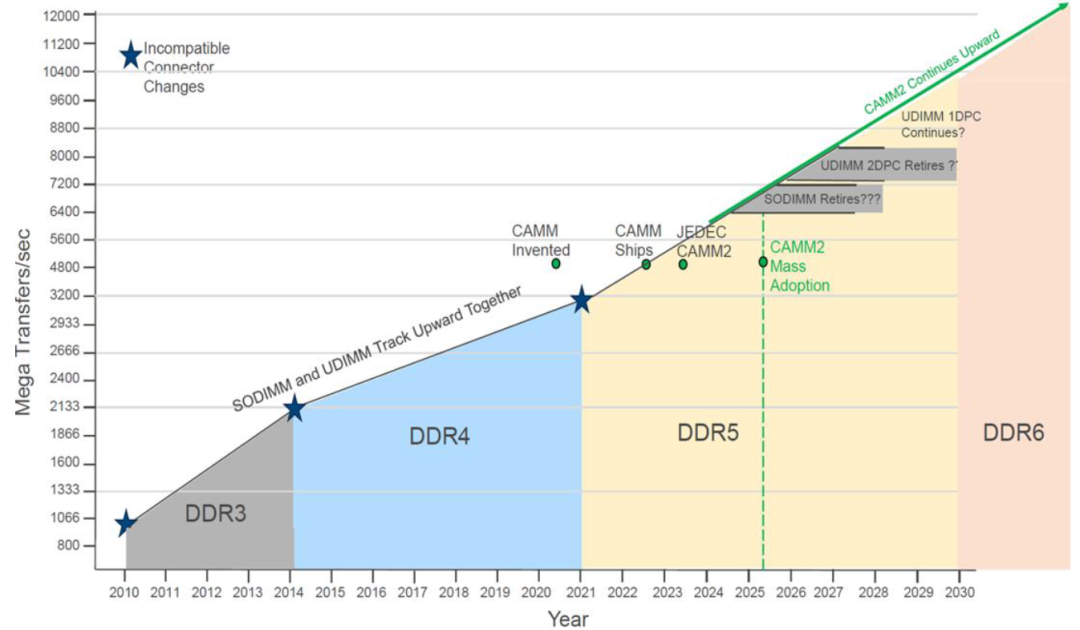

在计算机和电子设备中,存储器扮演着数据临时存放与快速交换的关键角色。其中,DDR SDRAM(双数据速率同步动态随机存取存储器)已成为现代内存的主流技术之一。它不仅在速度上显著超越前代产品,更凭借其高效传输机制,广泛应用于电脑、服务器、移动设备及各类嵌入式系统中。

2025-12-08 15:20:44 293

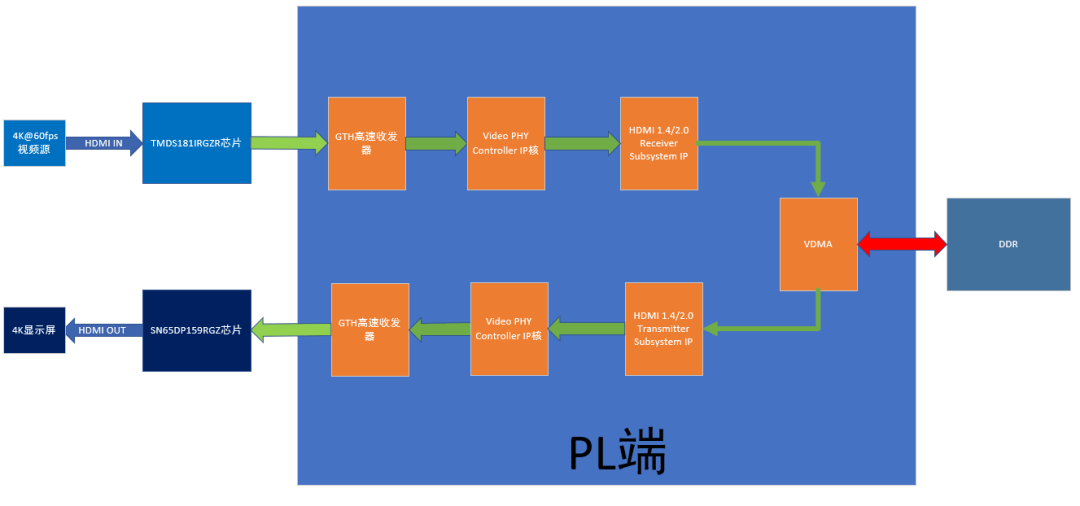

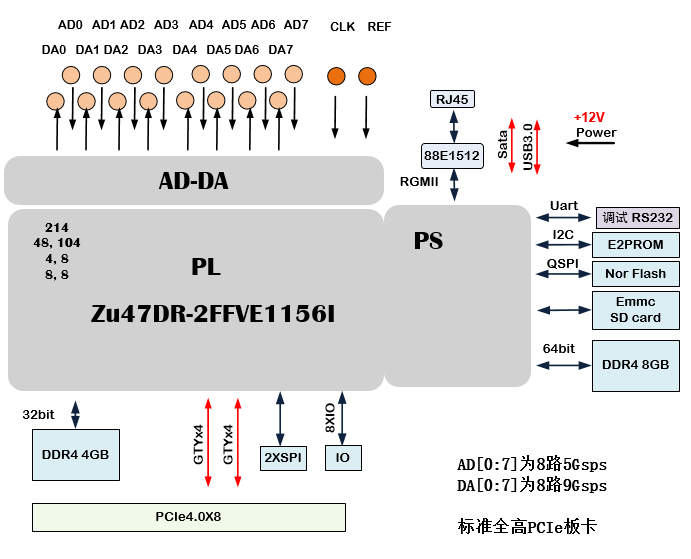

293 主处理器,完成复杂的数据采集、回放以及数据预处理。采用1片ZYNQSOC来完成信号处理算法。该平台的主处理器VU13P外挂两组72位DDR4SDRAM,来实现超大容量数

2025-12-04 16:02:34 287

287

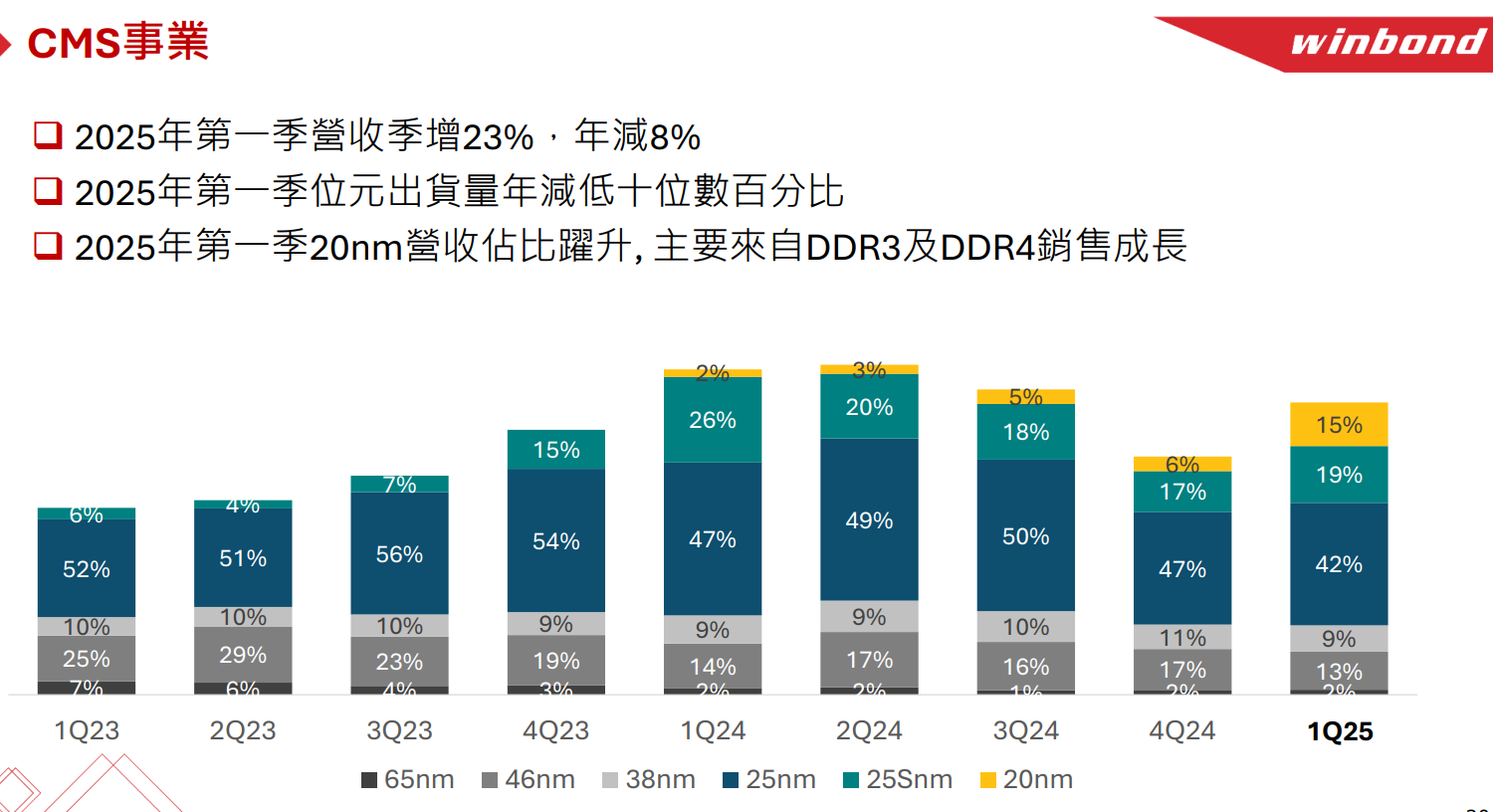

2025 年 12 月 3日,中国苏州 — 全球半导体存储解决方案领导厂商华邦电子今日宣布推出全新 8Gb DDR4 DRAM,该产品采用华邦自有先进 16nm 制程技术,提供更高速度、更低

2025-12-03 16:44:28 709

709

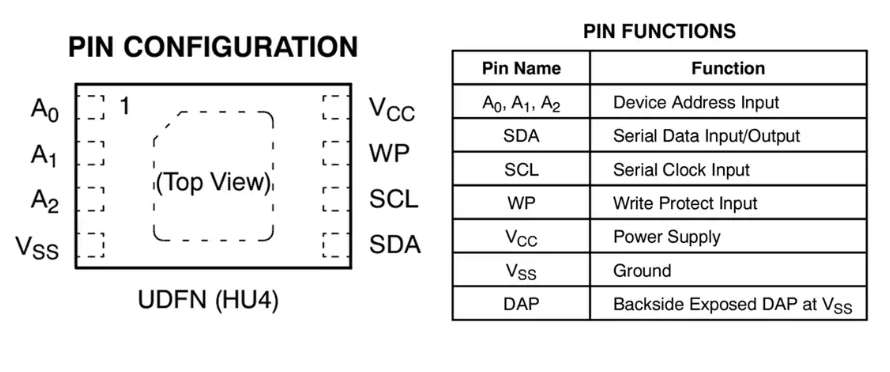

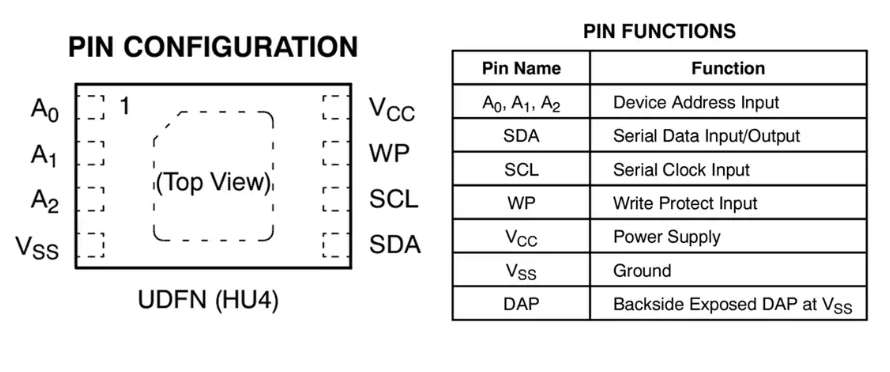

在电子设计领域,对于DDR4 DIMM的设计,EEPROM的选择至关重要。N34C04作为一款专门为DDR4 DIMM设计的EEPROM Serial 4 - Kb器件,实现了JEDEC

2025-11-27 14:42:12 306

306

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

TPS650061RUKR进行电源设计。电源输出1.2v,1.8v,3.3v均正常。

由于板子未挂载SDRAM或DDR,将程序的下载地址改为L2RAM(0x11800000)位置也没办法正确load,并通过JTAG调试

2025-11-19 19:53:00

(Shinshu University)研究团队的最新设计中,一个专为 Xilinx 7 系列 FPGA 量身打造的 4 位乘法器使用了仅 11 个 LUT + 2 个 CARRY4 块,关键路径延迟达到 2.75 ns。这是一次令人印象深刻的工艺优化实践。

2025-11-17 09:49:40 3274

3274

Xilinx FPGA因其高性能和低延迟,常用于串行通信接口设计。本文深入分析了Aurora、PCI Express和Serial RapidIO这三种在Xilinx系统设计中关键的串行通信协议。介绍了它们的特性、优势和应用场景,以及如何在不同需求下选择合适的协议。

2025-11-14 15:02:11 2357

2357

下面是HummingBird EV Kit给的版图,其中DDR3_D0对应的应该是板子上的FPGA的C2引脚:

不过我在配置MIG的时候,通过读入ucf文件的方式配置DDR3 SDRAM的引脚

2025-11-06 07:57:09

电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4 在有些情况下,我们想要把代码放到SDRAM运行。下面介绍在APM32的MCU中,如何把代码重定位到SDRAM运行。对于不同APM32系列的MCU,方法都是一样的。

2025-11-04 09:14:18 4981

4981

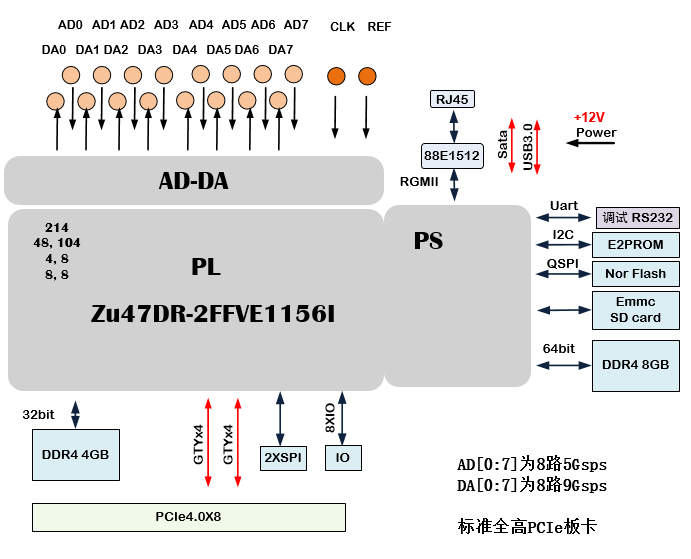

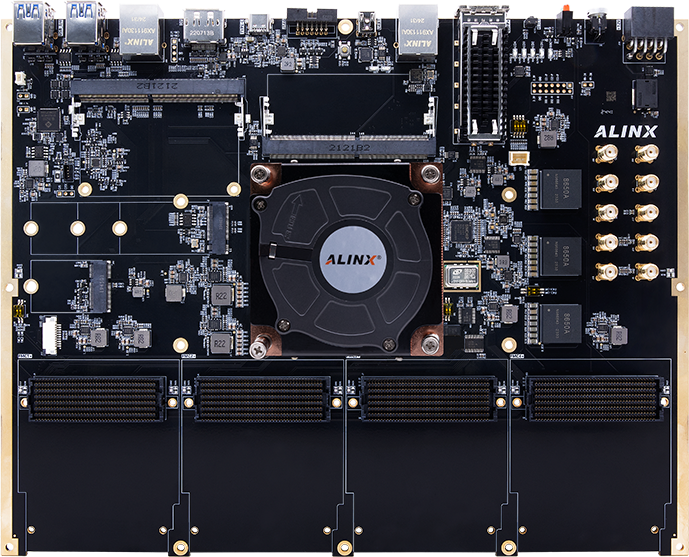

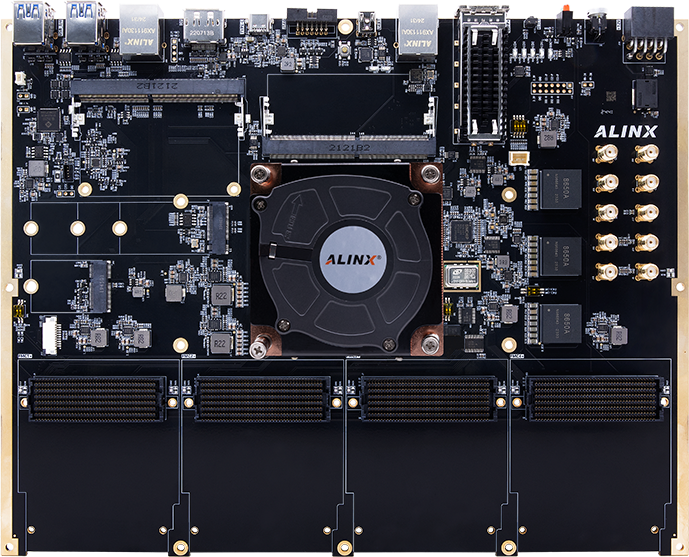

识别。该板卡的PS端支持1组72位DDR4 SDRAM,PL端支持1组32位DDR4 SDRAM,支持1片32GB EMMC存储单元,支持2片QSPI FLASH

2025-11-03 16:35:26

:

http://www.digilent.com.cn/products/product-nexys-4-ddr-artix-7-fpga-trainer-board.html

NexysVideo

2025-10-31 07:26:13

由于FPGA内部存储资源有限,很多时候不能满足需求,因此可以利用DDR对系统进行存储扩展。由于DDR3内部控制十分复杂,因此可以基于AXI总线,利用Vivado提供的MIG IP对DDR3进行控制

2025-10-29 07:16:34

SD卡和OV5640的数据搬运进DDR中。

Setting

Value

Memory Type

DDR3 SDRAM

Max. clock period

3000ps

Clock ratio

4

2025-10-28 07:24:01

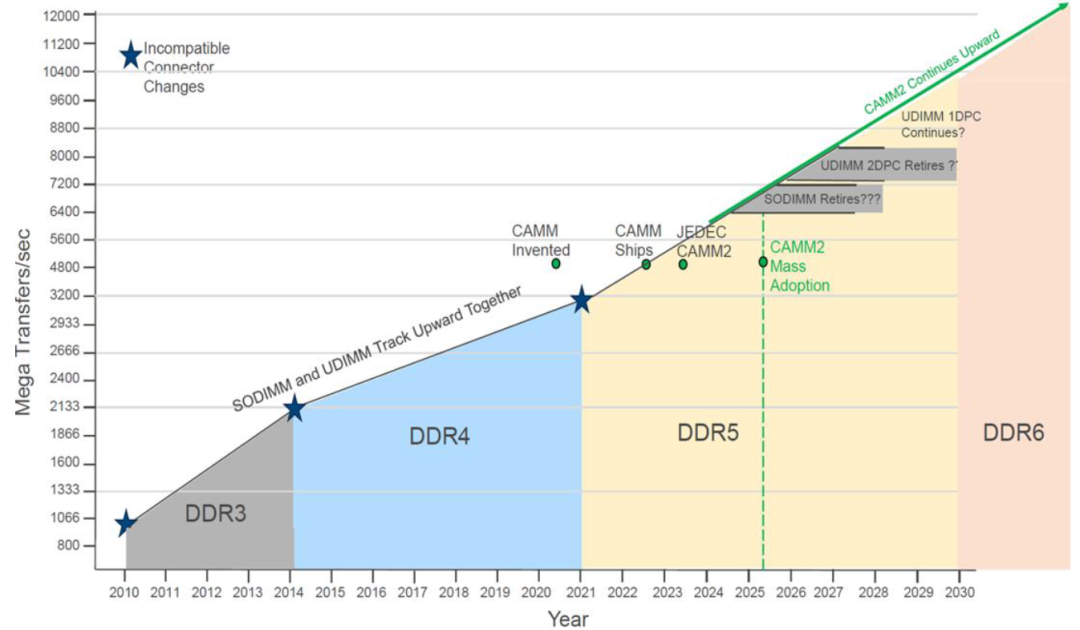

DDR 的比较以及 DDR5 与 LPDDR5 的差异以及 DDR5 的拓扑结构。 什么是 DDR5? 先来看一下什么是 DDR 。 DDR(Double Data Rate)属于SDRAM

2025-10-27 19:28:16 7360

7360

电子发烧友网综合报道 “早知道就多囤几根内存条了!”——这是2025年10月电商促销季里,无数DIY玩家与渠道商发出的共同感叹。如今,DDR4 16GB内存价格突破500元,一年内涨幅超两倍,赚钱

2025-10-22 09:19:37 10310

10310

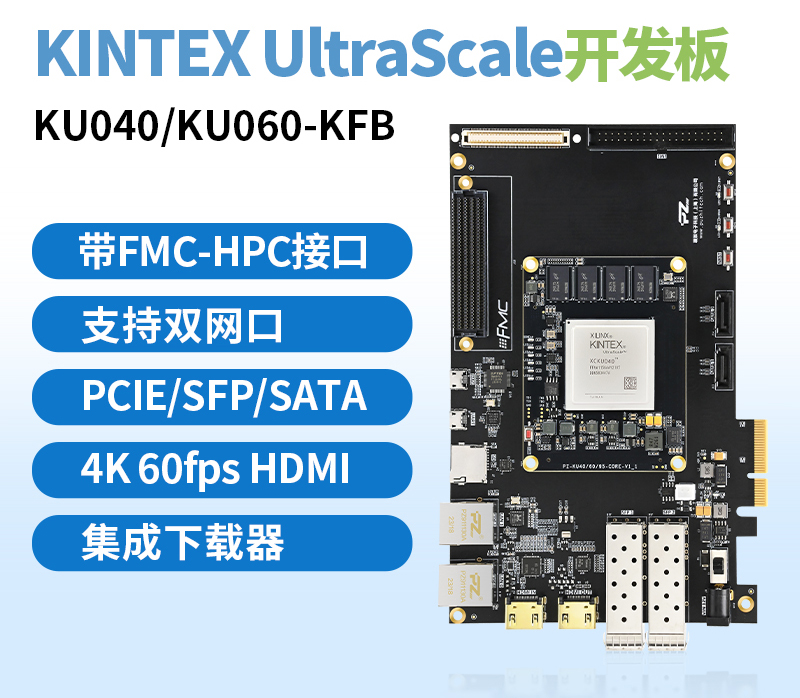

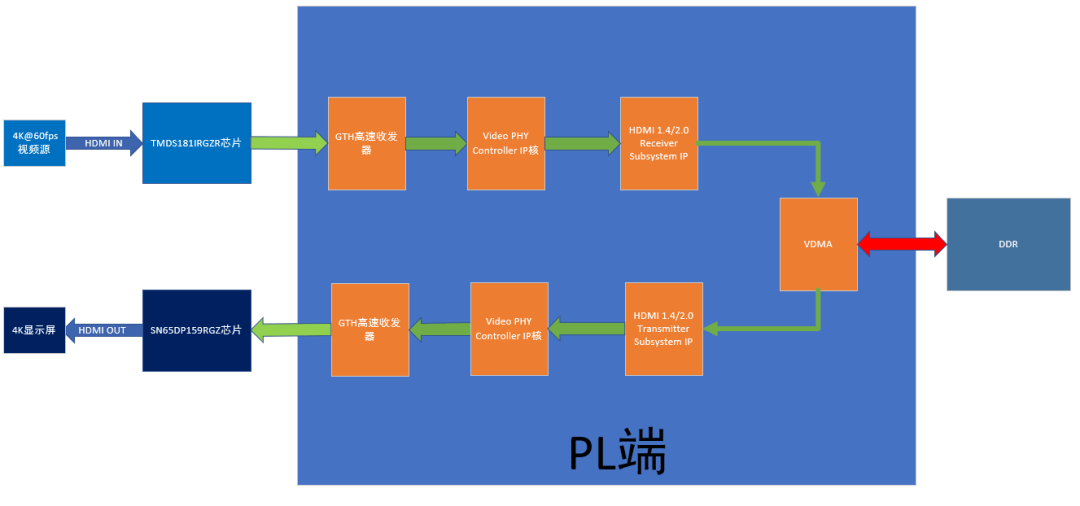

该平台的PL端具有1个FMC(HPC)接口,1路PCIe x4主机接口,支持1组64位DDR3 SDRAM大容量缓存、支持1路1000BASE-T千兆以太网接口、支持1路3G SDI输入接口、支持1路3G SDI输出接口,支持1路HDMI输入接口、支持1路HDMI输出接口。

2025-10-21 18:47:47 496

496

DDR控制协议

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源

2025-10-21 14:30:16

蜂鸟DDR200T中DDR3的ip配置案列,提供DDR3引脚配置。具体参数可更具项目实际更改。

这里选用的axi接口

在赛灵思的IP配置中没有MT41K28M6JT-125K内存的信息,因此选用

2025-10-21 11:19:08

,DDR SDRAM的最大特点是双边沿触发,即在时钟的上升沿和下降沿都能进行数据采集的发送,同样的工作时钟,DDR SDRAM的读写速度可以比传统的SDRAM快一倍。

DDR3读写控制器可以在Xilinx

2025-10-21 10:40:28

DDR3读写控制器主要用于生成片外存储器DDR3 SDRAM进行读写操作所需要的时序,继而实现对片外存储器的读写访问。由摄像头采集得到的图像数据通常数据量较大,使用片内存储资源难以实现大量图像数据

2025-10-21 08:43:39

在 FPGA 中测试 DDR 带宽时,带宽无法跑满是常见问题。下面我将从架构、时序、访问模式、工具限制等多个维度,系统梳理导致 DDR 带宽跑不满的常见原因及分析方法。

2025-10-15 10:17:41 735

735 三星近期已向全球 OEM 客户发出正式函件,明确旗下 DDR4 模组将于 2025 年底进入产品寿命结束(EOL)阶段,最后订购日期定于 6 月上旬,最后出货日期则为 12 月 10 日。此次停产

2025-10-14 17:11:37 1033

1033 10月10日,以“碳硅共生 合创AI+时代”为主题的2025中国移动全球合作伙伴大会上,芯盛智能科技(湖南)有限公司携手中国移动通信集团终端有限公司联合发布基于1Xnm工艺制程的全国产DDR4内存产品,这一成果彰显了数字基建自主可控又迈出了关键一步,为数字中国建设提供了更安全可靠的硬件支撑。

2025-10-13 14:28:55 1423

1423 回收DDR2,回收DDR3,收购DDR2,收购DDR3 DDR4 DDR5长期现金高价回收DDR,回收三星DDR,回收海力士DDR,回收南亚DDR,回收尔必达DDR,回收美光DDR,回收DDR

2025-10-09 14:15:34

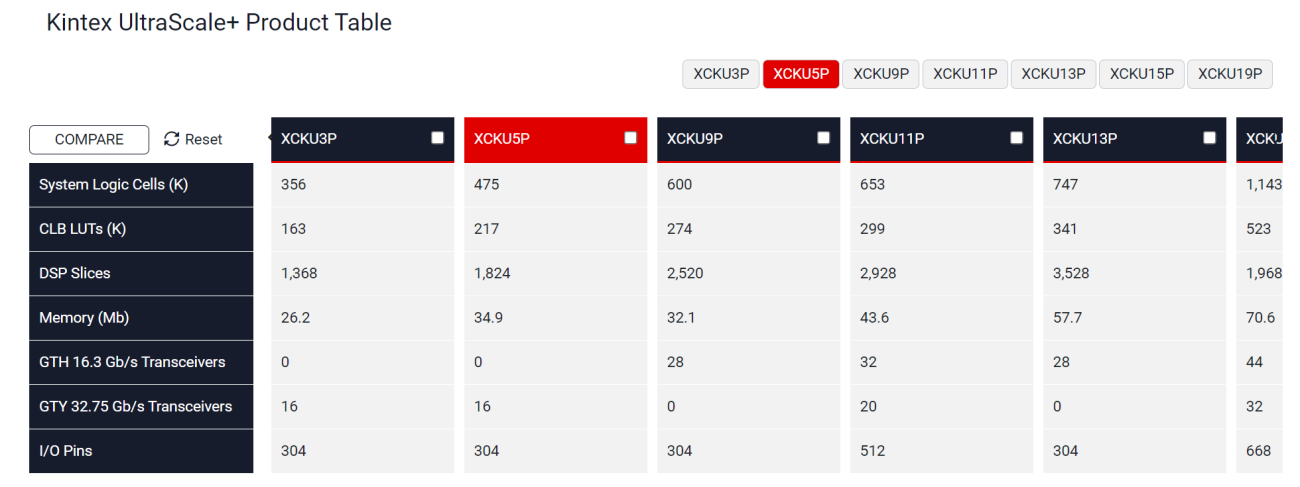

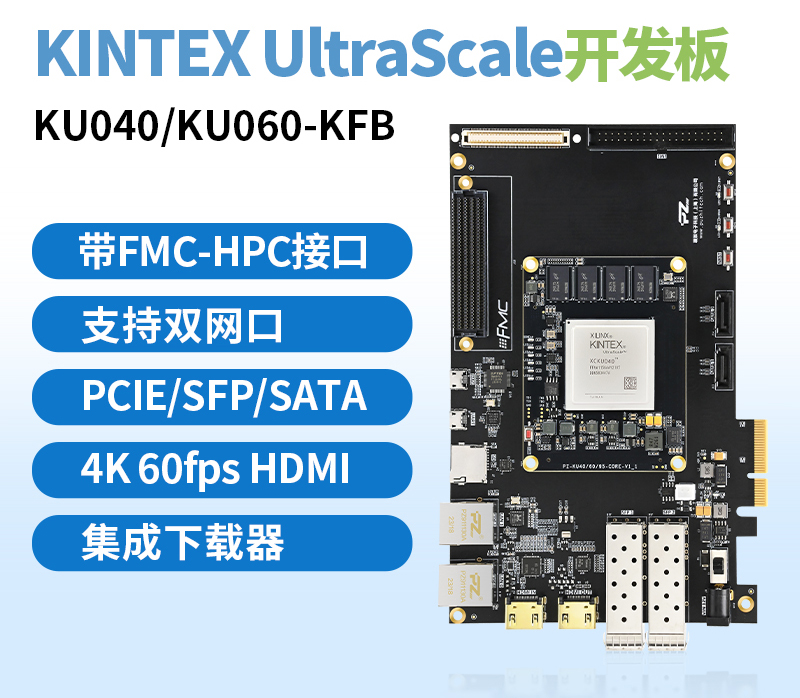

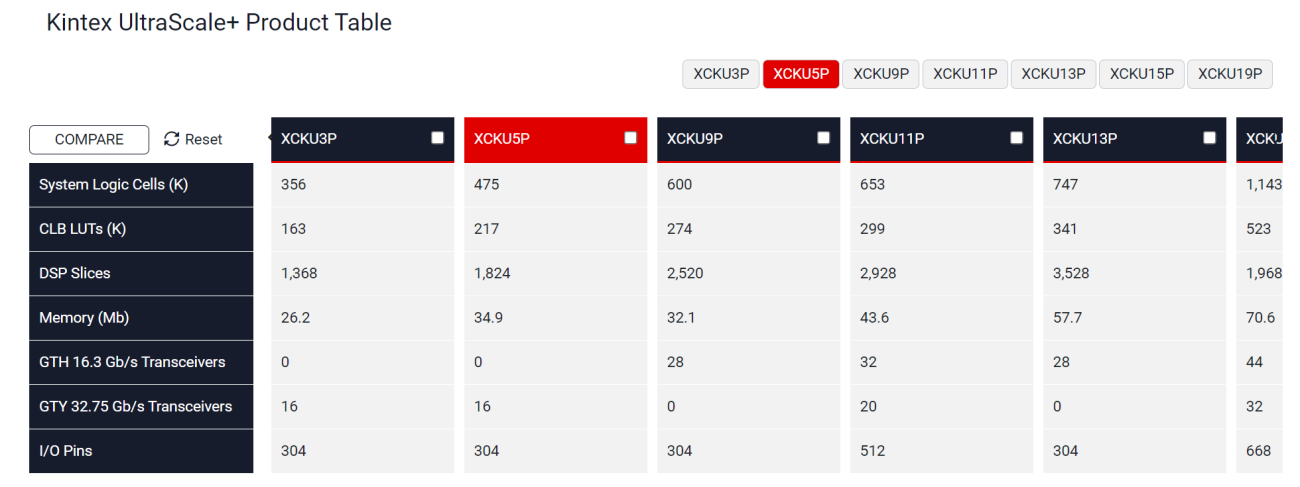

的Kintex UltraScale+开发板采用核心板+底板结构,核心板提供KU3P/KU5P两种型号,配备2GB DDR4、256Mb QSPI Flash等资源,通过240P高速连接器与底板连接。底板集成了千兆以太网、QSFP28、MIPI、FMC、PCIe等丰富接口,并内置USB-JTAG调试器

2025-09-26 10:46:19 782

782

1组72位DDR4 SDRAM,PL端支持1组32位DDR4 SDRAM,支持1片32GB EMMC存储单元,支持2片QSPI FLASH用于FPGA的加载,支持

2025-09-15 14:37:00

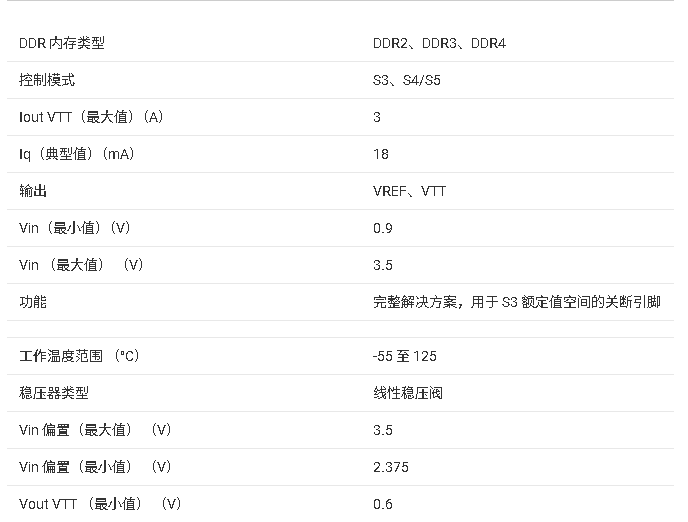

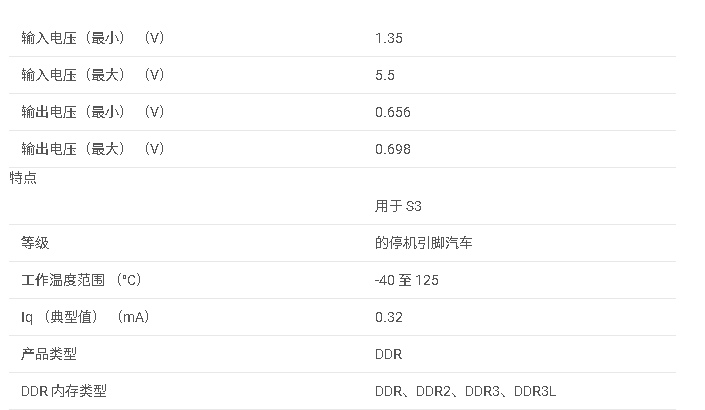

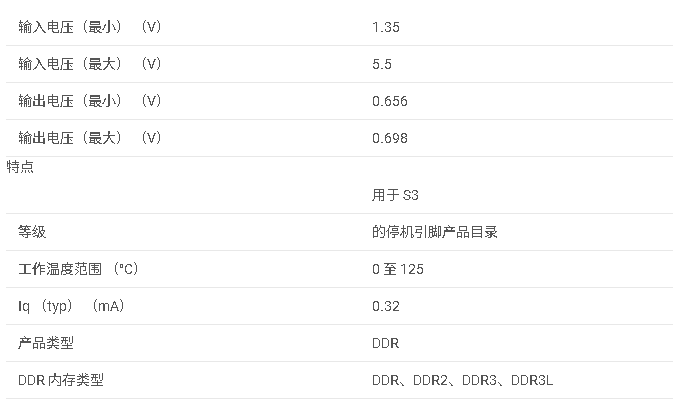

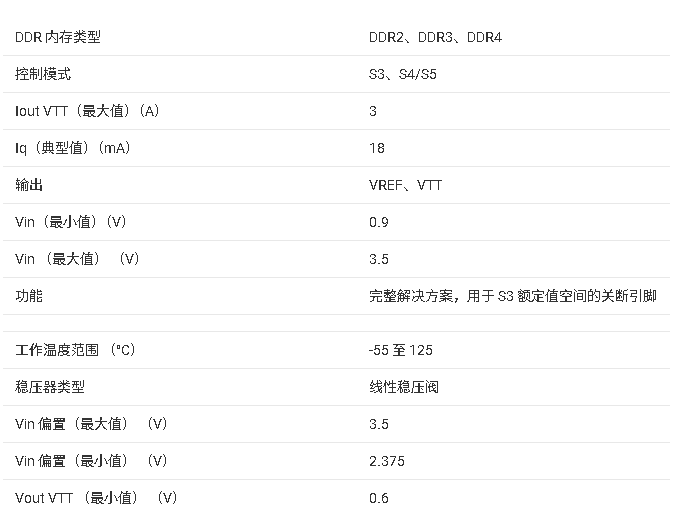

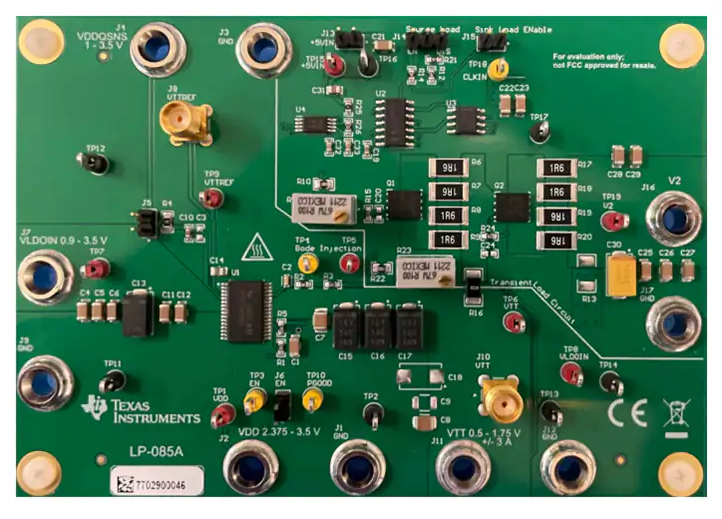

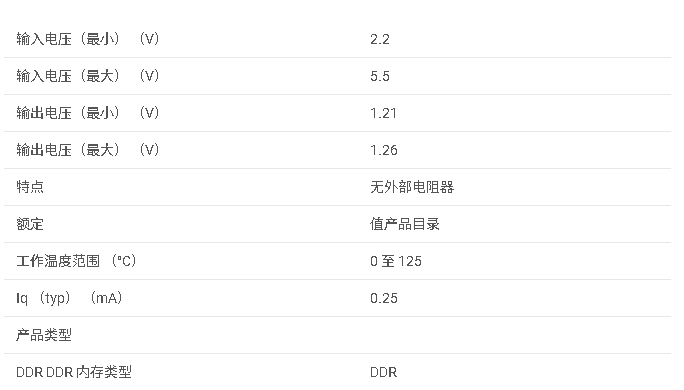

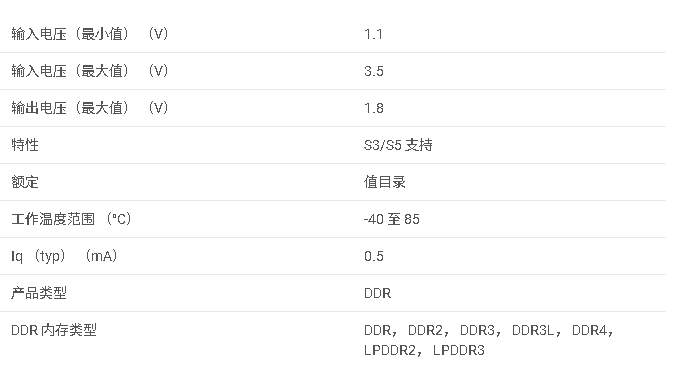

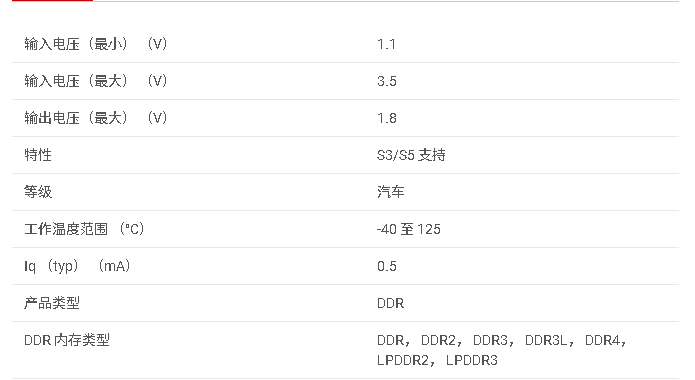

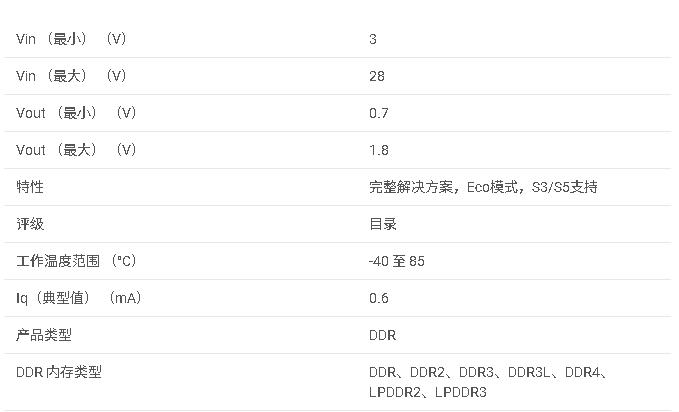

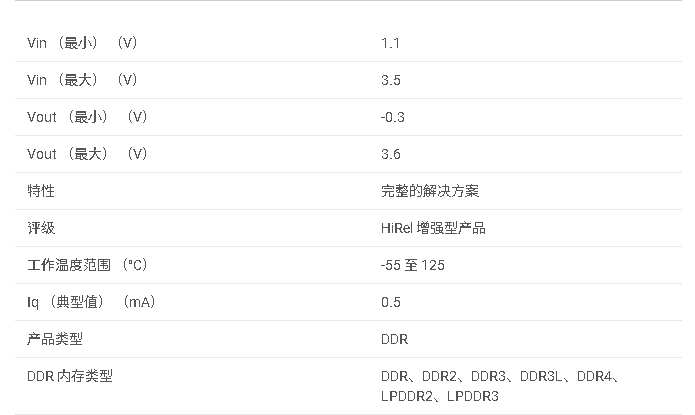

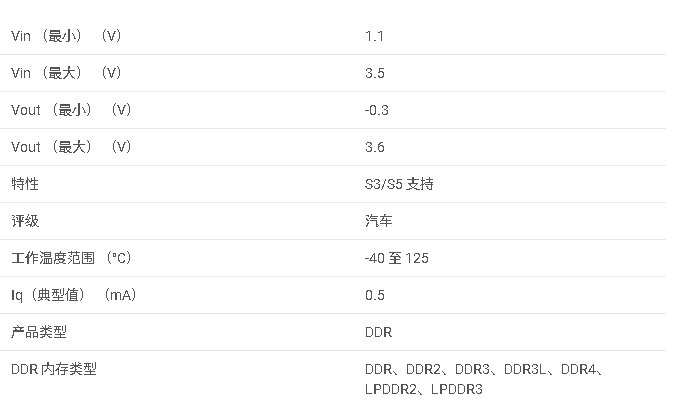

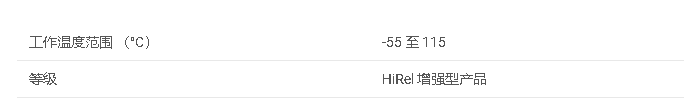

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接应用。TPS7H3301-SP VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源。在

2025-09-09 14:45:15 719

719

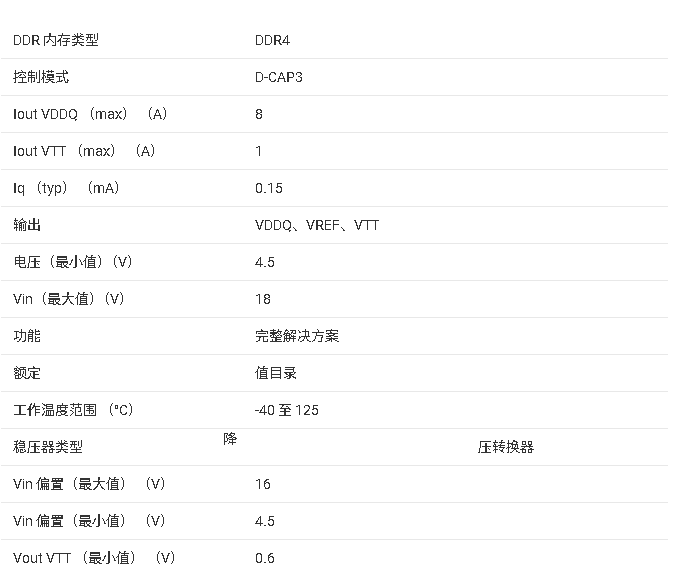

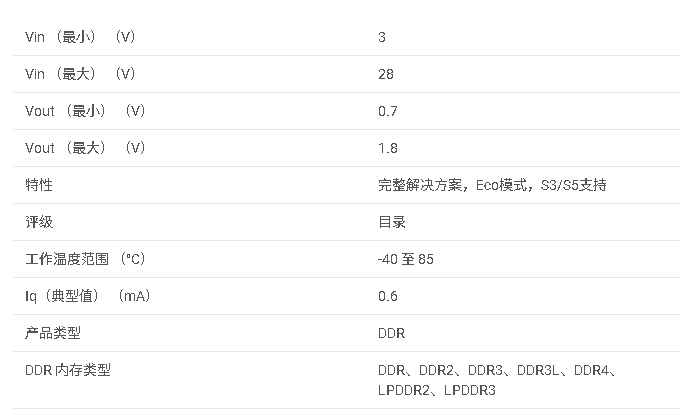

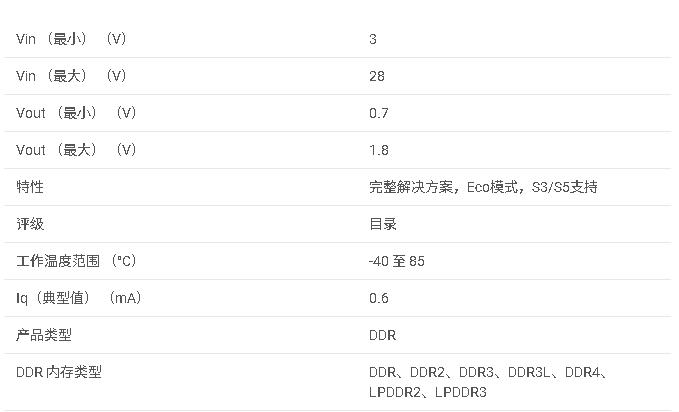

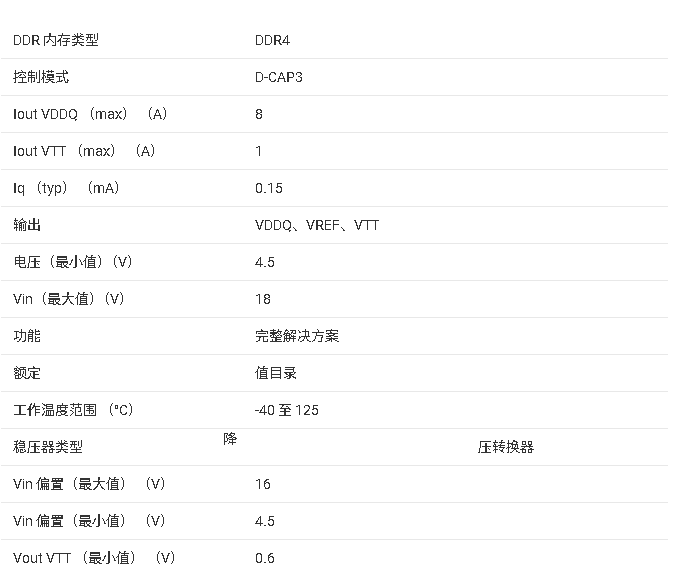

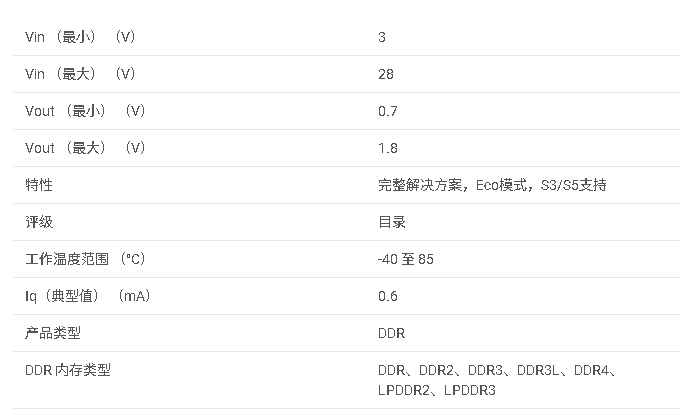

TPS65295器件以最低的总成本和最小的空间为 DDR4 内存系统提供完整的电源解决方案。它符合 DDR4 上电和断电序列要求的 JEDEC 标准。该TPS65295集成了两个同步降压转换器

2025-09-09 14:16:04 1732

1732

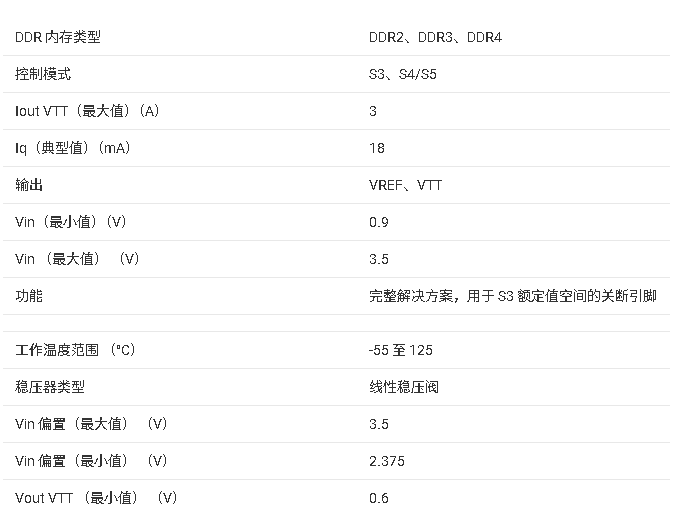

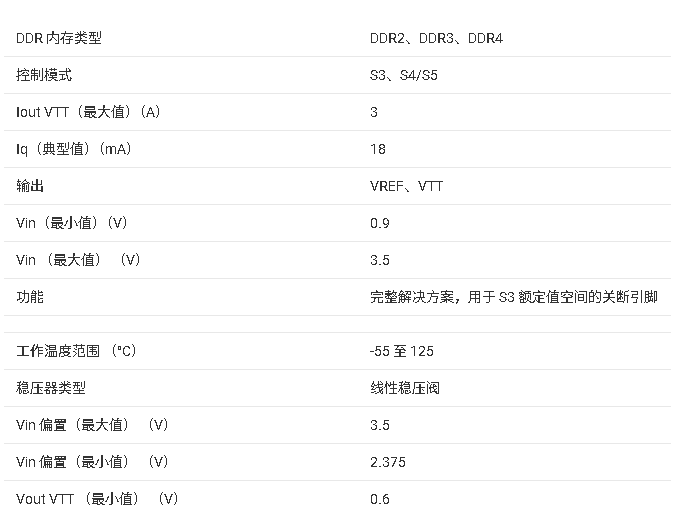

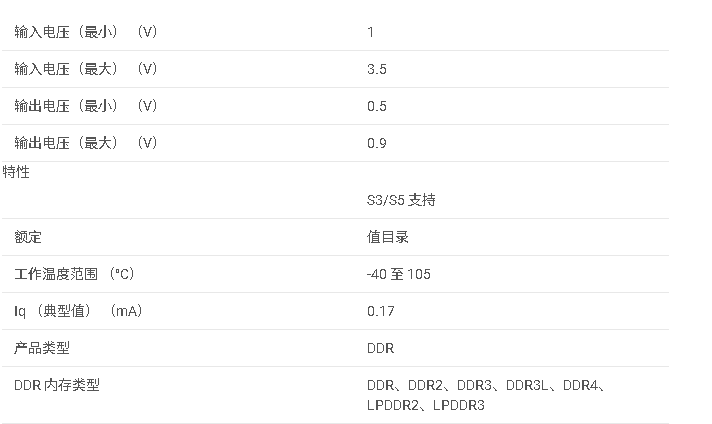

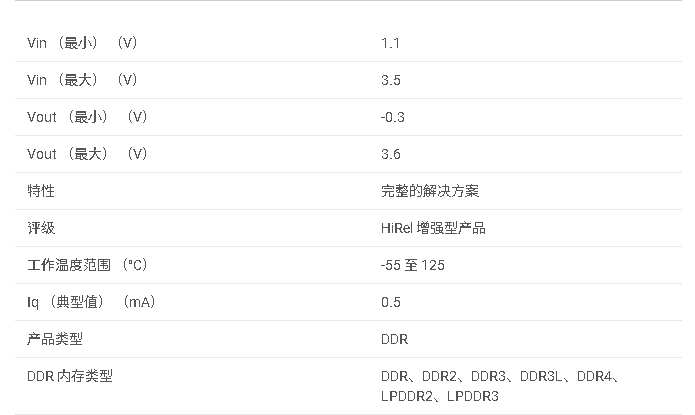

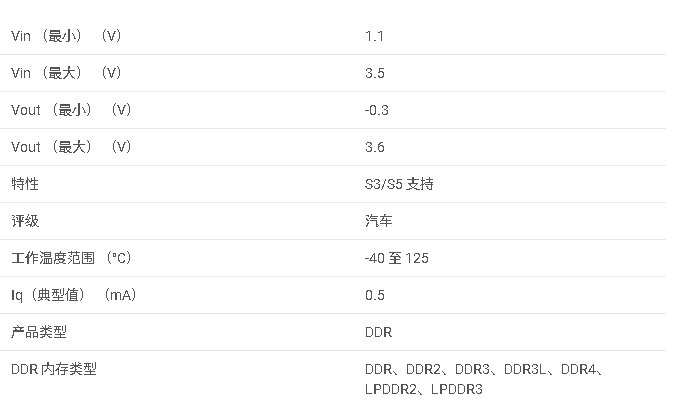

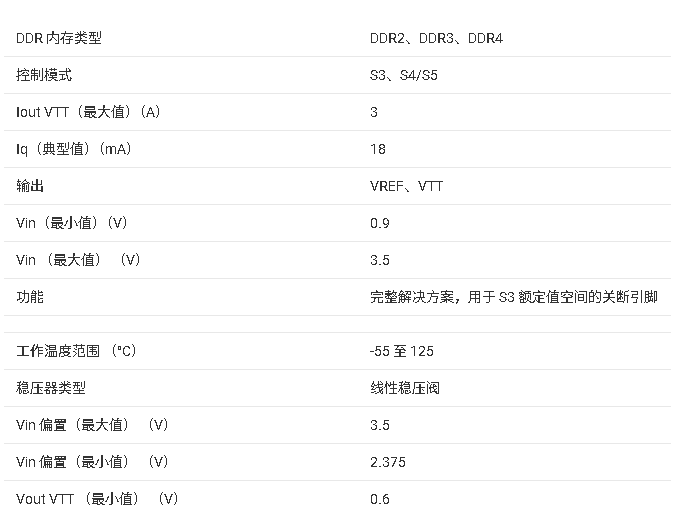

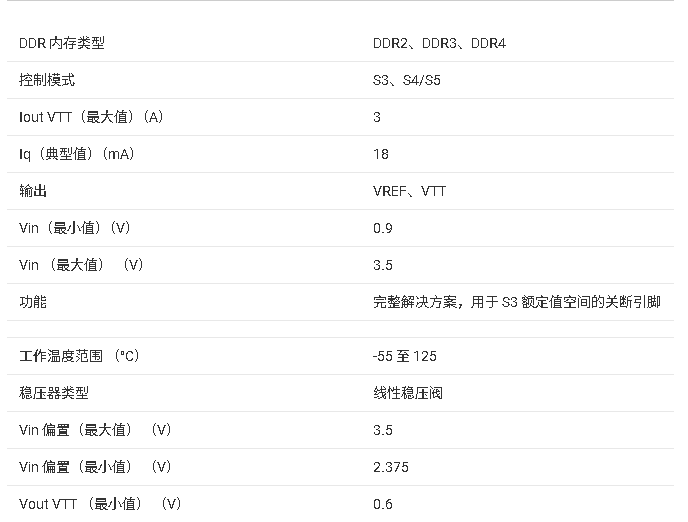

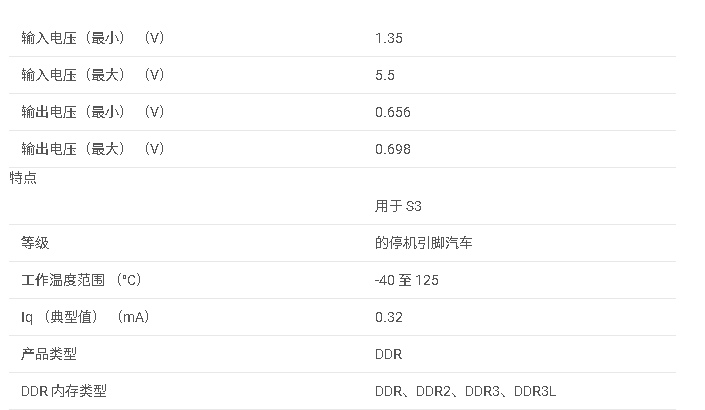

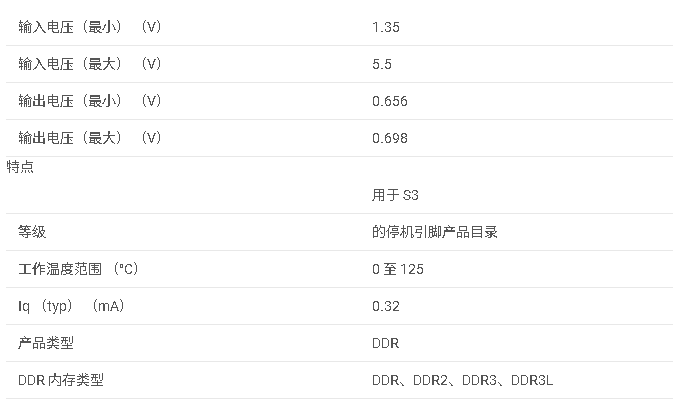

该TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接应用。TPS7H3302 VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源

2025-09-09 13:53:22 688

688

该TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接应用。TPS7H3302 VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源

2025-09-09 13:48:37 756

756

的技术支持和行业化的应用方案,贞光科技正在帮助更多客户在供应链安全与性能需求之间找到平衡。全系列产品覆盖:从SDR到DDR4紫光国芯在DRAM领域的技术积累超过十年,产品

2025-09-03 16:22:46 1511

1511

本文旨在通过讲解不同模式的原理图连接方式,进而配置用到引脚的含义(手册上相关引脚含义有四、五页,通过本文理解基本上能够记住所有引脚含义以及使用场景),熟悉xilinx 7系列配置流程,以及设计原理图时需要注意的一些事项,比如flash与FPGA的上电时序。

2025-08-30 14:35:28 9291

9291

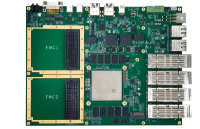

作为主处理器,FPGA 外挂两组 72 位 DDR4 SDRAM,用来实现超大容量数据缓存,DDR4 的最高数据缓存带宽可以达到2400MHz,DDR4 的缓存

2025-08-29 15:57:37 398

398

:XCKU115-2FLVF1924I 作为主处理器,FPGA 外挂两组 72 位 DDR4 SDRAM,用来实现超大容量数据缓存,DDR4 的最高数据缓存带宽可以达到 2400M

2025-08-29 15:49:41

DDR4SDRAM,用来实现超大容量数据缓存,FPGA的PS端外挂1组72位的DDR4SDRAM的高速数据缓存,用来支持操作系统的运行。该平台支持2个FMC+接口,每个F

2025-08-29 15:29:49 1292

1292

DDR4 SDRAM,用来实现超大容量数据缓存,FPGA的PS端外挂1组72位的DDR4 SDRAM的高速数据缓存,用来支持操作系统的运行。该平台支持2个FMC+接口,

2025-08-29 15:28:59

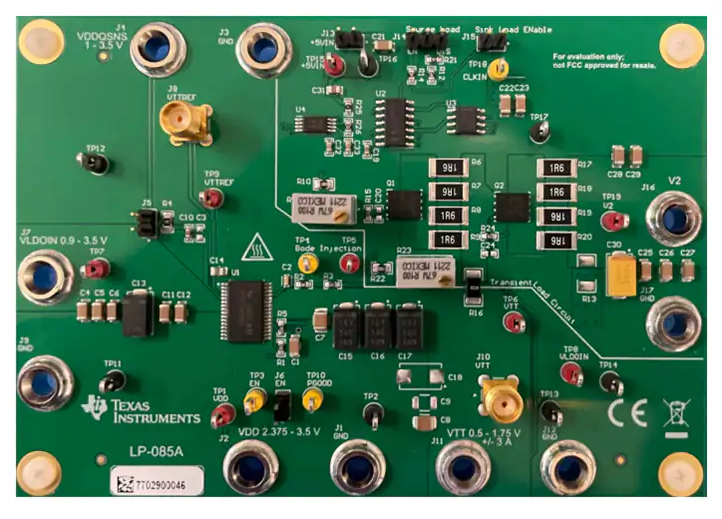

3A,支持测试DDR、DDR2、 DDR3、DDR3L和DDR4。该评估模块配有方便的测试点和跳线,用于评估TPS7H3302-SEP DDR端子。TPS7H3302EVM评估模块非常适合用于抗辐射DDR电源应用以及用于DDR、DDR2、DDR3和DDR4的存储器终端稳压器。

2025-08-27 16:14:21 831

831

璞致电子PZ-KU060-KFB开发板采用Xilinx Kintex UltraScale KU060芯片,提供高密度并行计算能力,配备4GB DDR4内存、20对GTH高速收发器和多种扩展接口

2025-08-18 13:28:10 581

581

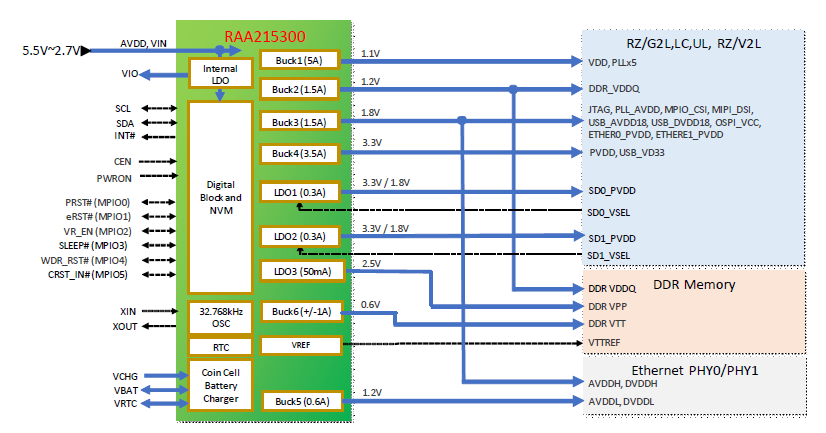

RZ/G2L微处理器配备Cortex-A55(1.2GHz)CPU、16位DDR3L/DDR4接口、带Arm Mali-G31的3D图形加速引擎以及视频编解码器(H.264)。此外,这款微处理器还

2025-08-04 13:40:03 3085

3085

关于 AMD/Xilinx 7系列FPGA存储器接口解决方案(UG586) 的用户指南,其主要内容和技术要点可概括如下:1. 文档定位与核心内容定位:该文档是7系列FPGA中存储接口控制器的官方

2025-07-28 16:17:45 3

3 超高速信号处理与光通信。其核心特性包括:16GB DDR4存储、PCIe3.0x8高速接口以及丰富的开发工具链支持。该产品适用于100G光通信、多通道雷达处理、超高速数据采集等尖端场景,为科研与工业应用提供高性能解决方案。璞致电子凭借十余年FPGA领域经验,致力于为全球客户提供可靠信号处理方案。

2025-07-24 09:05:19 773

773

及747K逻辑单元FPGA,形成"通用计算+实时控制+定制加速"架构。产品具备8GB DDR4/64GB eMMC存储、8×16.3Gb/s高速接口,支持-40~85℃宽温工作,适用于机器视觉、工业控制、医疗设备等领域。

2025-07-22 09:47:56 835

835

方式比较灵活,采用软核实现 DDR memory 的控制,有如下特点:

支持 DDR3

支持 x8、x16 Memory Device

最大位宽支持 32 bit

支持精简的 AXI4 总线协议

一个

2025-07-10 10:46:48

DRAM内存市场“代际交接”关键时刻2025年PC及服务器市场中,DDR4的渗透率约为20%-30%,而DDR5的渗透率约为70%-80%(TrendForce集邦咨询)。在AI算力爆发和先进

2025-07-09 11:11:24 1702

1702

北京贞光科技有限公司作为紫光国芯的核心代理商,贞光科技在车规级存储和工业控制领域深耕多年,凭借专业的技术服务能力为汽车电子、ADAS系统等高可靠性应用提供稳定供应保障。近期DDR4内存价格出现大幅

2025-06-27 09:45:11 4125

4125

,近期同样规格的16Gb产品中,DDR4 16Gb(1GX16)与DDR5 16G(2Gx8)的价格差距已达到1倍。 CFM闪存市场表示,去年三

2025-06-27 00:27:00 4539

4539 DDR内存占据主导地位。全球DDR内存市场正经历一场前所未有的价格风暴。由于原厂加速退出DDR3/DDR4市场,转向DDR5和HBM(高带宽内存)生产,DDR3和DDR4市场呈现供不应求、供需失衡、涨势延续的局面。未来,DDR5渗透率将呈现快速提升,市场份额增长的趋势。

2025-06-25 11:21:15 2010

2010

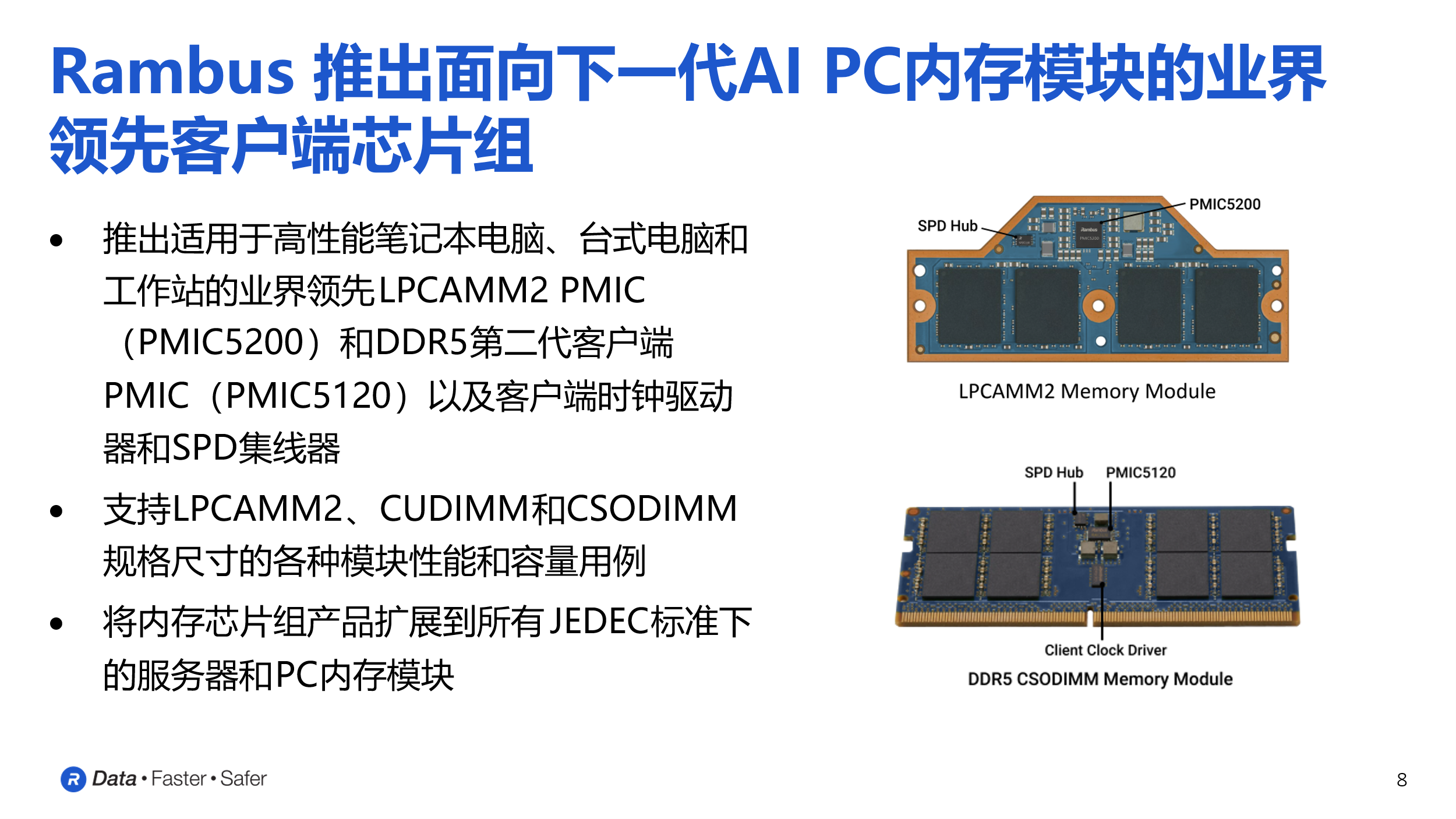

随着计算密集型任务的日益增长,DDR4内存的性能瓶颈已逐步显现。DDR5的出现虽解燃眉之急,但真正推动内存发挥极致性能的背后“功臣”——正是 DDR5 SPD(Serial Presence Detect)芯片。

2025-06-11 10:07:30 1913

1913

电子发烧友网站提供《XILINX XCZU67DR FPGA完整原理图.pdf》资料免费下载

2025-05-30 15:29:38 4

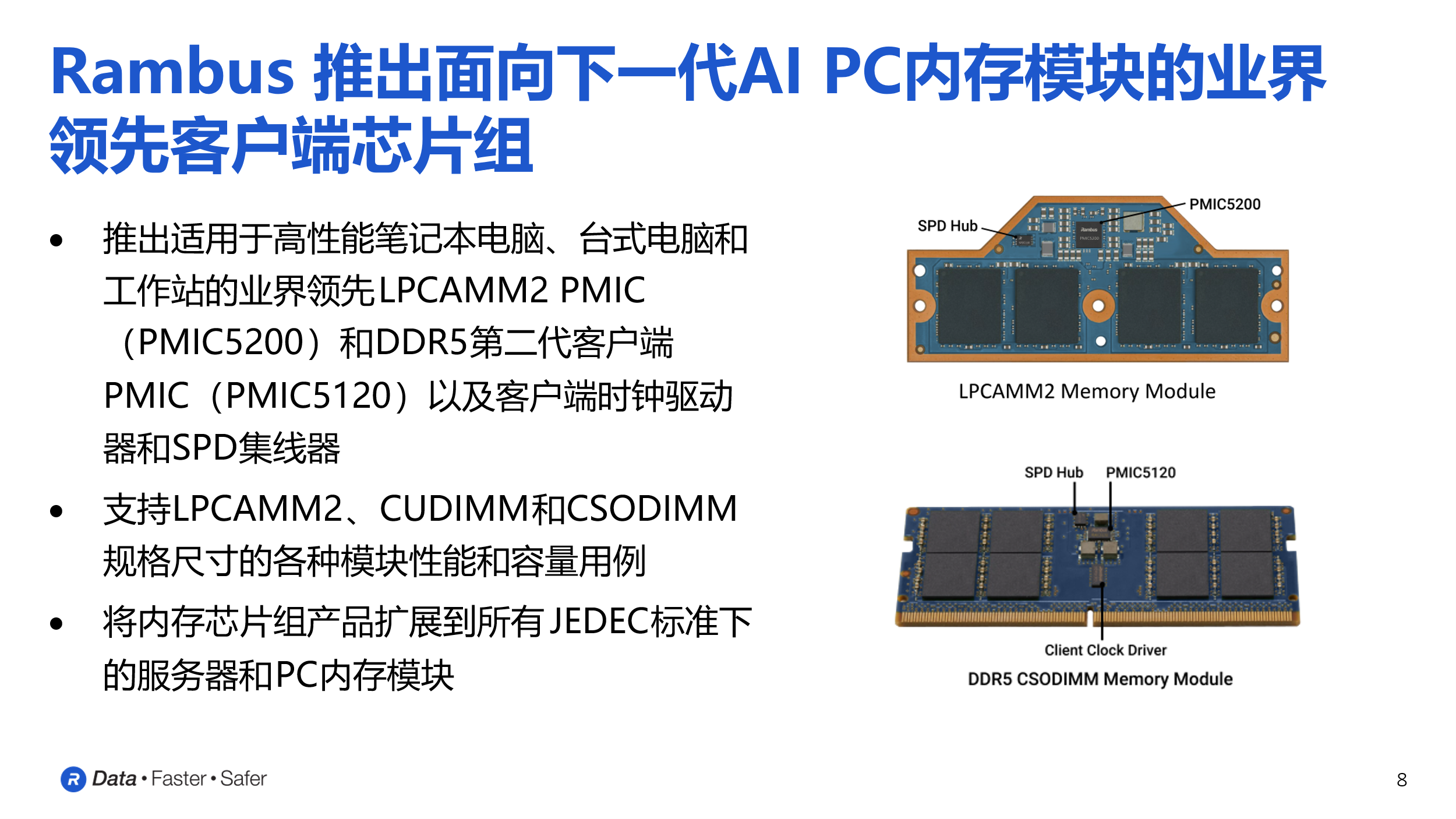

4 PC处理器对DDR5的支持,DDR5内存将更快渗透普及。相较于DDR4,所有电压由主板供给,DDR5中内存模组搭载PMIC,PMIC是实现高效供电的关键,能够为先进的计算应用提供突破性的性能表现。Rambus最近推出面向下一代AI PC内存模块的完整客户端芯片组,包含两款用于客户端计算的全新电源

2025-05-29 09:11:20 8127

8127

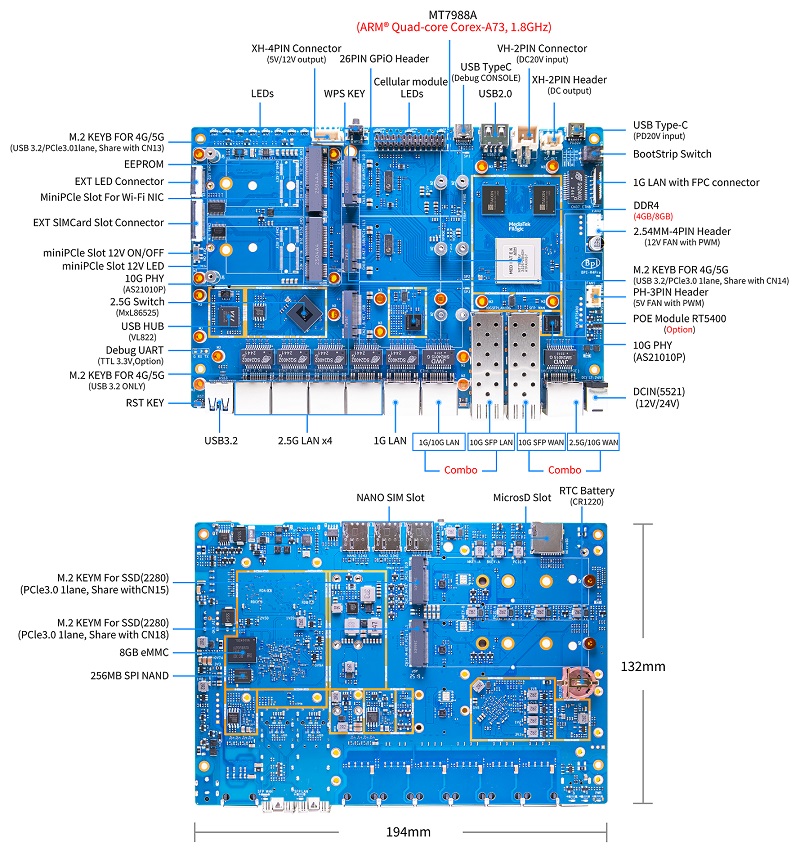

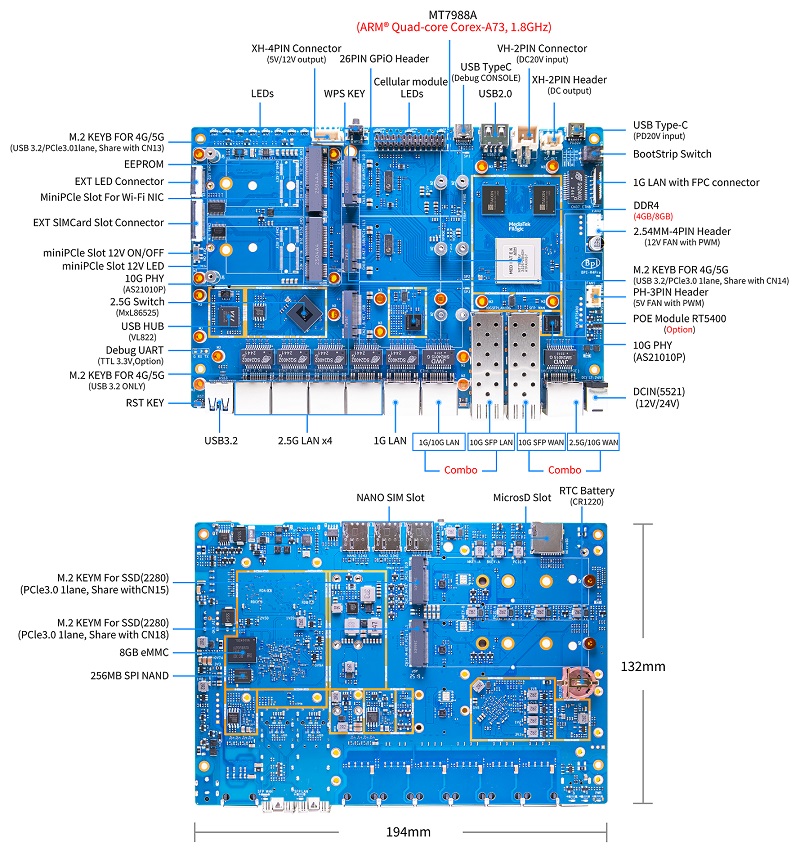

Banana Pi BPI-R4 Pro 路由器板采用联发科 MT7988A(Filogic 880)四核 ARM Corex-A73 设计,板载 4GB/8GB DDR4 RAM、8GB eMMC

2025-05-28 16:33:08 1793

1793

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一个 LogiCORE IP 核,用于在 FPGA 中实现高效的移位寄存器(Shift Register)。该 IP 核利用

2025-05-14 09:36:22 912

912 给大家带来一些业界资讯: 三星DDR4内存涨价20% 存储器价格跌势结束,在2025年一季度和第二季度,价格开始企稳反弹。 据TrendForce报道称,三星公司DDR4内存开始涨价,在本月

2025-05-13 15:20:11 1205

1205 最新消息,三星电子本月初与主要客户就提高DRAM芯片售价达成一致。DDR4 DRAM价格平均上涨两位数百分比;DDR5价格上涨个位数百分比。据称 DDR4 上调 20%,DDR5 上调约 5

2025-05-13 01:09:00 6843

6843 LP2995 线性稳压器旨在满足 JEDEC SSTL-2 和 SSTL-3 标准 DDR-SDRAM 终止规范。该器件包含一个高速运算放大器 对负载瞬变提供出色的响应。输出级可防止击穿,同时

2025-05-06 09:33:38 715

715

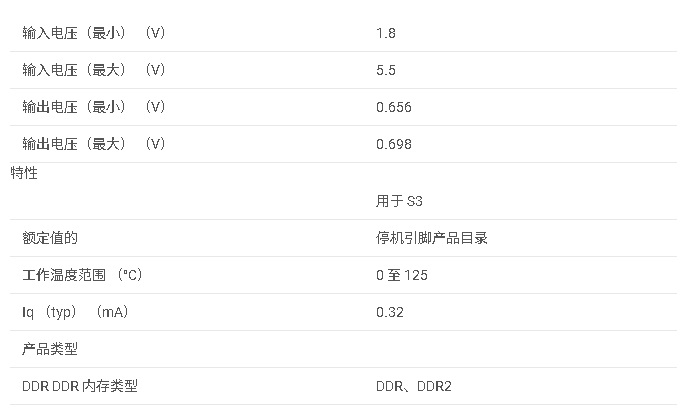

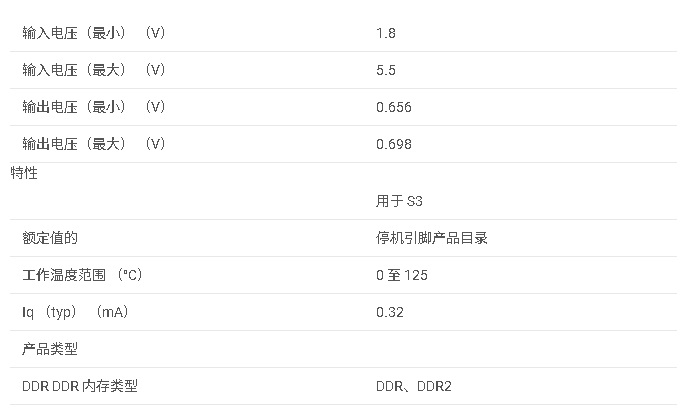

LP2996-N 和 LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 标准 DDR-SDRAM 终止规范。该器件还支持 DDR2,而 LP2996A 支持 DDR3 和 DDR

2025-04-29 18:11:05 834

834

TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 内存系统提供完整的电源。它将同步降压控制器与 3A 灌电流/拉

2025-04-29 16:38:02 1031

1031

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

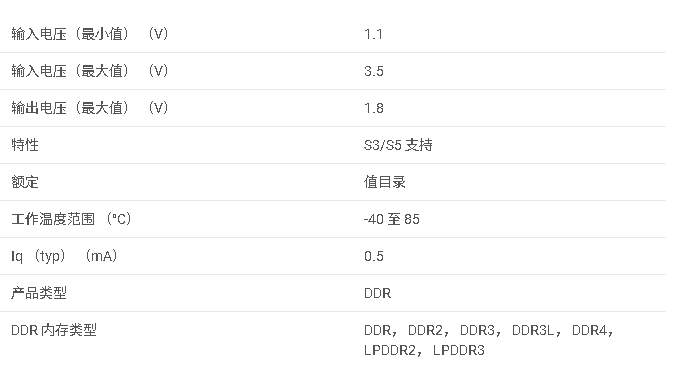

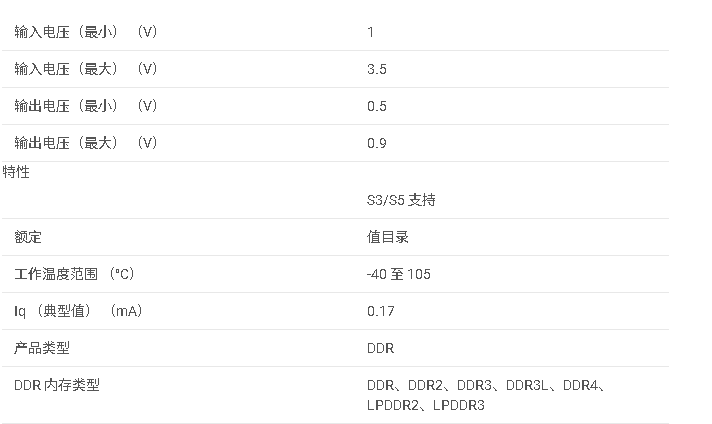

仅为 20 μF。该TPS51200支持远程感应功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

2025-04-29 09:59:25 1345

1345

只需要 20 μF 的最小输出电容。TPS51200-Q1 器件支持远程感应功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

2025-04-28 16:21:07 852

852

TPS51916 器件以最低的总成本和最小的空间为 DDR2、DDR3、DDR3L 和 DDR4 内存系统提供完整的电源。它集成了同步降压稳压控制器 (VDDQ),具有 2A 灌电流和 2A 源跟踪 LDO (VTT) 和缓冲低噪声基准 (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬态响应,并且只需要 1 × 10μF 的陶瓷输出电容。该器件支持远程感应功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 总线的所有电源要求。VTT 电流

2025-04-28 10:04:48 685

685

TPS51716为 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的电源 以最低的总成本和最小空间实现内存系统。它集成了一个同步降压 具有 2A 灌电流/拉电流跟踪 LDO

2025-04-27 11:36:05 763

763

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

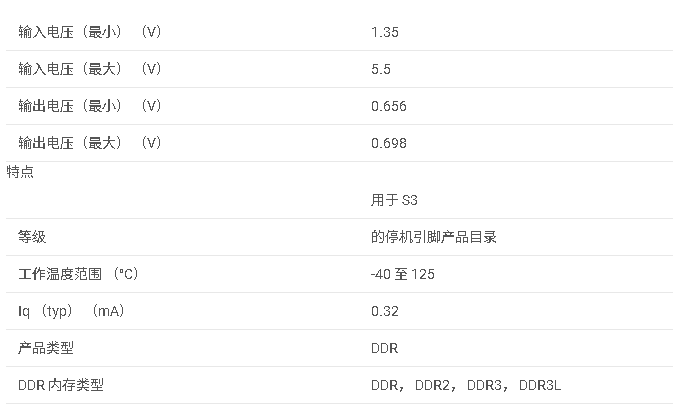

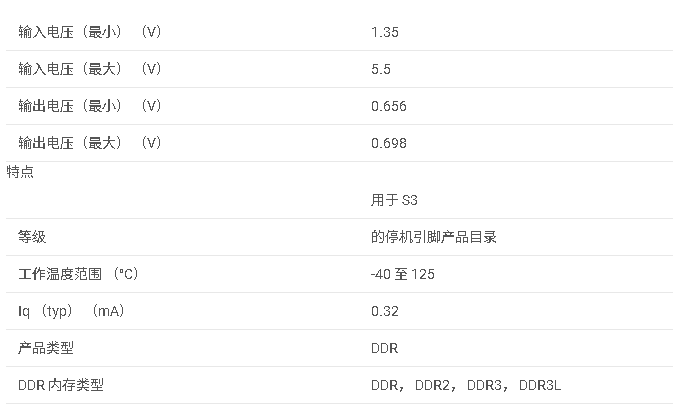

LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 规范 DDR-SDRAM 终止。该器件还支持 DDR2、DDR3 和 DDR3L VTT 总线端接,带 V~DDQ~最小为 1.35V

2025-04-26 15:02:50 746

746

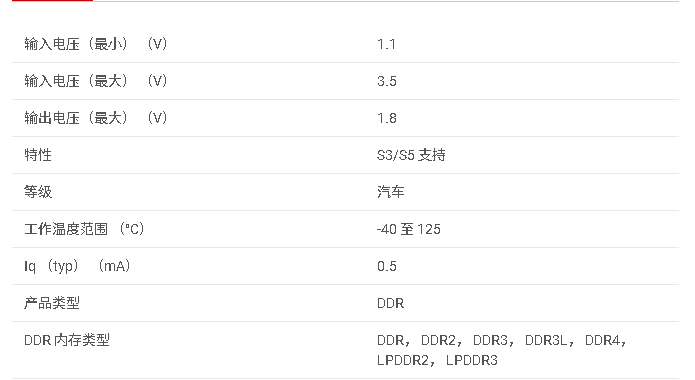

只需要最小输出 电容为 20 μF。TPS51200-EP 支持遥感功能和所有功率要求 用于 DDR、DDR2、DDR3、低功耗 DDR3 和 DDR4 VTT 总线终端。

2025-04-26 10:26:35 1335

1335

的最小输出电容。该器件支持远程感应功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

2025-04-25 10:07:15 1053

1053

位流验证,对于芯片研发是一个非常重要的测试手段,对于纯软件开发人员,最难理解的就是位流验证。在FPGA芯片研发中,位流验证是在做什么,在哪些阶段需要做位流验证,如何做?都是问题。

2025-04-25 09:42:51 2202

2202

推动电脑迈入新一轮升级周期。相比服役多年的DDR4,DDR5不仅带来更快的速度,还能提升游戏帧率、加快视频渲染效率,甚至延长设备续航时间。(主板上的内存插槽位置)问

2025-04-18 10:34:13 71

71

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

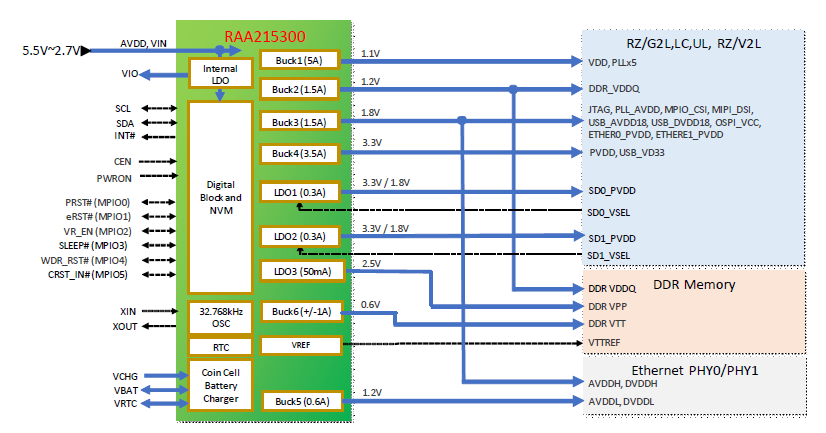

RAA215300 是一款高性能、低成本的 9 通道 PMIC,专为 32 位和 64 位 MCU 和 MPU 应用而设计。 该 PMIC 支持DDR3、DDR3L、DDR4 和 LPDDR4 内存

2025-04-09 15:31:25 657

657

的DAC; ● 支持外部时钟输入1路, 外触发,外同步各1路; ● PL 1组64 bit 2400M DDR4,支持PL部分高速存储和处理。 单组4GB字节容量,PL部分8GB字节容量。 ● 支

2025-04-08 10:34:02 1023

1023

注意:DDR PMU 固件 vision-0x1001 (vA-2019.04)

注意:DDR4 UDIMM,带 2 位 64 位总线 (x8)

注意:32 GB DDR4,64 位,CL=22,ECC

2025-04-04 08:17:54

RT1176 与 DDR SDRAM 兼容吗?

2025-04-04 06:09:26

具有闪存 以及一个串行接口,以支持可配置性、监控和管理。

支持多种电压识别 (VID) 模式,包括 4 位并行 接口、一个 6 位接口和一个 8 位串行接口。

2025-03-25 17:18:55 785

785

,UCD9244 具有闪存和串行接口,以支持可配置性、监控和管理。

支持多种电压识别 (VID) 模式,包括 4 位并行接口、6 位接口和 8 位串行接口。

2025-03-25 15:20:12 726

726

3, DDR3L, DDR4和LPDDR3, LPDDR4协议,数据传输速率最高可达2667Mbps,并支持X16/X32/X64等多种数据位宽应用。

2025-03-21 16:20:03 984

984 DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPDDR2),并通过精心设计的架构来优化内存访问效率。

2025-03-05 13:47:40 3573

3573

前言 SDRAM控制器里面包含5个主要的模块,分别是PLL模块,异步FIFO 写模块,异步FIFO读模块,SDRAM接口控制模块,SDRAM指令执行模块。 其中异步FIFO模块解读

2025-03-04 10:49:01 2301

2301

为了加深读者对 FPGA 端控制架构的印象,在数据读取的控制部分,首先我们可以将SDRAM 想作是一个自来水厂,清水得先送至用户楼上的水塔中存放,在家里转开水龙头要用水时,才能及时供应,相同

2025-02-26 15:27:09 1813

1813

电子发烧友网综合报道,日前,日媒报道由于DRAM内存芯片价格持续下滑,全球三大原厂三星、SK海力士和美光计划在2025年停产DDR4内存芯片。 数据显示,2025年1月,DDR4 8Gb颗粒

2025-02-21 00:10:00 2806

2806 ,DDR5内存已成为市场主流,并逐步取代DDR4内存。值得注意的是,消费级平台已不再支持DDR4,这使得DDR4内存开始加速向DDR3目前所占据的利基市场转移。 若三大内存原厂真的决定停产DDR3和DDR4,这无疑将对内存市场产生深远影响。一方面,这将促使现有DDR3和DDR4内存库存

2025-02-19 11:11:51 3465

3465

在查阅了论坛中的相关帖子后,发现为了达到该DMD允许的最大投影帧率,需要:

在硬件上需要使用Xilinx Platform cable将FPGA代码烧录到该EVM的APPSFPGA中,同时需要

2025-02-19 07:04:51

UltraScale+ XCVU13P(16nm工艺)FPGA 芯片,但从原先最大支持 16G DDR4 SODIMM 内存条插槽升级为最大支持 32G ,并且支持多达 4 个 FMC+ 扩展接口,接入

2025-02-13 17:56:44 1020

1020

;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM内存模块,专为满足现代计算需求而设计。该产品以其高带宽和低功耗的特性,广泛应用于个人电脑、服务器和嵌入式系统中,成为市场上备

2025-02-10 20:10:39

如需了解价格货期等具体信息,欢迎在首页找到联系方式链接我。不要留言,留言会被吞,收不到留言。 8GB DDR4 ECC UDIMM 产品概述 8GB DDR4 ECC UDIMM

2025-02-10 20:07:47

如需了解价格货期等具体信息,欢迎在首页找到联系方式链接我。不要留言,留言会被吞,收不到留言。 16GB DDR4 ECC UDIMM 产品概述 16GB DDR4 ECC

2025-02-10 20:05:15

M471A2G43AB2-CWE 是一款高性能的 DDR4 SO-DIMM 内存模块,具有 16GB 的容量,专为满足现代移动计算需求而设计。这款内存条采用了 Samsung 的先进技术,适用于各种

2025-02-10 07:49:49

M471A1G44CB0-CWE 是一款高性能的 DDR4 SO-DIMM 内存模块,具有 8GB 的容量,专为满足现代移动计算需求而设计。这款内存条采用了 Samsung 的先进技术,适用于各类

2025-02-10 07:48:41

更高的带宽和更低的功耗,适用于各种笔记本电脑和小型计算设备。产品技术资料型号:M425R1GB4PB0-CWM内存类型:DDR5 SDRAM容量:8GB工作频率:5

2025-02-10 07:47:57

执行信号的解串操作(串转并),并解码出视频流数据,随后通过VDMA IP缓存至DDR中,利用Xilinx官方的IP对视频流数据进行重新编码

2025-01-24 10:27:05 979

979

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

2025-01-16 11:02:01 1655

1655

AMD Versal 自适应 SoC 器件上 DDR4 硬核控制器 DDRMC 跑仿真时,按照 IP 的默认设置,在 IP wizard 中使能了“Internal Responder”,就可以

2025-01-10 13:33:34 1481

1481

硬件:

一Xilinx XC7A100T FPGA开发板

二12V电源适配器

三下载器

四 win10笔记本

软件:

一Vivado (指导手册有详细的安装下载流程)

二官方按键示例工程

按键示例

2025-01-09 16:08:51

电子发烧友App

电子发烧友App

评论