来源:至芯

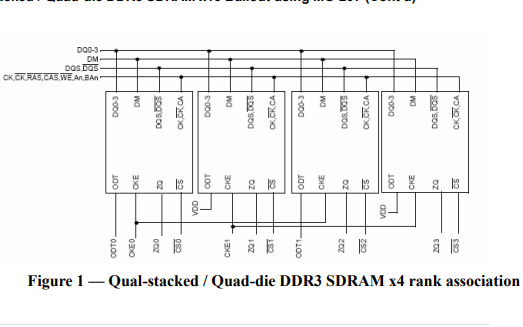

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。DDR SDRAM是在SDRAM技术的基础上发展改进而来的;与SDRAM相比,DDR SDRAM的最大特点是双沿触发,即在时钟的上升沿和下降沿都能进行数据采集和发送,同样的工作时钟,DDR SDRAM的读写速度比传统的SDRAM快一倍。本次实验使用的DDR3芯片是MT41J256MM16,芯片的bank位宽为,行位宽为,列位宽为,所以它的地址大小等于,数据位宽为16bit,所以容量大小为256Mb*16bit,也就是512MB。DDR3是半双工,读写不能同时发生,掉电数据丢失。

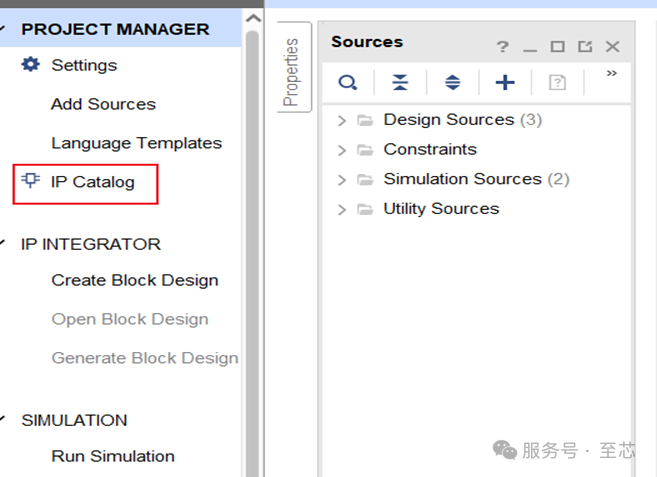

1)点击“IP Catalog”按钮。

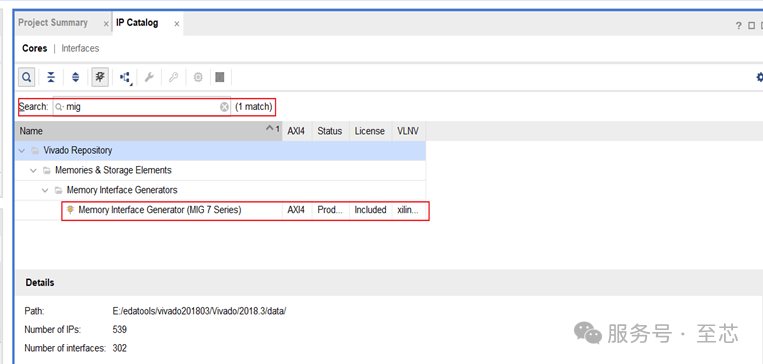

2)在搜索栏中输入MIG,此时出现MIG IP核,直接双击打开。

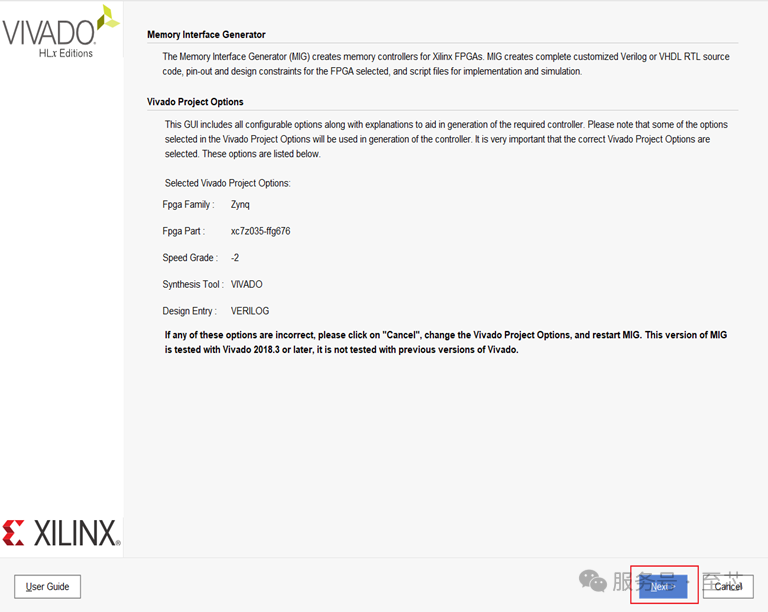

3)确认工程的信息,主要是芯片信息和编译环境的信息,如果没有问题,直接点击“Next”。

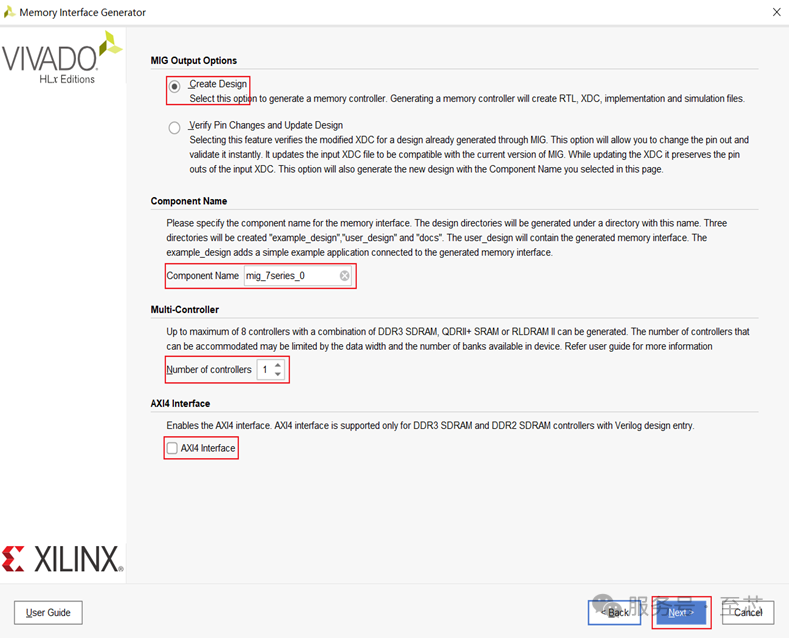

4)选择“Create Design”,在“Component Name”一栏设置该IP核的名称,这里取默认软件的名称,再往下选择控制器数量,默认为“1”即可。最后是AXI4接口,本工程使用的是Native接口,不勾选。配置完点击“Next”。

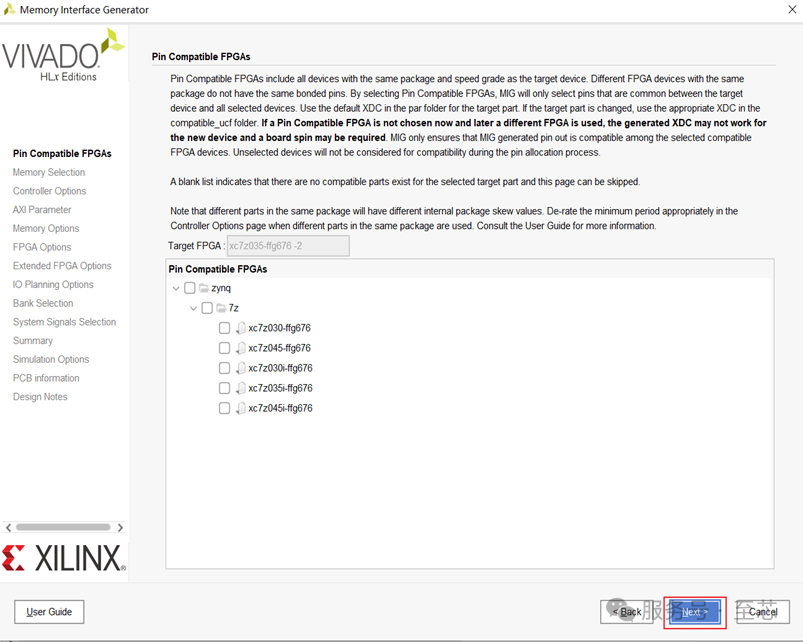

5)这一页主要是让用户选择可以兼容的芯片,本工程默认不勾选,即不需要兼容其他的FPGA芯片。配置完成点击“Next”。

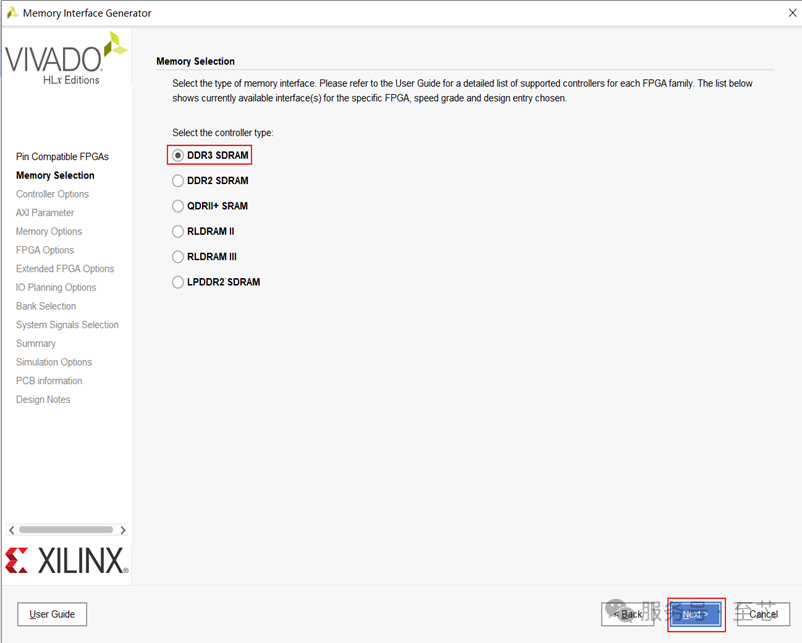

6)这一页选择第一个选项“DDR3 SDRAM”,因为本实验用的就是DDR3芯片。配置完成点击“Next”。

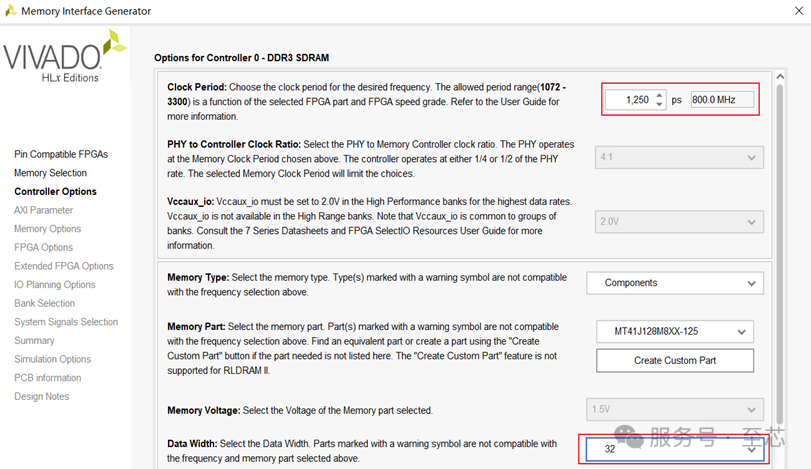

7)配置MIG IP核。

Clock Period:DDR3芯片运行时钟周期,这个参数的范围和FPGA的芯片选型以及具体类型的速度等级有关。本实验选择1250ps,对应800MHz。注意这个时钟是由MIG IP核产生,并输出给DDR3物理芯片使用,它关系到DDR3芯片具体的运行带宽。本次实验的开发板板载了2颗DDR3芯片,数据位宽为32位,因为是双沿触发,这里带宽达到了800*32*2=51.2Gb/s。

PHY to ControllerClock Ratio:DDR3物理芯片运行时钟和MIG IP核的用户端(FPGA)的时钟之比,一般有4:1和2:1两个选项,本次实验选4:1。由于DDR芯片的运行时钟是800MHz,因此MIG IP核的用户时钟就是200MHz。当DDR3时钟选择了350MHz到最高的400MHz,比例默认只为4:1,低于350MHz才有4:1和2:1两个选项。

VCCAUX_IO:这是FPGA高性能bank(High Performancebank)的供电电压。它的设置取决于MIG控制器运行的周期/频率。当用户让控制器工作在最快频率的时候,系统会默认为2.0V。

Memory Type:DDR3存储器类型选择。本实验选择Component。

Memory Part:DDR3芯片的具体型号。本实验选择MT41J256M8XX-125,这个型号其实和实际硬件原理图上的型号是不同的,这个没关系,只要用户的DDR3芯片容量和位宽一致大部分是可以兼容的,其他的型号也是可以的。

Memory Voltage:是DDR3芯片的电压选择,本实验选1.5V。

Data Width:数据位宽选择,根据硬件原理图选择,选择32,因为是2片DDR拼接而成的。

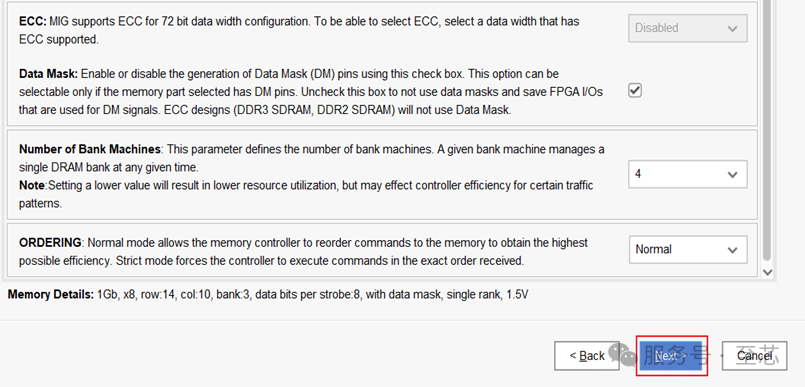

ECC:ECC校验使能,数据位宽为72位的时候才能使用,本实验不使用它。

Data Mask:数据屏蔽管脚使能。

Number of BankMachine:Bank Machine的数量是用来对具体的每个或几个来单独控制的,选择多了控制效率就会高,相应的占用的资源也多,本实验选择4个,平均一个Bank Machine控制两个Bank。

ORDERING:该信号用来决定MIG控制器是否可以对它的指令进行重新排序,选择Normal则允许,Strict则禁止。本实验选择Normal,从而获得更高效率。

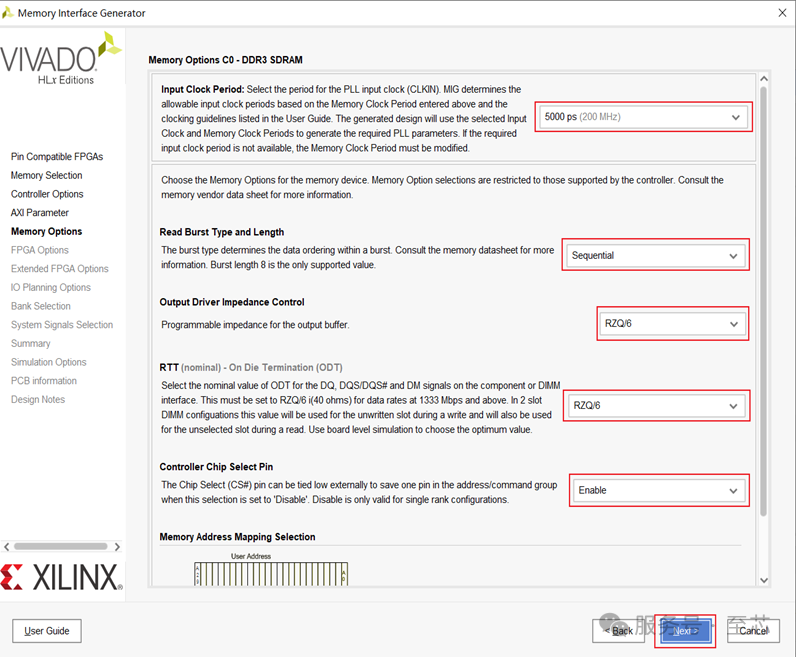

点击“Next”,如下图所示:

Input ClockPeriod:MIG IP核的系统输入时钟,该输入时钟是由FPGA内部产生的,本次实验选择的时钟频率为200MHz(5000ps)。

Read Burst Typeand Length:突发类型选择,突发类型有顺序突发和交叉突发两种,本实验选择顺序突发(Sequential),其突发长度固定为8。

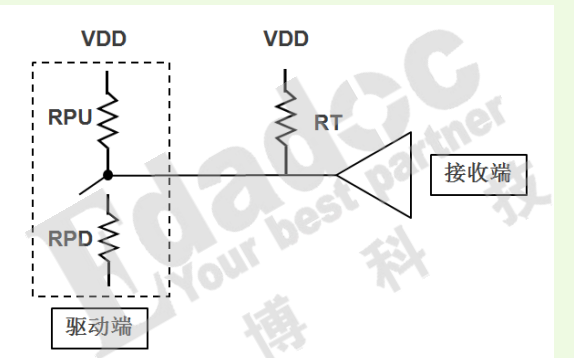

Output DriverImpdance Control:输出阻抗控制。本实验选择RZQ/7。

RTT:终结电阻,可进行动态控制。本实验选择RZQ/4。

Controller ChipSelect Pin:片选管脚引出使能。本实验选择enable,表示把片选信号cs引出来,由外部控制。

BANK_ROW_COLUMN:寻址方式选择。本实验选择第二种,即BANK-ROW-COLUMN的形式,这是一种最常规的DDR3寻址方式,即要指定某个地址,先指定bank,再指定行,最后指定列,这样就确定了具体地址。一般来说这样寻址方式有利于降低功耗,但是读写性能上不如“ROW_BANK_COLUMN”。配置完成点击“Next”。

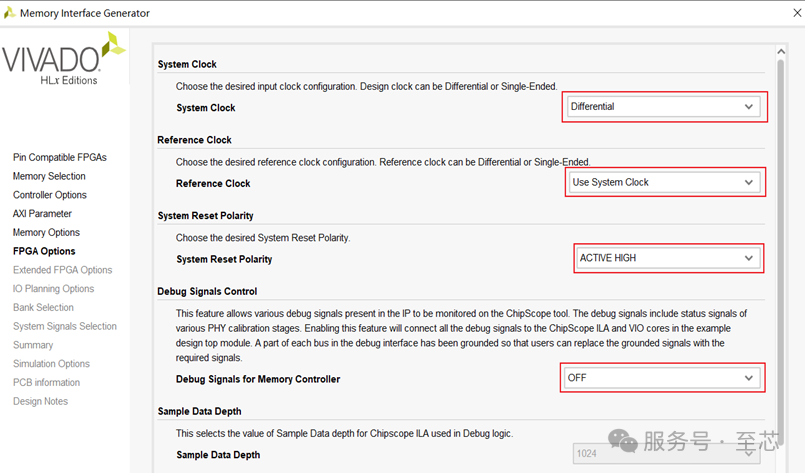

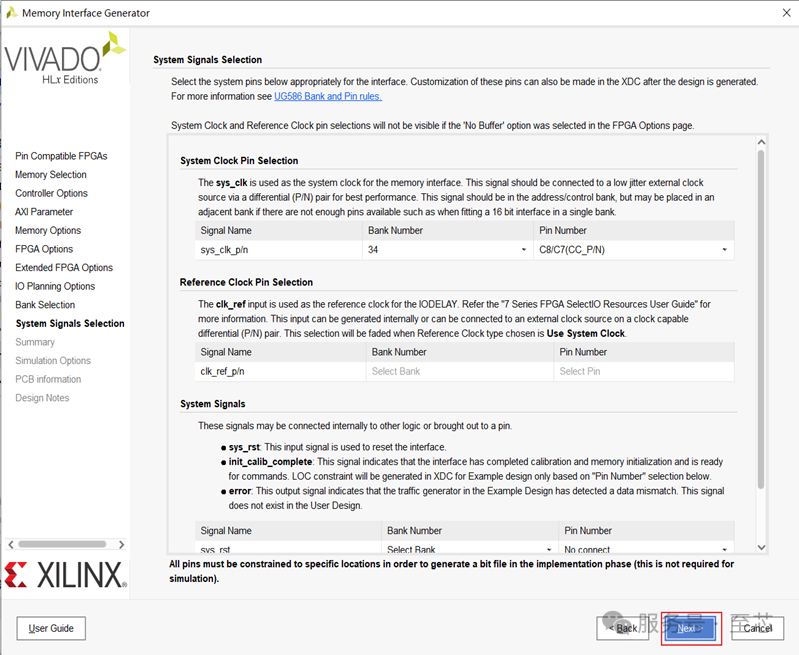

System Clock:MIG IP核输入时钟。本实验选择“Differential”,由外部晶振提供。

Referance Clock:MIG IP核参考时钟。选择“Use SystemClock”这个选项,这时候的MIG IP系统时钟同时作为了参考时钟,MIG IP核参考时钟要求是200MHz,而MIG IP核的系统时钟刚好也使用了200MHz的系统时钟。

System ResetPolarity:复位有效电平选择。本实验选择“ACTIVE HIGH”高电平有效。

Debug SignalsControl:该选项用于控制MIG IP核是否把一些调试信号引出来,它会自动添加到ILA,这些信号包括一些DDR3芯片的校准状态信息。本实验选择“OFF”,不需要让MIG IP核产生各种调试信号。

Sample DataDepth:采样深度选择。当“Debug Signals Control”选择“OFF”时,所有采样深度是不可选的。

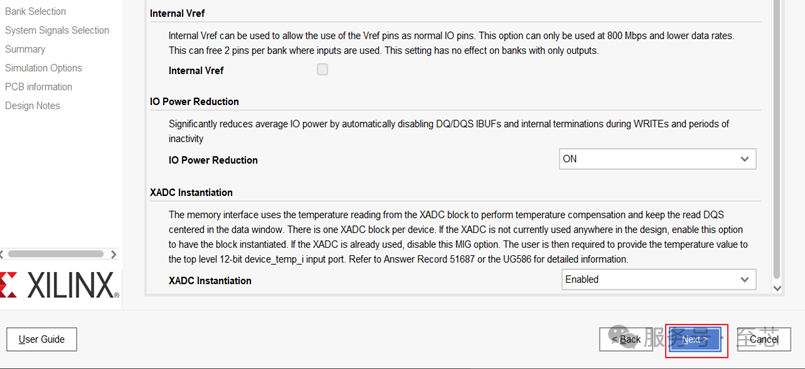

Internal Vref:内部参考管脚,表示将某些参考管脚当成普通的输入管脚来用。由于开发板的IO资源较为紧张,因此这里需要选择“ON”,把参考管脚当做普通的输入管脚来用。

IO PowerReduction:IO管脚节省功耗设置。本实验选择“ON”,即开启。

XADCInstantiation:XADC模块例化。使用MIG IP核运行的时候需要进行温度补偿,可以直接选择XADC模块的温度数据引到MIG IP核来使用,否则需要额外提供温度数据,所以本实验选择“Enable”。

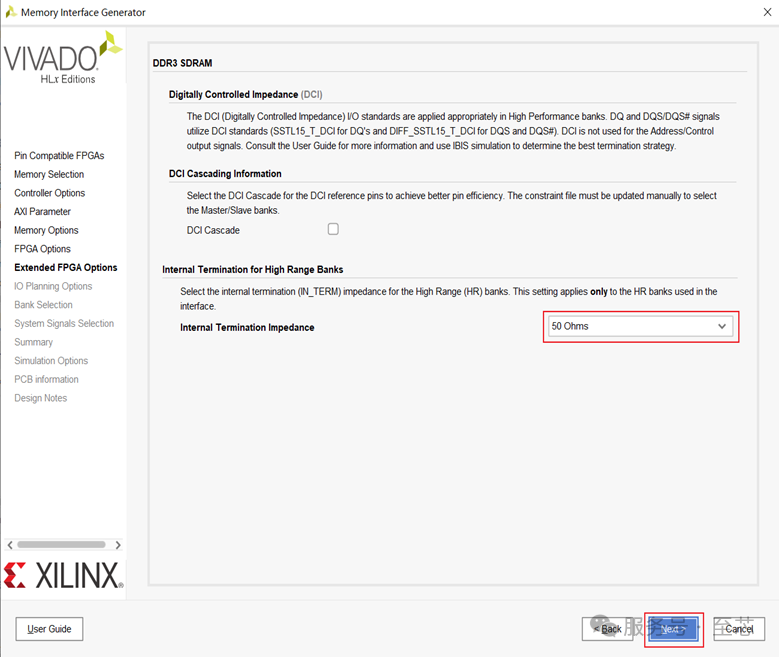

点击“Next”按钮,界面如下图所示:

上图界面是内部高性能bank端接匹配阻抗的设置,这里不去改它,默认50欧姆即可。接下来点击“Next”,界面如下图所示:

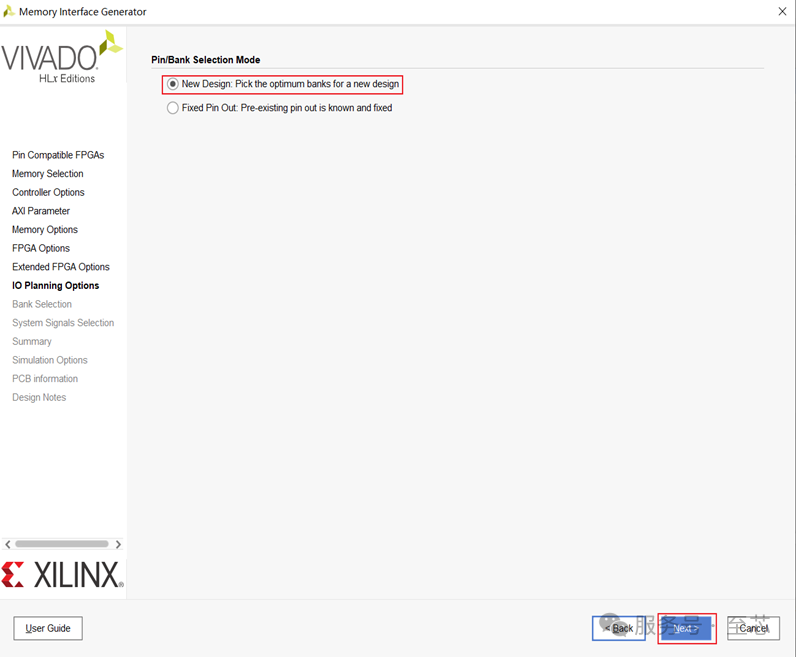

选择第一种,点击“Next”,如下图所示:

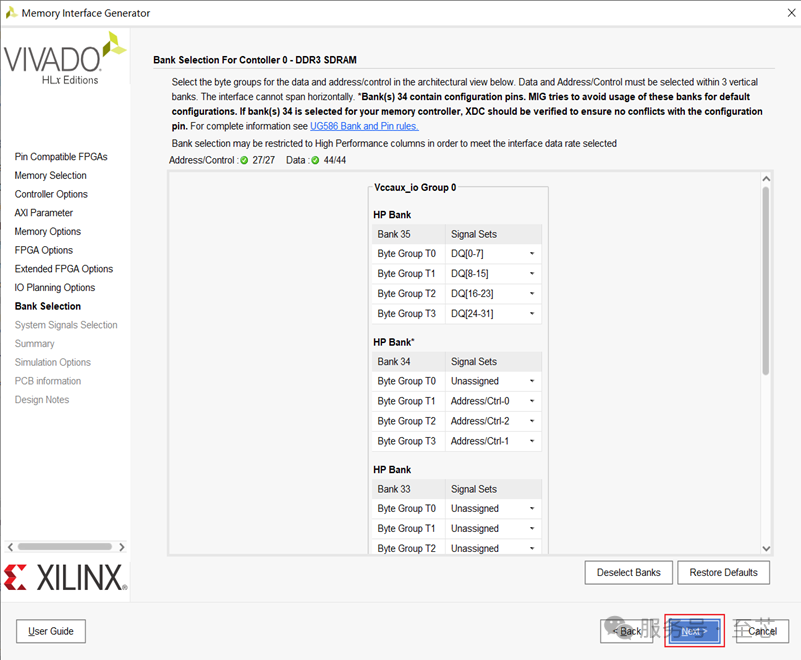

点击“Next”,如下图所示:

点击“Next”,如下图所示:

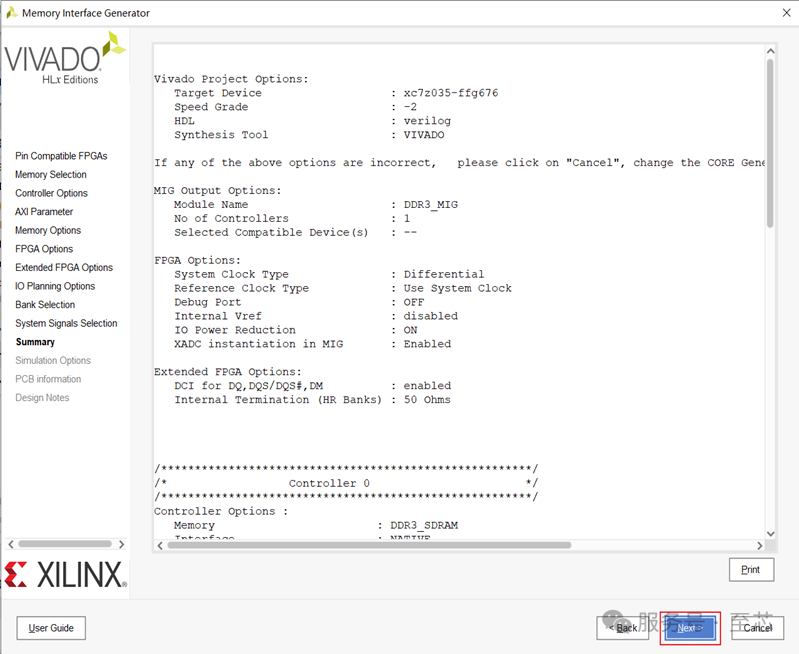

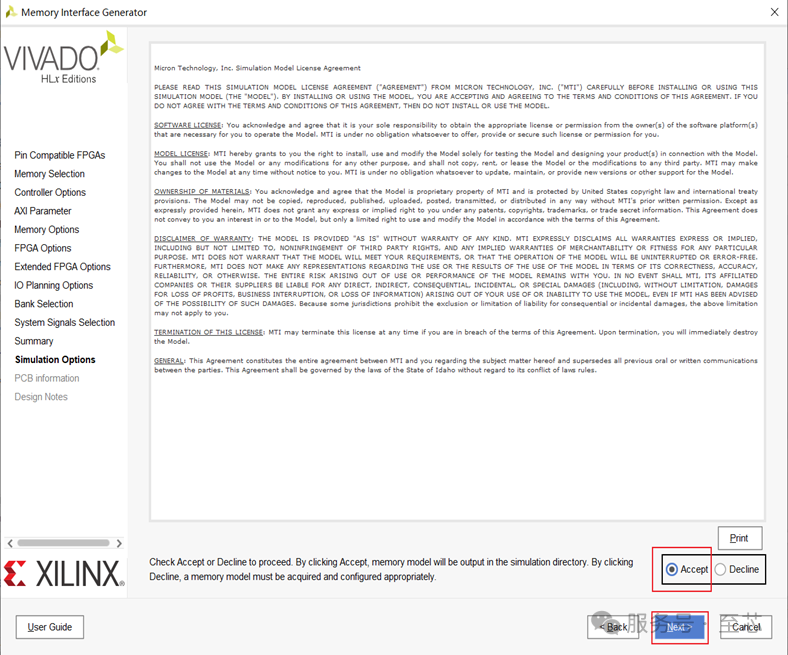

选择“Accept”,点击“Next”,如下图所示:

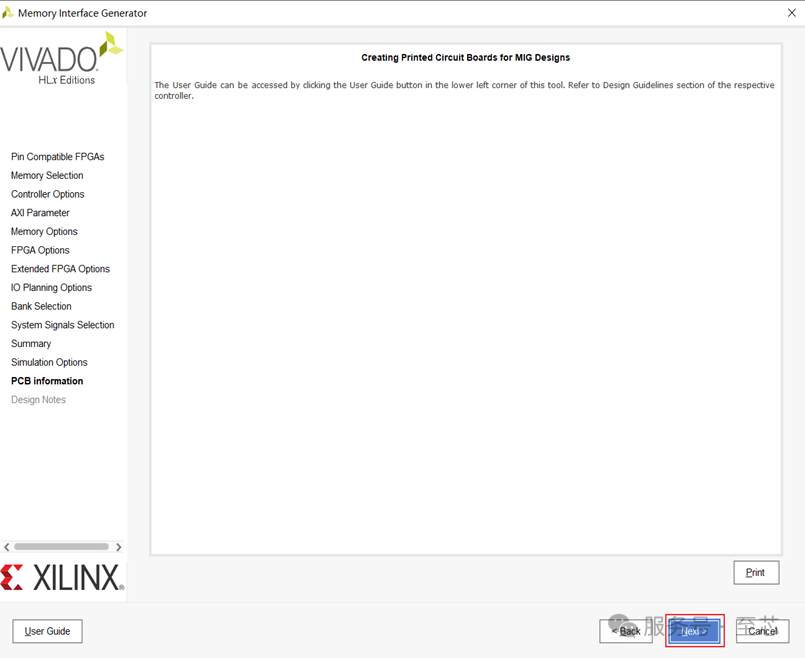

点击“Next”,如下图所示:

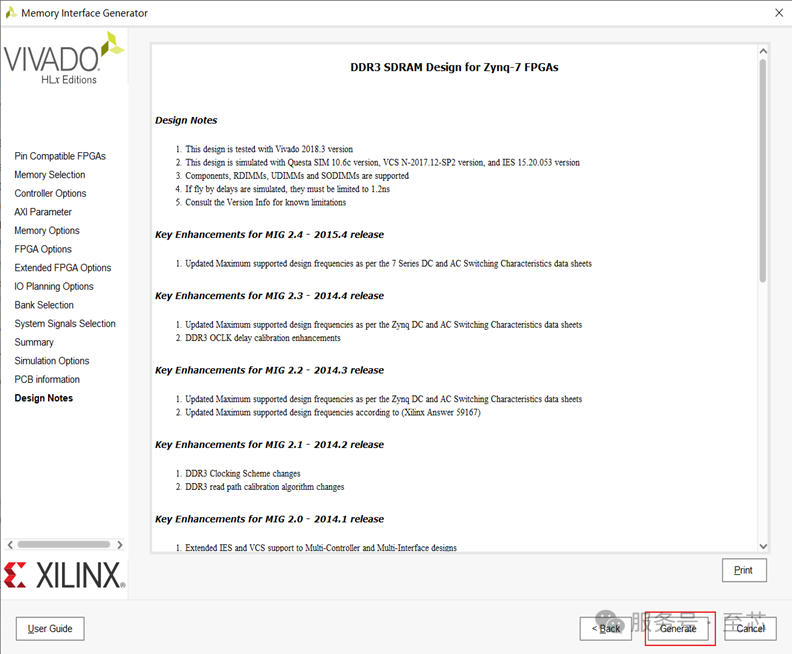

点击“Generator”,如下图所示:

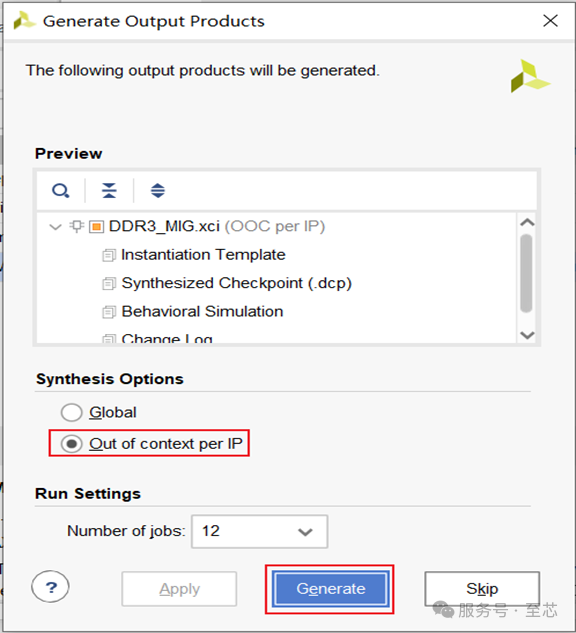

选择“OOC”模式,点击“Next”,如下图所示:

-

芯片

+关注

关注

463文章

54429浏览量

469367 -

SDRAM

+关注

关注

7文章

458浏览量

57848 -

DDR3

+关注

关注

2文章

290浏览量

44277 -

DDR2

+关注

关注

1文章

115浏览量

42444

原文标题:DDR3详细配置步骤

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

DDR3 SDRAM控制器IP核的写命令和写数据间关系讲解

华邦将持续扩产 DDR3 SDRAM

665x的DDR3配置

ddr3 sdram controller with uniphy 17.1 无法例化

基于Stratix III的DDR3 SDRAM控制器设计

检验DDR, DDR2 和DDR3 SDRAM命令和协议

SDRAM,DDR3,DDR2,DDR4,DDR1的区别对比及其特点分析

基于FPGA的DDR3 SDRAM控制器用户接口设计

DRAM、SDRAM及DDR SDRAM之间的概念详解

DDR3和DDR4的设计与仿真学习教程免费下载

DDR3 SDRAM的JESD79-3D标准免费下载

DDR3 SDRAM配置教程

DDR3 SDRAM配置教程

评论