RZ/G2L微处理器配备Cortex-A55(1.2GHz)CPU、16位DDR3L/DDR4接口、带Arm Mali-G31的3D图形加速引擎以及视频编解码器(H.264)。此外,这款微处理器还配备有大量接口,如摄像头输入、显示输出、USB2.0和千兆以太网,因此特别适用于入门级工业人机界面(HMI)和具有视频功能的嵌入式设备等应用。

目录

RZ/G2L的DDR配置

1. RZ/G2L对DDR的支持

1.1 RZ/G2L支持的DDR类型

1.2 RZ/G2L DDR控制器的相关硬件特性

1.3 RZ/G2L DDR控制器ECC功能介绍

2. DDR3和DDR4的背景技术介绍

2.1 DDR3

2.2 DDR4

2.3 DDR3L

2.4 DDR3L和DDR4的技术特点和区别

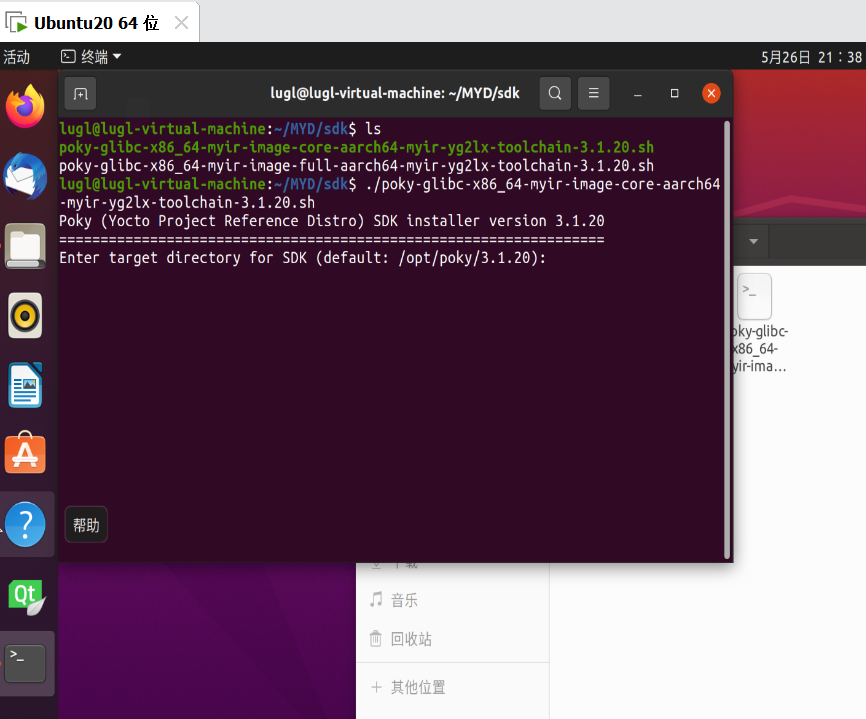

3. DDR配置工具使用流程(以RZ/G2L为例)

3.1 配置工具介绍

3.2 使用前准备

3.3 具体使用步骤

3.3.1 01_Condition与02_Connection表的选择

3.3.2 03_Topology表的选择

3.3.3 05_CA_Remap表操作

3.3.4 GenParam表操作

3.3.5 生成配置文件

3.4 使用技巧与注意事项

4. 总结

1RZ/G2L对DDR的支持

1.1RZ/G2L支持的DDR类型

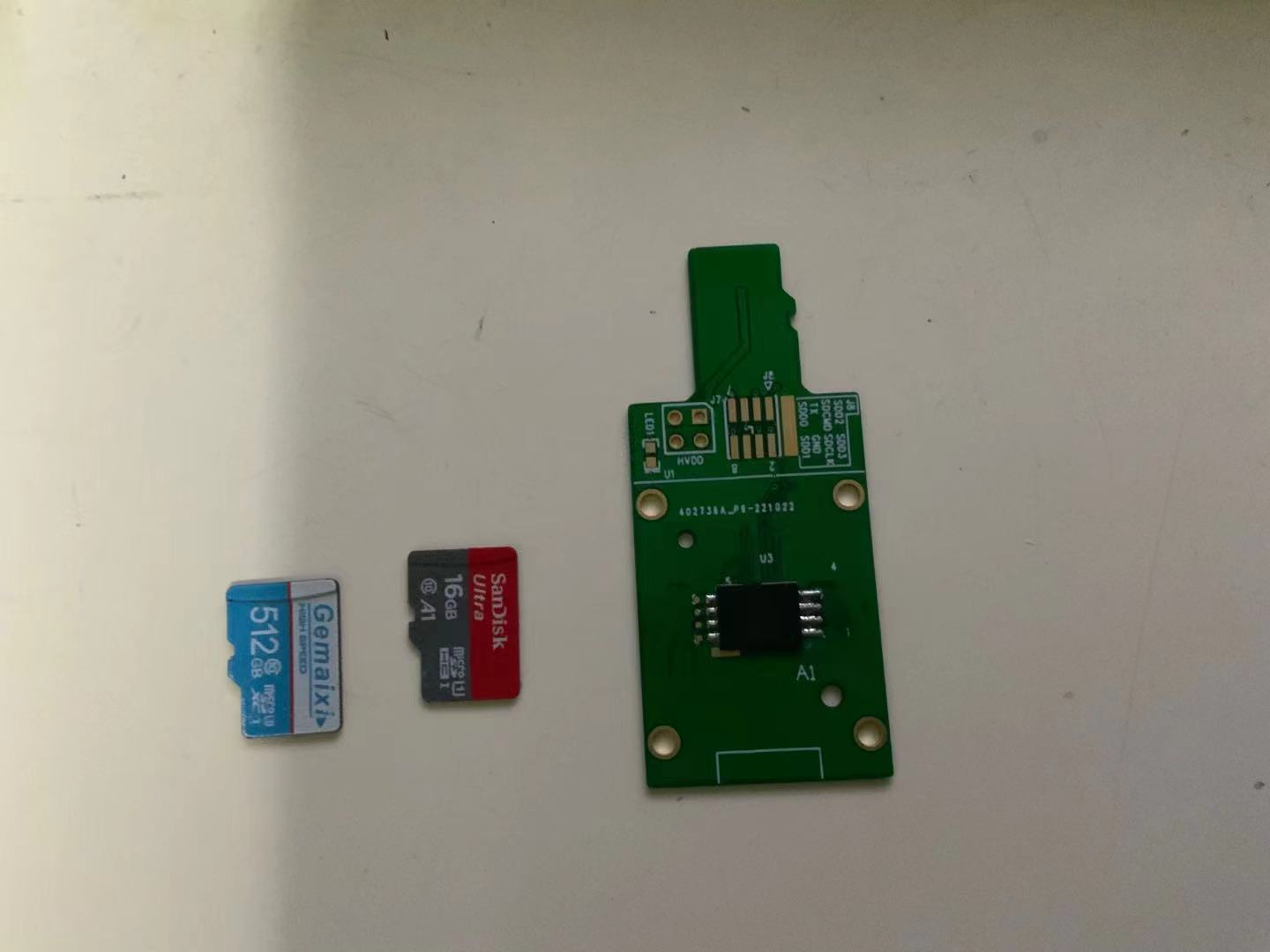

RZ/G2L-LC-UL型号的MPU处理器在内存适配这块还是比较灵活的,他们的DRAM IF/MC/PYH模块是一样的,配置工具因此是通用的,支持DDR3L和DDR4两种类型的DDR内存。

DDR3L是DDR3的低电压版本,工作电压为1.35V,在RZ/G2L中,其数据传输速率范围为800-1333Mbps(对应400-666MHz)。较低的工作电压使其在功耗控制上更具优势,适用于对功耗敏感的嵌入式设备场景,如便携式工业控制终端、移动数据采集设备等。

DDR4则是新一代的内存技术,工作电压进一步降低至1.2V,在RZ/G2L上支持的传输速率为1333-1600Mbps(666-800MHz)。更高的传输速率和更低的功耗,使其在处理复杂计算任务和大数据量传输时表现更为出色,适合于对性能要求较高的应用,如边缘计算设备、高端工业自动化控制系统等。

此外,两种内存均支持16位的数据,可根据实际需求选择全宽(16bits)或半宽(8bits)数据宽度模式,同时支持单Rank(Rank:1)或双Rank(Rank:2)的配置,满足不同内存容量和性能的需求。

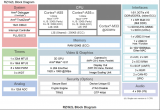

1.2RZ/G2L DDR控制器的相关硬件特性

RZ/G2L的DDR相关硬件架构由多个关键模块协同工作,共同保障内存数据的高效传输与稳定运行。

内存控制器(MC)采用全流水线设计,为命令、读写数据提供了高效的接口通道。这种设计使得内存访问指令能够以流水线的方式快速处理,极大地提高了内存数据的吞吐量。同时,它具备先进的bank look-ahead特性,能够提前预测内存访问模式,优化数据读取和写入顺序,进一步提升内存访问效率。

通过可编程寄存器接口,开发者可以灵活地控制内存参数和协议,包括自动预充电功能,该功能能够在内存操作完成后自动对存储单元进行预充电,为下一次操作做好准备,减少等待时间。在控制器复位时,内存能够实现全面初始化,确保系统启动时内存状态的一致性和准确性。

物理层(PHY)集成了多种重要功能。写均衡(Write Leveling)功能能够调整数据写入时的时钟与数据信号的相位关系,确保数据准确写入内存单元;位校准(Bit Leveling)用于校准数据信号(DQS)与数据(DQ/DM)之间的相位差,保证数据传输的准确性;Vref训练(Read and Write)则通过自动调整参考电压,优化数据读写时的信号质量;自校准逻辑(Self Calibratio Logic)能够调整读取数据与内部时钟的相位关系,确保数据读取的准确性;命令/地址交织(Command/Address Swizzling)功能通过优化地址映射,提高内存访问效率,增强系统整体性能。

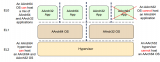

1.3RZ/G2L DDR控制器ECC功能介绍

RZ/G2L的ECC(纠错码)功能是保障数据可靠性的重要机制。在数据存储和传输过程中,由于各种因素的干扰,数据可能会出现错误,ECC功能能够有效地检测和纠正这些错误。

对于单比特错误,ECC可以自动检测并进行纠正,确保数据的准确性。在双比特错误发生时,ECC能够及时报告错误信息,虽然无法直接纠正,但可以让系统采取相应的措施,如重新读取数据或进行错误处理,避免错误数据对系统运行产生严重影响。

此外,ECC功能还支持可编程的ECC存储移除,开发者可以根据实际应用场景和需求,灵活地选择启用或关闭ECC功能,在对数据可靠性要求不高且希望降低系统资源占用的情况下,可以关闭ECC功能,从而节省内存空间和计算资源。

结语

敬请期待

精彩尚未结束,下一期我们将深入探讨——DDR3和DDR4的背景技术介绍,敬请期待!

-

DDR

+关注

关注

11文章

748浏览量

68573 -

瑞萨

+关注

关注

36文章

22434浏览量

89839 -

微处理器

+关注

关注

11文章

2416浏览量

85385 -

MPU

+关注

关注

0文章

442浏览量

51060

发布评论请先 登录

基于瑞萨64位MPU RZ/G2L的uboot串口多波特率支持介绍

瑞萨MCU方案:瑞萨RZ/G2L Bootloader单独编译方法详解

瑞萨RZ/G2L MPU的DDR配置(1)

瑞萨RZ/G2L MPU的DDR配置(1)

评论