AMD Versal 自适应 SoC器件上 DDR4 硬核控制器 DDRMC 跑仿真时,按照 IP 的默认设置,在 IP wizard 中使能了“Internal Responder”,就可以直接进行仿真了。这种方法非常的简单,但是,DDR4 这一侧的模型包含在内部,接口信号隐藏了,所以用户无法直接观察到 DDR4 管脚上的波形。

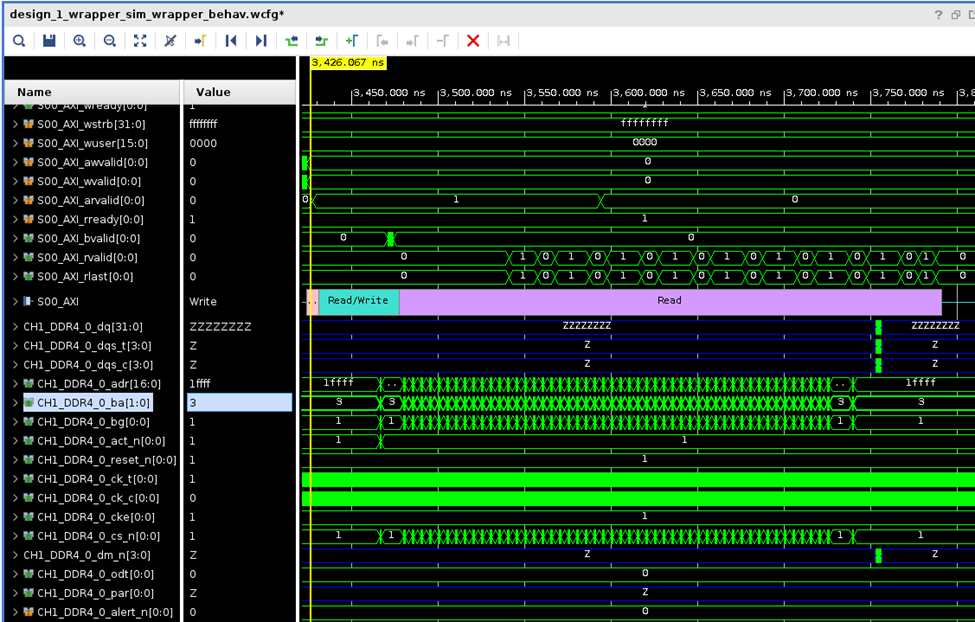

如果需要看到 DDR4 管脚这一侧的信号,则需要通过修改设计,把 Memory 厂商提供的仿真模型外接到 DDRMC 上,再去进行仿真。

具体操作的流程如下:

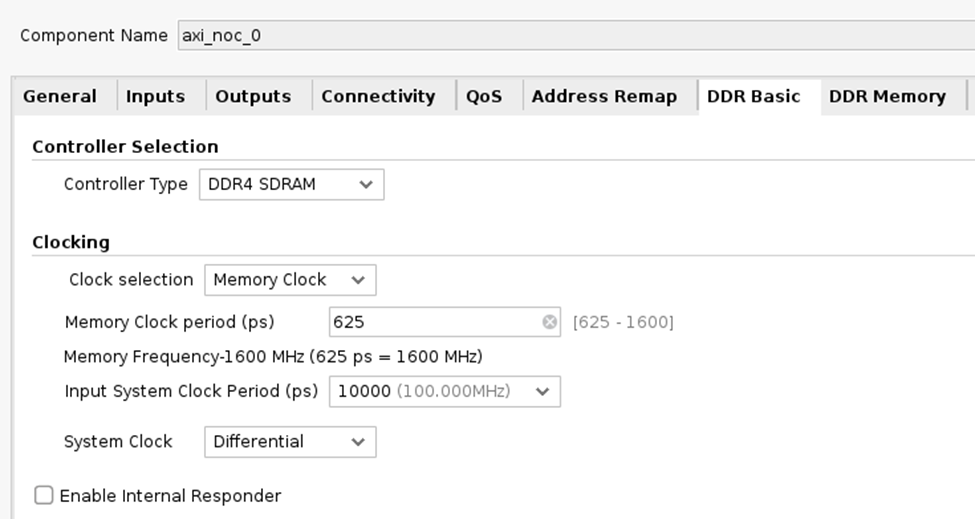

1. AXI NOC IP中去掉 “Enable Internal responder”的勾选。

2. 从 Micron 官网上下载最新版本的 DDR4 仿真模型:

https://www.micron.cn/

3. 在 Testbench 中例化 Micron DDR4 仿真模型,并设置 Memory 数据宽度,容量等相关参数。

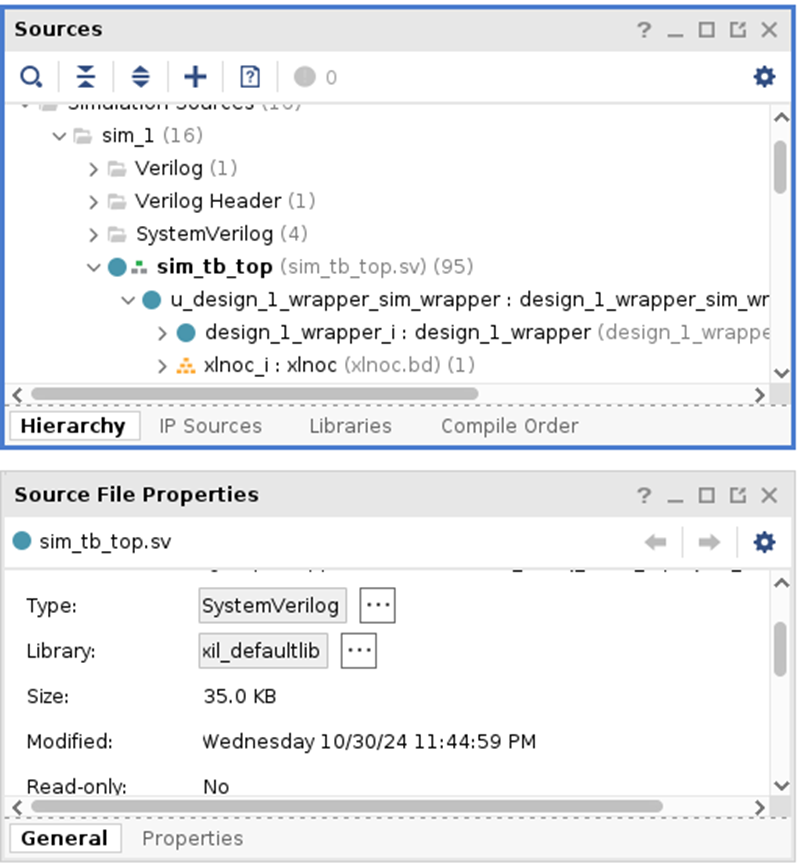

4. 在 Source File Properties 窗口中选择 General -> Type。修改 design_1_wrapper.v 的文件类型,从Verilog改成 SystemVerilog。

5. 在 design_1_wrapper.v 文件中添加容量配置,如下:

import arch_package::*;

parameter UTYPE_density CONFIGURED_DENSITY = _4G; //BASED ON DRAM(COMPONENT) DENSITY

6. 确认命令地址信号的位宽和模型的正确连接。注意,当选项 COMMAND ADDRESS MIRRORING 打开的时候,每个 Rank 的 Bank Group 和 Bank 地址线都要单独生成。

7. 通过 Tcl 使能模式寄存器的初始化流程:

set_property CONFIG.MC_XLNX_RESPONDER "false" [get_ips design_1_axi_noc_0_0]

8. 点击“Run Simulation”或者运行脚本 launch_simulation 开始仿真。

-

amd

+关注

关注

25文章

5708浏览量

140436 -

控制器

+关注

关注

114文章

17886浏览量

195208 -

soc

+关注

关注

40文章

4635浏览量

230239 -

仿真

+关注

关注

55文章

4539浏览量

138688 -

Versal

+关注

关注

1文章

176浏览量

8545

原文标题:开发者分享|AMD Versal™ 自适应 SoC DDRMC 如何使用 Micron 仿真模型进行仿真

文章出处:【微信号:gh_2d1c7e2d540e,微信公众号:XILINX开发者社区】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

【ALINX 技术分享】AMD Versal AI Edge 自适应计算加速平台之 Versal 介绍(2)

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

AMD Versal自适应SoC内置自校准的工作原理

基于MATLAB的时变系统自适应控制的仿真

AMD率先推出符合DisplayPort™ 2.1 8K视频标准的FPGA和自适应SoC

AMD发布第二代Versal自适应SoC,AI嵌入式领域再提速

AMD Versal自适应SoC CPM5 QDMA的Tandem PCIe启动流程介绍

AMD Versal自适应SoC GTM如何用XSIM仿真和观察PAM4信号

AMD Versal自适应SoC器件Advanced Flow概览(上)

AMD Versal自适应SoC器件Advanced Flow概览(下)

AMD Versal自适应SoC DDRMC如何使用Micron仿真模型进行仿真

AMD Versal自适应SoC DDRMC如何使用Micron仿真模型进行仿真

评论