DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPDDR2),并通过精心设计的架构来优化内存访问效率。

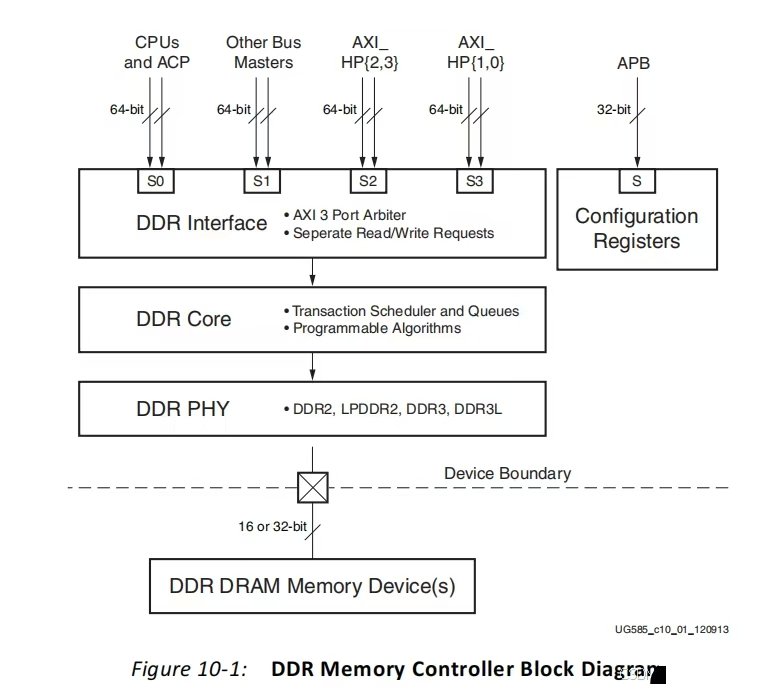

DDR内存控制器架构

AXI内存端口接口(DDRI):该部分负责处理与多个AXI主设备之间的通信。通过四个64位的同步AXI接口,DDRI能够同时服务多个AXI主设备,每个接口都配备了专用的交易FIFO,以确保数据的高效传输和缓存。

核心控制器与事务调度器(DDRC):DDRC是DDR内存控制器的核心,它包含两个32条目的内容可寻址存储器(CAMs),用于执行DDR数据服务调度,以最大化DDR内存的效率。此外,它还提供了低延迟的飞线通道(fly-by channel),允许直接访问DDR内存而无需经过CAM,从而进一步减少延迟。

数字PHY控制器(DDRP):DDRP负责处理来自控制器的读写请求,并将这些请求转换为符合目标DDR内存时序约束的特定信号。这些信号通过数字PHY连接到DDR引脚,最终与DDR设备通过PCB信号迹线直接相连。

访问机制

AXI端口分配:系统通过DDRI的四个64位AXI内存端口访问DDR内存。其中,一个端口专用于CPU和ACP的L2缓存,两个端口专用于AXI_HP接口,第四个端口则由AXI互连上的所有其他主设备共享。

仲裁机制:DDRI负责仲裁来自八个端口(四个读端口和四个写端口)的请求。仲裁器基于请求的等待时间、请求的紧急程度以及请求是否与前一个请求在同一页面内等因素来选择请求,并将其传递给DDR控制器和事务调度器(DDRC)。

读写流程:读写请求通过DDRC的单一接口传递。读请求包括一个标签字段,该字段与从DDR返回的数据一起返回,以便于数据的匹配和确认。DDR控制器PHY(DDRP)则负责驱动DDR事务的完成。

整个DDR内存控制器通过精心设计的接口和调度机制,实现了对多种DDR内存类型的支持,并优化了内存访问的效率和性能。无论是通过AXI接口的并行处理能力,还是通过DDRC和DDRP的精细调度和物理层处理,都确保了系统能够高效、可靠地访问DDR内存。

DDRI

DDR Controller System Interface (DDRI) 是一个关键组件,它连接了处理器或主设备与DDR内存系统,提供了高效、灵活的数据传输和控制机制。以下是DDRI的一些核心特性详解:

四个相同的64位AXI端口:DDRI提供了四个独立的64位AXI端口,每个端口都支持INCR(递增)和WRAP(回环)两种突发类型。这使得系统能够同时处理来自多个主设备的读写请求,提高了数据传输的并行性和效率。

独立的读写端口和32位寻址:每个64位AXI接口都包含独立的读写端口,这有助于优化数据传输流程,减少冲突。同时,使用32位寻址允许访问大量的内存地址空间。

写数据字节使能支持:对于每个数据节拍(beat),DDRI支持写数据字节使能(write data byte enable),这意味着可以仅更新数据总线上的特定字节,而不是整个数据字,从而提高了写操作的灵活性和效率。

复杂的仲裁方案:为了防止数据饥饿(即某些主设备长时间无法获得访问权),DDRI采用了复杂的仲裁方案。这些方案可以根据请求的优先级、等待时间等因素来公平地分配访问权。

低延迟路径:DDRI提供了一个低延迟路径,使用紧急位(urgent bit)来绕过仲裁逻辑,允许高优先级的请求快速获得访问权。

深度读写命令接受能力:DDRI具有深度读写命令队列,能够同时接受并处理多个读写命令,提高了系统的吞吐量和响应速度。

乱序读数据返回:对于来自不同主设备ID的请求,DDRI可以乱序返回读数据。这有助于优化数据传输流程,减少等待时间。

九位AXI ID信号:所有端口上的AXI ID信号均为九位,这允许系统支持更多的主设备,提高了系统的可扩展性。

灵活的突发长度和大小:DDRI支持从1到16个数据节拍的突发长度,以及1、2、4、8字节每节拍的突发大小。这提供了灵活的数据传输选项,以适应不同的应用场景。

不支持锁定访问:DDRI不支持从任何AXI端口发起锁定访问(locked accesses),这有助于简化系统设计并减少潜在的冲突。

低延迟读机制:通过使用HPR(高优先级读)队列,DDRI实现了低延迟读机制,可以更快地响应高优先级读请求。

特殊紧急信号:DDRI向每个端口发送特殊紧急信号,以便在需要时快速响应高优先级请求。

TrustZone区域可编程:DDRI支持在64MB边界上编程TrustZone区域,这有助于实现安全分区,保护敏感数据不被未授权访问。

独占访问:对于每个端口,DDRI支持两个不同ID的独占访问。然而,需要注意的是,不支持跨不同端口的独占访问,且不支持锁定事务。

这些特性共同构成了DDRI的强大功能,使得DDR内存系统能够高效地支持各种复杂的应用场景。

DDRP

DDR Controller PHY (DDRP) 是DDR内存控制器中的物理层接口,它负责处理与DDR内存模块之间的物理信号传输。DDRP 的特性直接关系到内存访问的速度、稳定性和效率。以下是DDRP的一些关键特性:

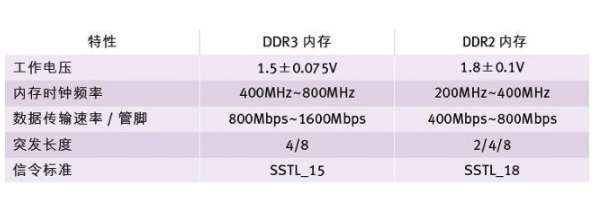

兼容多种DDR I/O电压:DDRP支持多种DDR接口电压标准,包括1.2V的LPDDR2、1.8V的DDR2、以及1.5V的DDR3和1.35V的DDR3L。这种兼容性使得DDRP能够适配不同版本的DDR内存,增强了系统的灵活性和扩展性。

可选的16位和32位数据总线宽度:DDRP支持配置为16位或32位的数据总线宽度。这种灵活性允许系统设计者根据具体的性能需求和内存容量来选择合适的总线宽度,以达到最佳的系统性能。

可选的ECC在16位数据宽度配置中:在16位数据宽度配置下,DDRP支持可选的错误检查与纠正(ECC)功能。ECC能够检测并纠正数据传输中的错误,提高数据的完整性和可靠性。

软件控制的自刷新进入和命令到达时的自动退出:DDRP支持通过软件命令进入自刷新模式,以在不需要访问内存时降低功耗。当新的命令到达时,DDRP会自动退出自刷新模式,准备处理新的内存访问请求。

基于可编程空闲周期的自主DDR掉电进入和退出:DDRP能够根据预设的空闲周期自动进入和退出DDR掉电模式。这种自主管理功能有助于进一步降低系统功耗,特别是在系统负载较低时。

数据读选通(strobe)自动校准:为了确保数据传输的准确性和稳定性,DDRP支持数据读选通自动校准功能。该功能能够自动调整读选通信号的相位和时序,以匹配数据信号的边缘,从而减少数据传输中的错误和失真。

这些特性共同构成了DDRP的强大功能,使得DDR内存控制器能够高效地与DDR内存模块进行通信,确保数据的快速、准确和可靠传输。通过优化DDRP的配置和使用,可以显著提高系统的整体性能和稳定性。

DDRC

DDR Controller Core and Transaction Scheduler (DDRC) 是DDR控制器中的核心组件,它主要负责管理内存事务的调度和执行,以确保数据的高效传输和访问。

高效的事务调度以优化数据带宽和延迟

DDRC通过智能地调度内存访问请求,使得数据能够在CPU、图形处理器或其他系统组件之间高效传输。它能够识别并优先处理高优先级或紧急的数据传输请求,从而最大化数据带宽的利用率。通过精细控制事务的执行顺序和时间,DDRC能够减少数据访问的延迟。它可以根据系统的实时需求动态调整调度策略,确保关键数据的快速访问。

先进的重排序引擎以最大化内存访问效率

对于连续读写操作,DDRC的重排序引擎能够识别并重新排列内存访问请求,以减少DRAM的页面切换和激活延迟。这通过减少不必要的DRAM操作来提高整体访问效率。

对于随机读写操作,DDRC能够利用重排序引擎来合并相邻的内存访问请求,从而减少内存总线的负载并提高访问效率。这种优化对于处理来自多个处理器或系统组件的随机访问请求尤为重要。

读写地址冲突检测以避免数据损坏

DDRC在调度内存访问请求时,会检查读写地址是否存在冲突。如果发现冲突(即同一地址在同一时间被不同的读写请求访问),它会暂停或重新调度相关请求,以避免数据损坏或不一致性。除了地址冲突检测外,DDRC还可能包含其他保护机制,如错误纠正码(ECC)等,以确保数据的完整性和可靠性。

遵守AXI排序规则

DDRC通常与AXI总线接口紧密集成,以支持高级别的数据传输和控制。它必须遵守AXI协议的排序规则,以确保不同主设备之间的数据访问顺序一致性和正确性。

在AXI协议中,事务ID(Transaction ID)用于标识和跟踪内存访问请求。DDRC需要管理这些事务ID,以确保它们按照正确的顺序被处理和返回给请求者。

综上所述,DDRC及其交易调度器是DDR控制器中的关键组件,它们通过高效的事务调度、先进的重排序引擎、读写地址冲突检测以及遵守AXI排序规则等特性,确保了数据的高效传输和访问。这些特性对于提高系统性能、降低延迟和保护数据完整性至关重要。

方框图

DDR内存控制器的框图如下图所示。DDR内存控制器由一个仲裁器、一个带有事务调度器的内核和DDR内存信号的物理排序组成。

控制器核心和事务调度器中包含两个32条目的CAMs(内容可寻址存储器),用于执行DDR数据服务重排序。这种重排序机制旨在最大化DDR内存访问的效率,特别是对于连续读写和随机读写操作。通过重新排列内存访问请求的顺序,可以减少DRAM的页面切换和激活延迟,从而提高整体性能。除了通过CAM进行重排序外,该控制器还包含一个Fly-by通道,允许某些内存访问请求绕过CAM进行低延迟访问。这对于需要快速响应的关键任务特别有用,因为它们可以更快地访问DDR内存而无需等待CAM的重排序过程。

PHY(物理层)负责处理来自控制器的读写请求,并将这些请求转换为符合目标DDR内存时序约束的特定信号。这些信号包括时钟信号、命令信号、地址信号和数据信号等,它们共同构成了DDR内存操作的完整序列。PHY使用来自控制器的信号来产生内部信号,这些内部信号通过PHY连接到PS的焊盘(pads)。这些焊盘直接通过PCB信号迹线连接到外部内存设备,从而实现DDR内存与处理器系统之间的物理连接。

仲裁器负责跨四个AXI端口进行仲裁,以确定哪个端口可以访问DDR核心。仲裁是基于优先级的,允许系统根据当前的任务需求和资源利用率来动态调整各个端口的访问权限。此外,仲裁器还支持通过紧急机制来提升某些任务的优先级,以确保关键任务能够及时获得DDR内存的访问权限。

注意事项:

通常情况下,CLG225系列设备支持32位和16位两种数据总线宽度选项。这意味着大多数CLG225设备可以根据系统需求配置为使用32位或16位的数据总线,以适应不同的数据传输速率和带宽要求。

然而,对于7z007s单核心和7z010双核心这两款特定的CLG225设备,它们的数据总线宽度支持受到了限制。这两款设备仅支持16位数据总线宽度,而不支持32位数据总线。这意味着在设计和使用这两款设备时,需要特别注意它们的数据传输能力和系统接口兼容性,确保它们能够与其他系统组件正确协作。

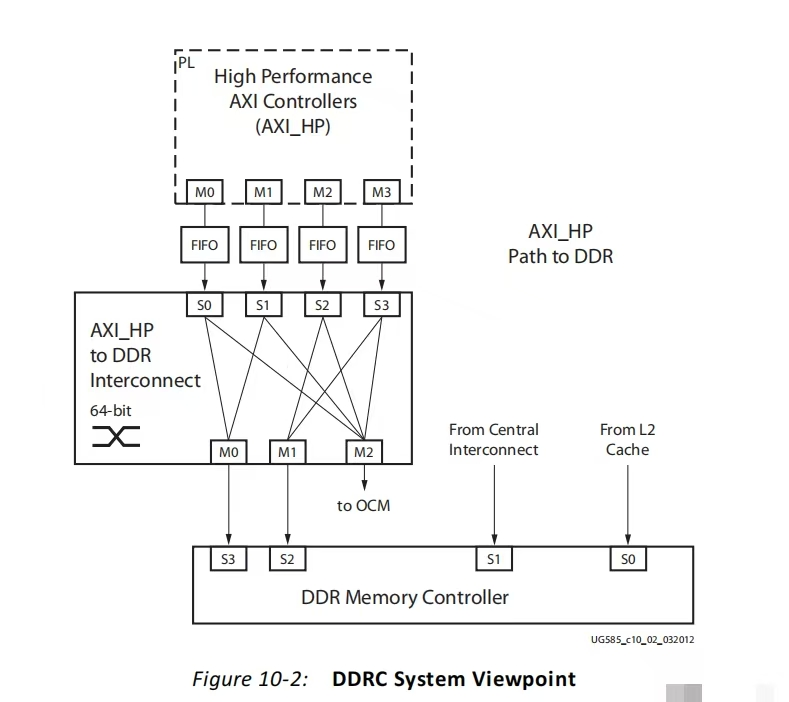

AXI的互联系统

该系统在处理器与DDR内存之间提供高效的数据传输。这里详细说明了AXI_HP(高性能)接口、DDR内存端口仲裁器、互联开关、QoS(服务质量)信号以及L2缓存的连接和配置方式。

AXI_HP接口:有四个AXI_HP接口,它们被成对复用,并连接到图10-2中所示的端口2和端口3。这些端口通常配置为高带宽流量使用,以支持大量数据的快速传输。

DDR内存端口仲裁器:从这四个AXI_HP接口到DDR内存的路径包括DDR内存端口仲裁器上的两个端口。互联开关负责在这两个端口之间进行双向仲裁,以决定何时允许哪一侧进行数据传输。

读/写通道分离:在互联系统中,读和写通道是分开操作的,这意味着它们可以独立地管理数据的读取和写入,从而提高数据传输的效率。

QoS(服务质量)仲裁:互联桥接器中的仲裁受到来自每个PL接口的QoS信号的影响。具有更高QoS值的请求者会被互联桥接器优先处理。这种基于优先级的仲裁机制确保了关键任务或高优先级的数据传输能够优先进行。

LRG方案:在QoS值相同的情况下,即出现优先级相同的情况时,会使用LRG(可能是指某种负载均衡或随机选择)方案来打破这种平局,确保公平性和系统的稳定性。

L2缓存:L2缓存连接到端口0,并用于服务CPU和PL的ACP(加速器一致性端口)接口。这个端口通常配置为低延迟,以快速响应CPU和ACP的数据请求。

其他AXI主设备:AXI互联上的其他主设备(如其他处理器或外设)连接到端口1,这些设备通过AXI互联与DDR内存、L2缓存等资源进行通信。

总的来说,这个互联系统通过高效的仲裁机制、QoS支持和缓存技术,为处理器和DDR内存之间提供了高性能、低延迟的数据传输路径。

原文连接:https://tencentcloud.csdn.net/678a2060edd0904849a677be.html

-

FPGA

+关注

关注

1655文章

22283浏览量

630285 -

控制器

+关注

关注

114文章

17638浏览量

190255 -

接口

+关注

关注

33文章

9444浏览量

156143 -

Zynq

+关注

关注

10文章

625浏览量

49239 -

DDR内存

+关注

关注

0文章

22浏览量

7322

原文标题:Zynq7000系列FPGA中的DDR内存控制器

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

PrimeCell DDR2动态内存控制器(PL341)循环模型9.1.0版用户指南

DDR内存接口的设计与实现

利用DDR控制器读取重排序缓冲器,将DRAM带宽提高十倍

基于FPGA的DDR3协议解析逻辑设计

TMS320DM646x数字媒体系统DMSoC的DDR2存储控制器详细介绍

完整的DDR、DDR2和DDR3内存电源解决方案同步降压控制器数据表

完整的DDR2、DDR3和DDR3L内存电源解决方案同步降压控制器TPS51216数据表

DDR内存控制器的架构解析

DDR内存控制器的架构解析

评论