前言

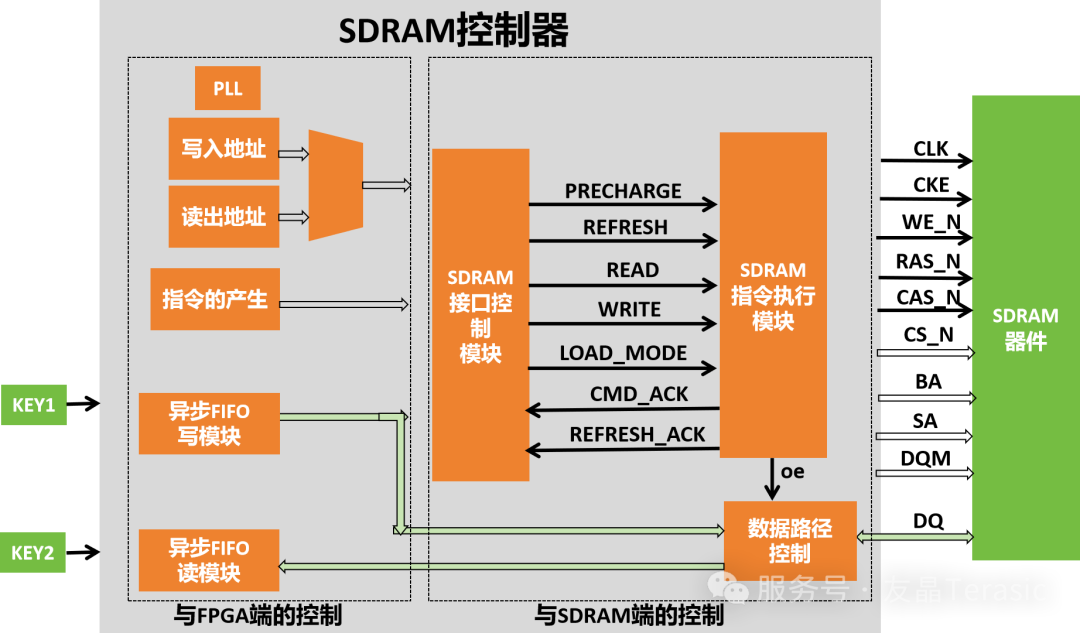

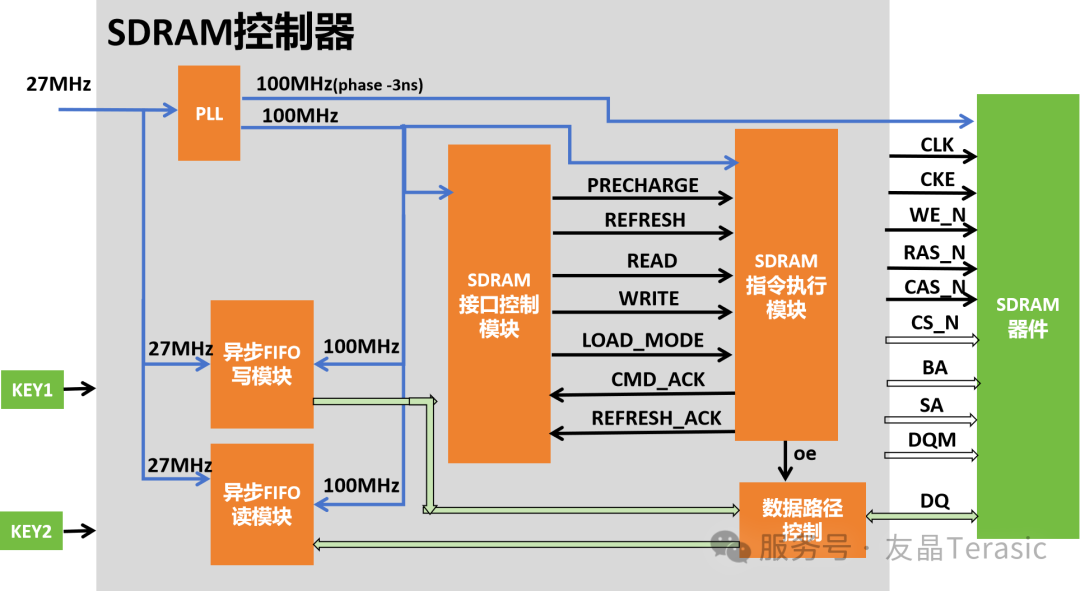

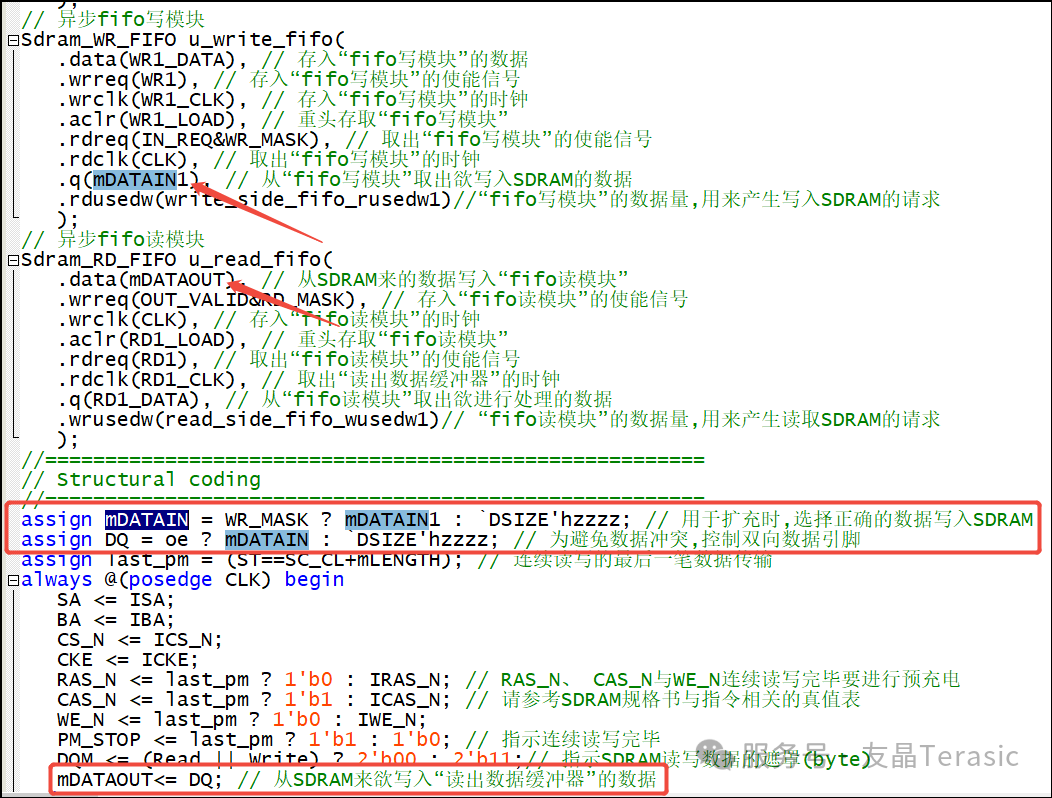

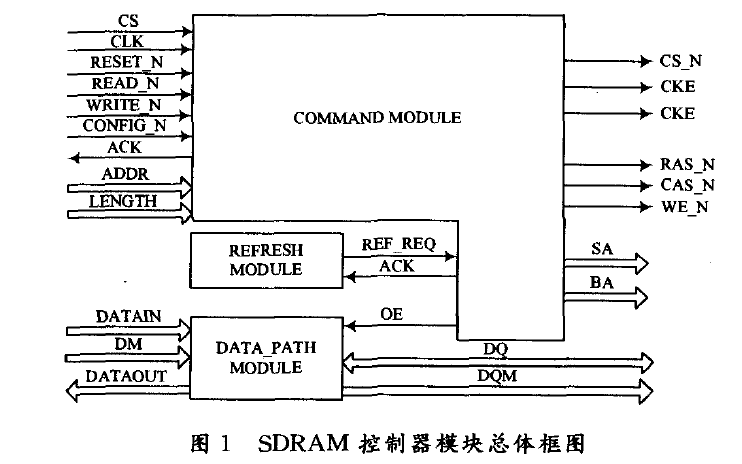

SDRAM控制器里面包含5个主要的模块,分别是PLL模块,异步FIFO 写模块,异步FIFO读模块,SDRAM接口控制模块,SDRAM指令执行模块。

其中异步FIFO模块解读参考:05-SDRAM控制器的设计——异步FIFO的调用;

https://www.elecfans.com/d/6468023.html

SDRAM接口控制模块解读参考:03-SDRAM控制器的设计——control_interface.v代码解析;

https://www.elecfans.com/d/6458523.html

SDRAM指令执行模块解读参考:04-SDRAM控制器的设计——command.v代码解析

https://www.elecfans.com/d/6466276.html

PLL时钟模块

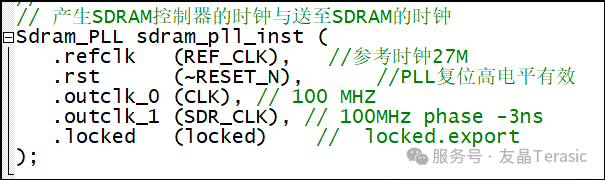

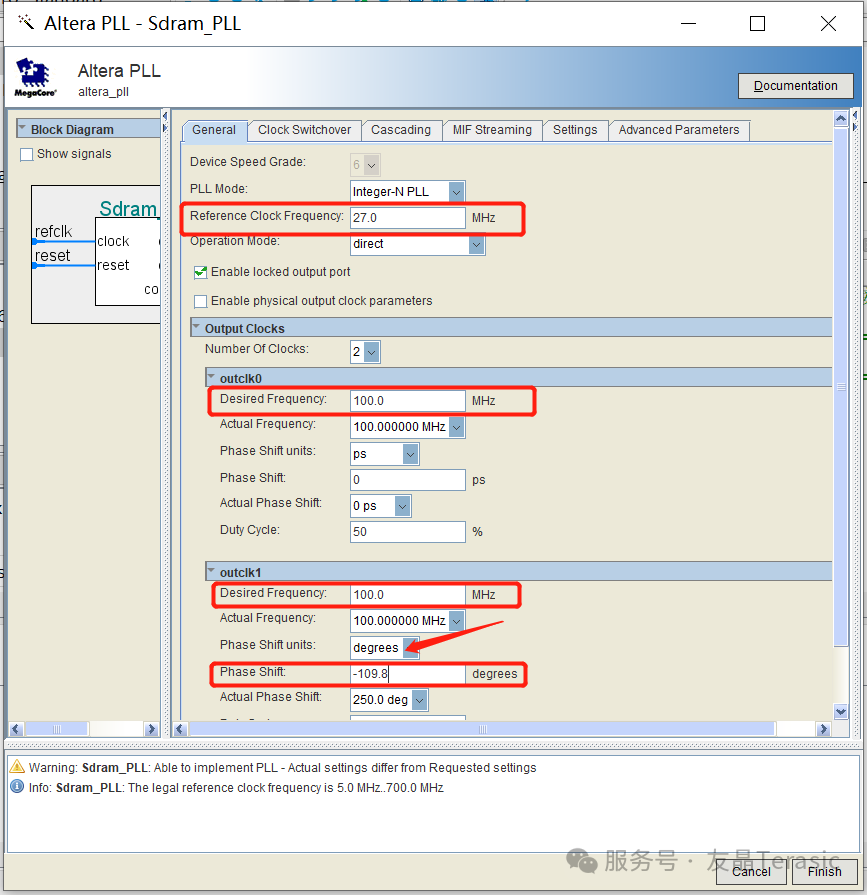

SDRAM控制器模块里面的PLL将27MHz时钟倍频出2个100MHz时钟,其中一个100MHz时钟给SDRAM里面的模块使用;另外一个100MHz时钟相移-109.8°以后输出给SDRAM器件。(相移-109.8°是这个SDRAM器件在DE10-Standard开发板上的时序约束经验值)

PLL参数设置如下:

关于Sdram_Control.v模块时钟分布请参考下图的蓝色走线:

其实也可以直接从FPGA 的50MHz时钟经过PLL得到100M时钟传递给工程里其他模块工作,这里设置27M是为了让大家看看FIFO跨时钟域的一个工作情况。

数据路径控制

SDRAM的数据口是一个inout接口,要做成三态门控制,控制电路代码如下:

从command.v传过来的oe信号为高时,将数据送到DQ端口,此为SDRAM的写入操作;当oe信号为低时,DQ输入为高阻,三态门截止,DQ端口的数据送出给读fifo模块进行缓存,此为SDRAM的读操作。(关于oe信号的控制请参考04-SDRAM控制器的设计——command.v代码解析)

自动且连续的读写操作

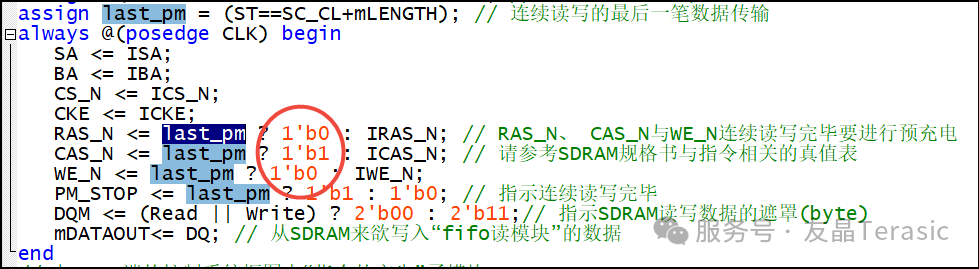

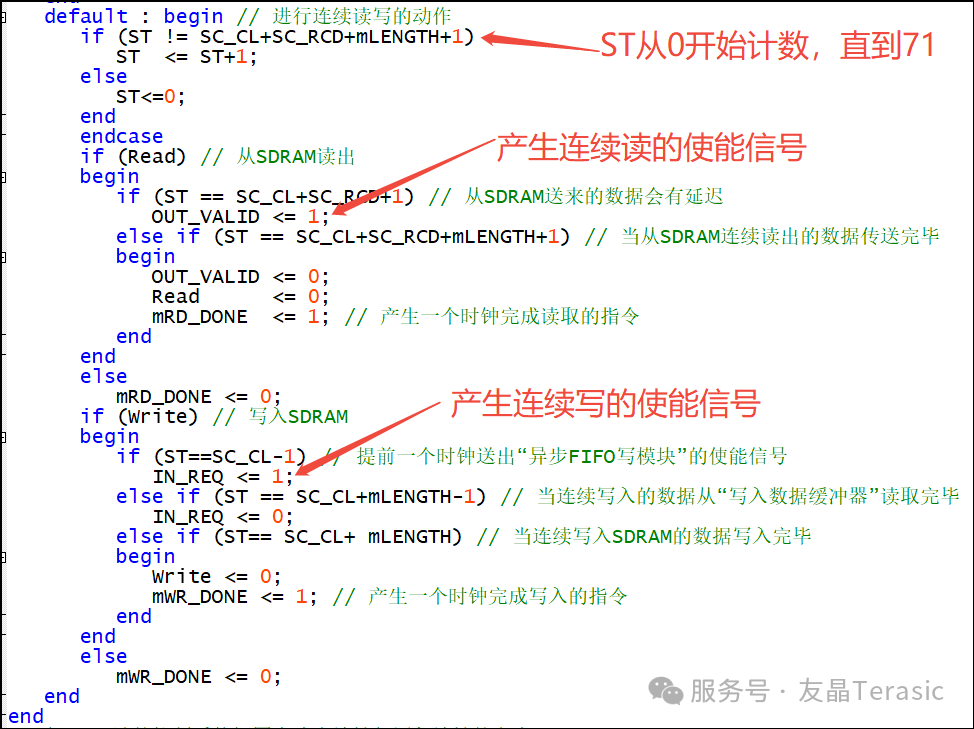

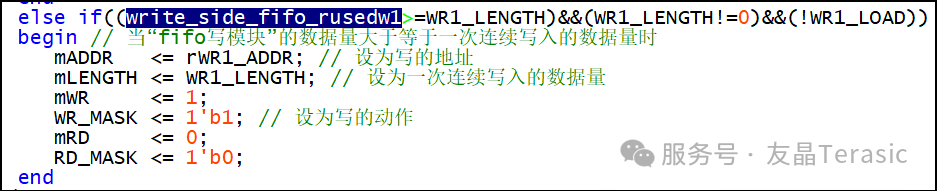

接下来是设置完成连续读写(64个数据)以及进行突发中断的操作。

command.v模块里面已经设置突发长度为整页(整页可读写数据量为1024),所以每次读写64个数据后需要提前中断突发操作。根据IS42R16320D手册可知下发突发中断命令或者预充电命令可提前结束突发操作。

该案例选择预充电命令来结束突发操作。参考前面的章节可知预充电命令是RAS_N, CAS_N,WE_N组合为010。

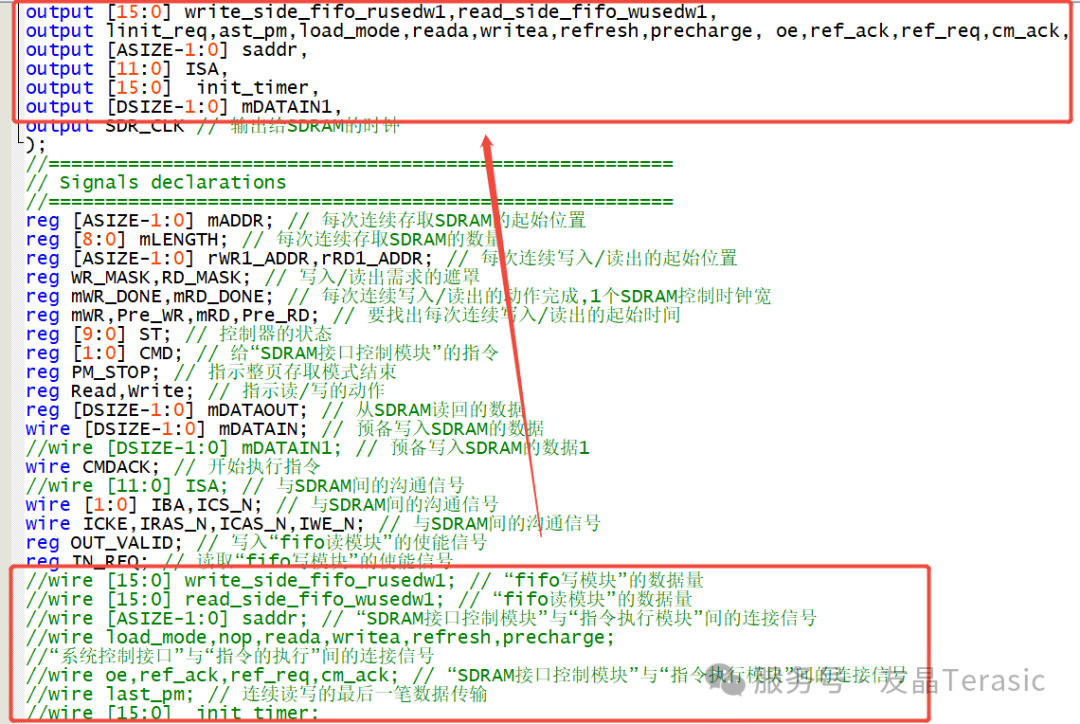

为了拉出相关信号查看其波形,先要暂时把这些信号输出,不然这些信号会被Quartus在综合操作时优化掉。

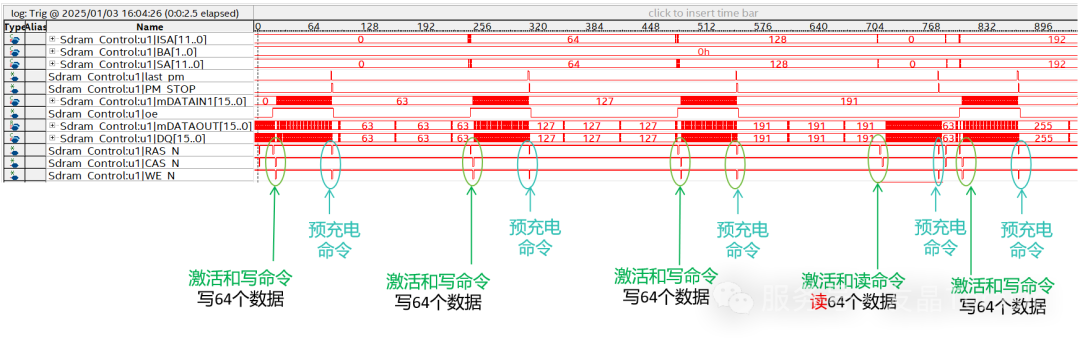

从波形图可以看到,确实在每次读或者写64个数据后,都会跟着出现一个预充电命令来结束全页突发操作。

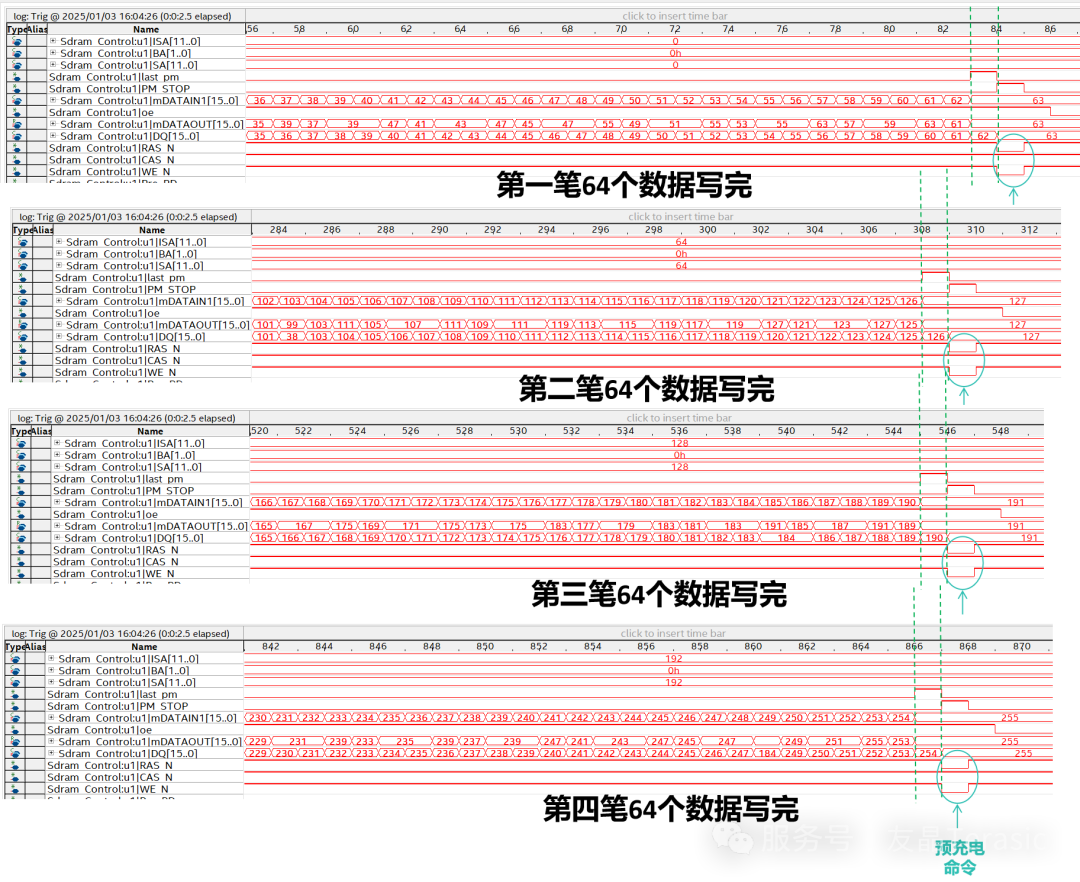

如果上面总体的图缩小看不清,可以参考下面放大的图:

可能大家会疑惑为什么不直接写256个数据,然后读256个数据?这里设置64个数据长度是为了让大家看到多次读和写是如何进行的。

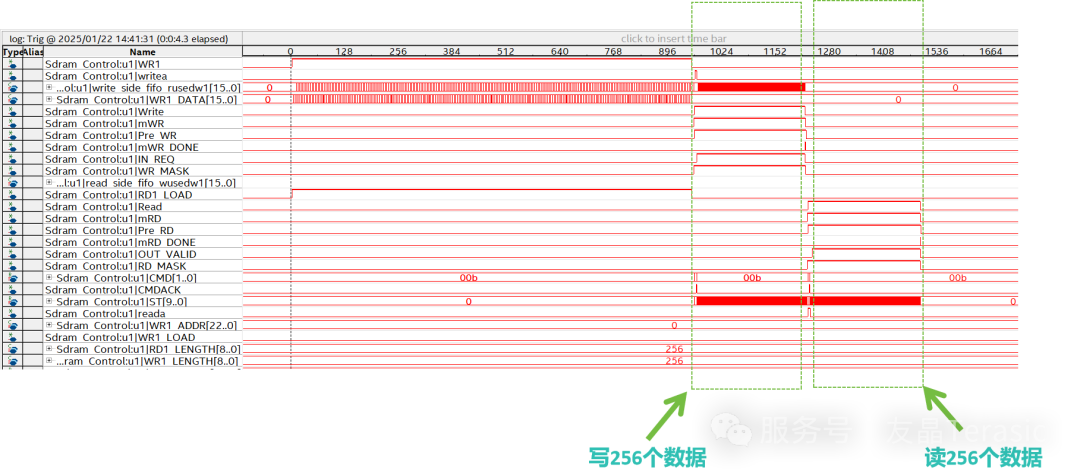

如果想设置256个数据也是可以的,这时就把自动读设计成写完256个数据后自动进行。

此时的波形图如图所示(一次性写完256个数据,一次性读完256个数据):

指令的产生

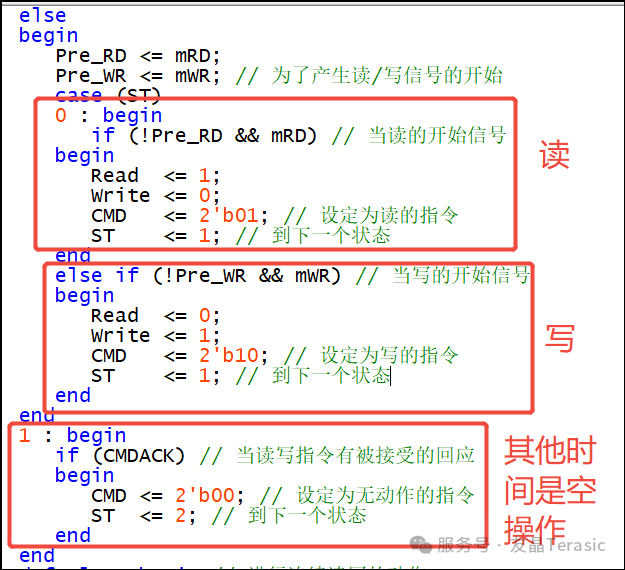

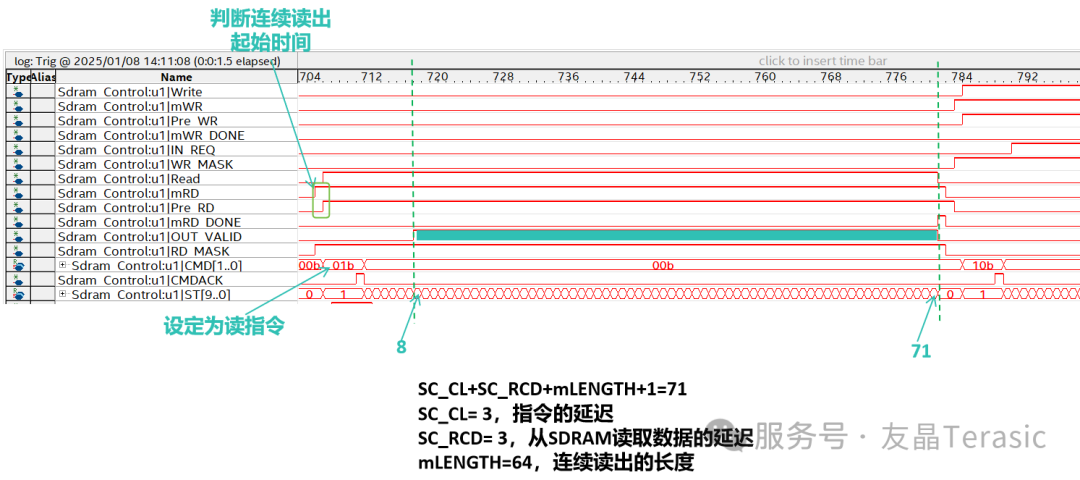

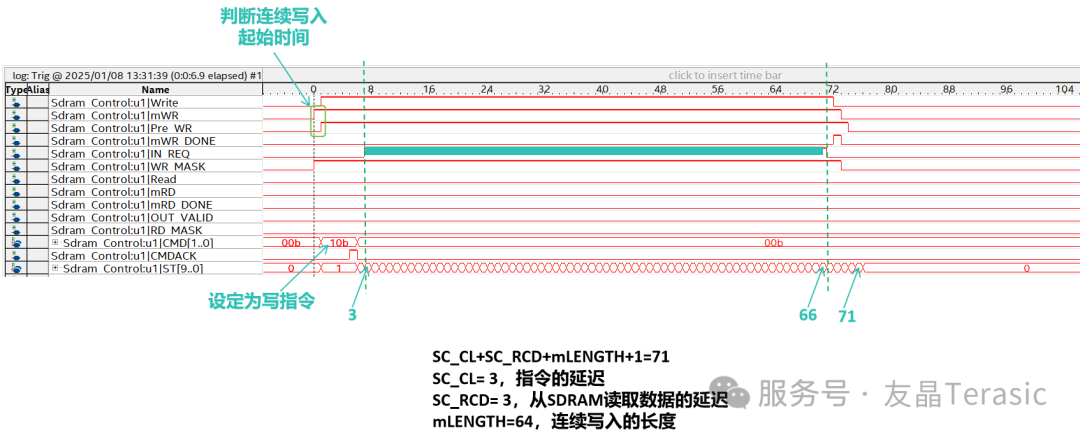

读过程通过Pre_RD和mRD信号的组合标志出连续读的起始时间,通过Read信号标志出连续读的过程。

写过程通过Pre_WR和mWR信号的组合标志出连续写的起始时间,通过Write信号标志出连续写的过程。

当FIFO读模块中的数据量低于一次需要读取的数据量时,mRD置1;直到连续读完成时,mRD才会清零。即mRD保持为0或1的状态都会持续多个周期,因此我们无法通过电平状态来判断是否产生开始读信号Read,所以这里采取用寄存器保存mRD的前一状态,并与当前状态进行比较,当前一状态为0,当前状态为1,即产生上升沿时,开始读信号Read信号置1。写信号同理。

提前一个时钟送出异步FIFO写模块的读出使能信号是因为写数据没有延迟,写命令发出的当拍要准备好数据,所以读使能信号提前一拍给出。

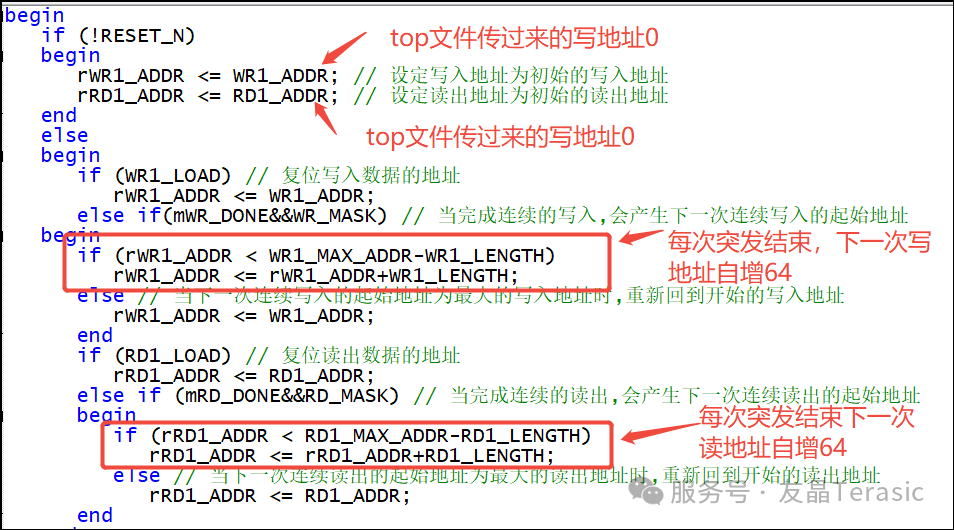

写入地址和读出地址

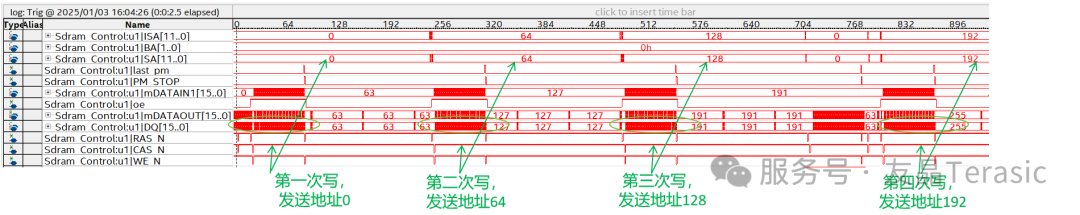

256个数据写入节奏是这样的:

当KEY1被按下,触发了counter产生数据0~255,这个数据同步传递给异步FIFO写模块进行缓存。当系统检测到write_side_fifo_rusedw1值大于64时,异步FIFO写模块的读出端口会把FIFO里面的数据读出,传递给SDRAM器件进行储存。FIFO一次读出64个数据。总共会读出4次。

从top文件传递过来的地址0开始写SDRAM,一次写64个数据,写第二笔64个数据时初始地址是0+64,写第三笔64个数据时初始地址是64+64=128,写第四笔64个数据时初始地址是128+64=192。

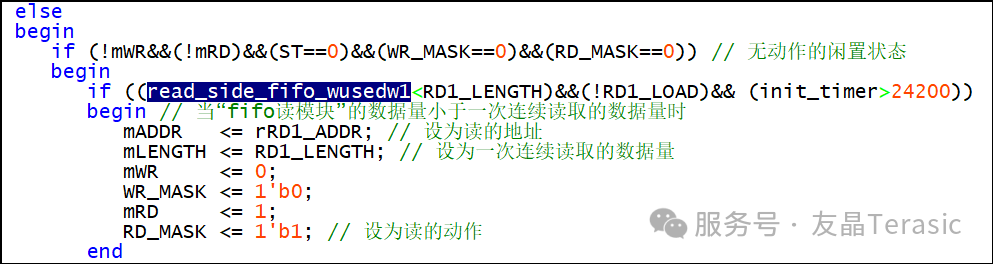

256个数据读出节奏是这样的:

异步FIFO读模块从离开初始化状态且离开复位状态且检测到read_side_fifo_wusedw1小于64时开始读取SDRAM器件的数据。

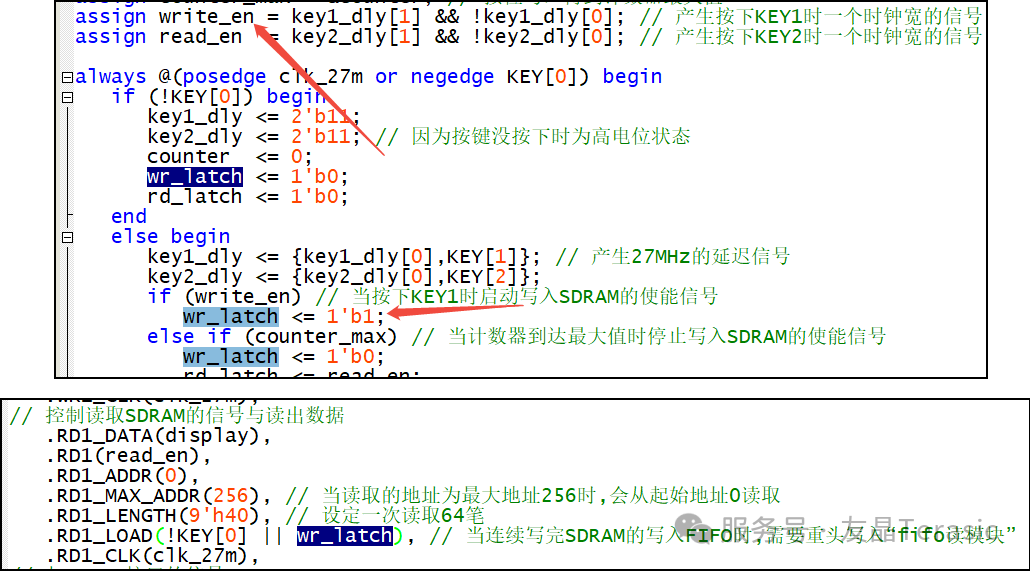

其复位状态的离开主要看KEY0信号和wr_latch信号:

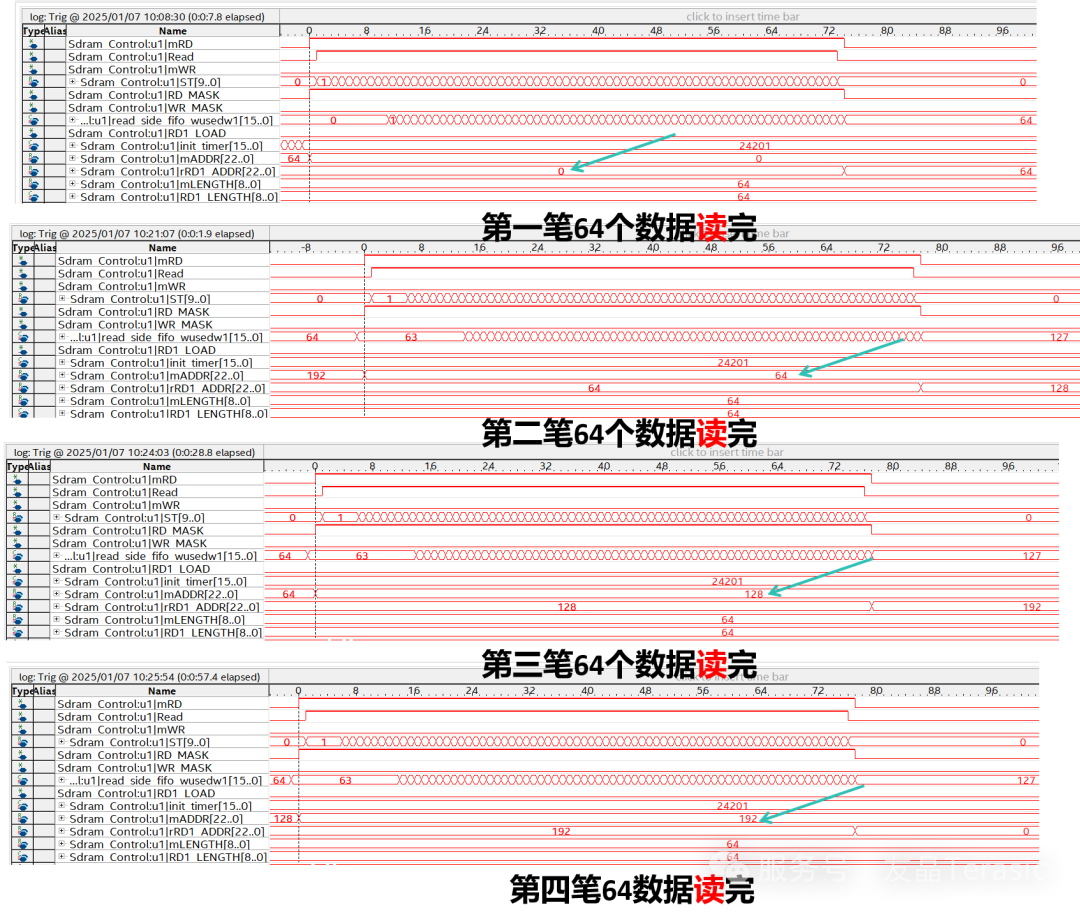

第一笔64个数据(0~63)是等异步FIFO写模块已经完成256个字节的缓存操作(其中的192个数据已写入到SDRAM器件了)以后读出。此时读SDRAM的地址送出是0。

第二笔64个数据(64~127)是等异步FIFO读模块读出第一个数据0的下一个时钟节拍读出,因为此时read_side_fifo_wusedw1的值64-1等于63又小于64。此时读SDRAM的地址送出是64。

第三笔64个数据(128~191)是等到异步FIFO读模块数据又只剩63个数据时读出,此时地址送出是128。

第四笔64个数据(192~255)同样是等到异步FIFO读模块数据又只剩63个数据时读出,此时地址送出是192。

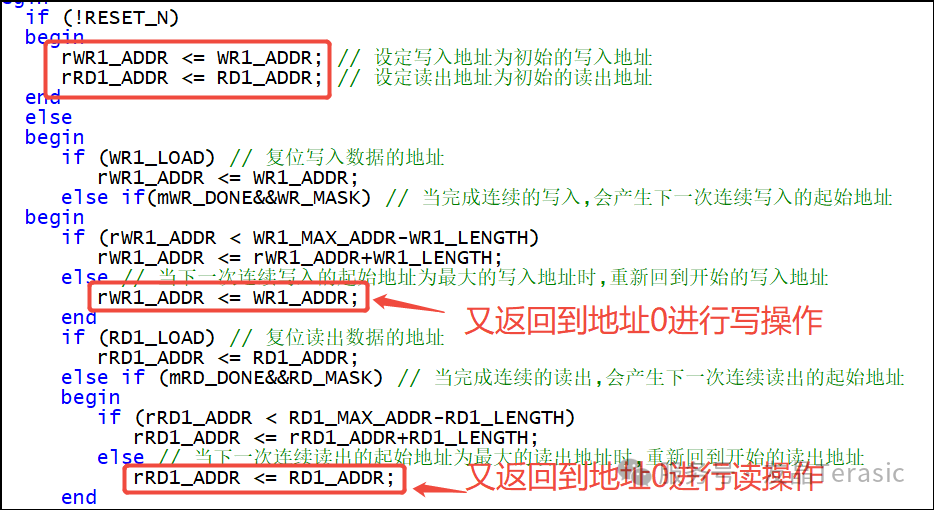

无论是SDRAM写操作还是读操作,在读写完256个数据后又会从地址0开始重复读写:

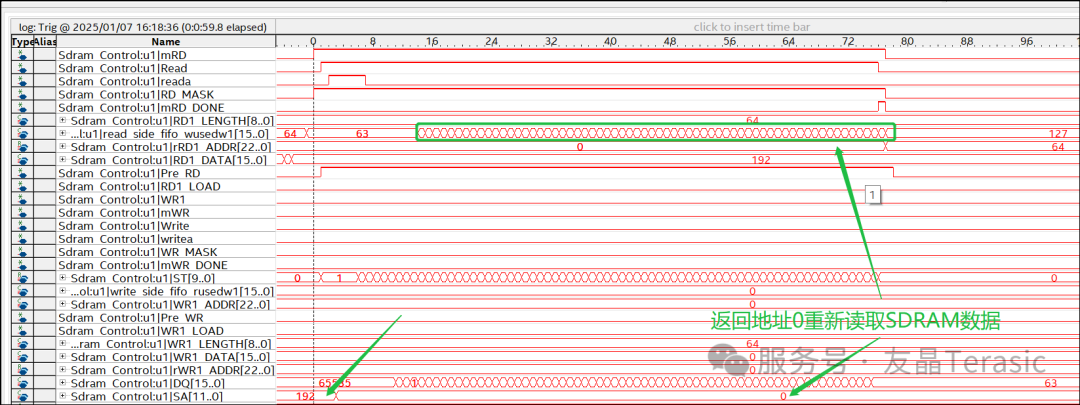

拿SDRAM读操作来说,当读完256个数据还继续触发读操作时抓取波形图可以看到:

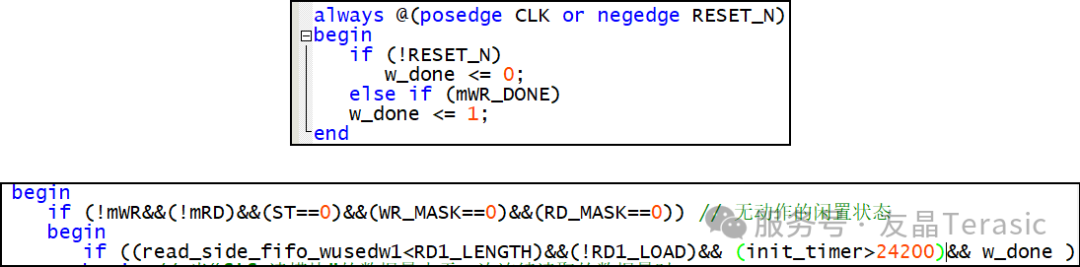

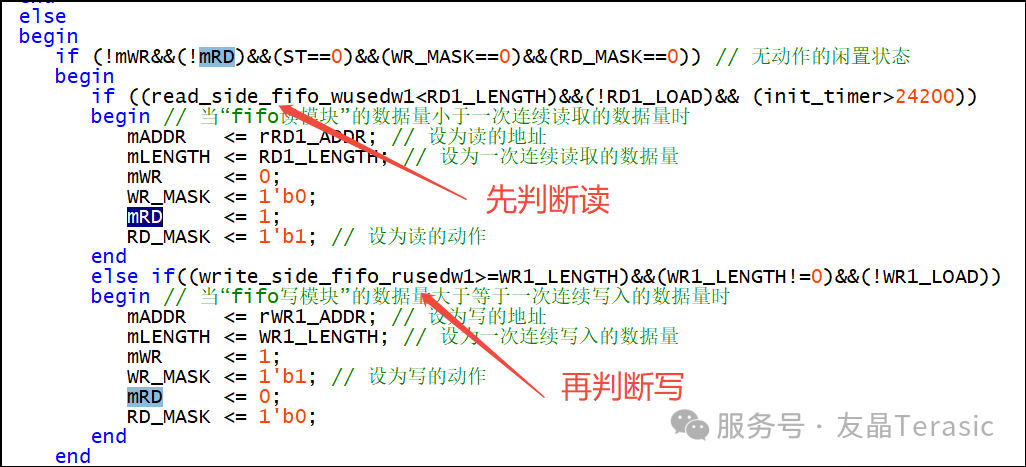

可能读者会有疑惑,当异步FIFO写模块第四次累计了64个数据时,为什么没有马上写入SDRAM器件,而是先从SDRAM器件里面读出64个数据缓存到异步FIFO读模块,等这64个数据读完以后再继续往SDRAM里面写最后的64个数据(192~255)。这里是因为if语句存在优先级,电路是先判断有没有读指令,当有读命令时就先处理读操作。当异步FIFO写模块写入了第四个64个数据后,异步FIFO读模块就离开了复位状态,系统会自动发送读命令,此时就开始SDRAM器件数据的读取操作。

PS:

本文的Signaltap波形图文件对应:~sdramcontroloutput_filesSdram_Control.stp

-

fifo

+关注

关注

3文章

406浏览量

45493 -

代码

+关注

关注

30文章

4941浏览量

73151 -

SDRAM控制器

+关注

关注

0文章

29浏览量

8610

原文标题:07-SDRAM控制器的设计——Sdram_Control.v代码解析

文章出处:【微信号:友晶FPGA,微信公众号:友晶FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【开源骚客】《轻松设计SDRAM控制器》第九讲—解密读写FIFO

多路读写的SDRAM接口设计

【每周FPGA案例】至简设计系列- SDRAM读写控制器

具有时间隐藏特性的数据块读写SDRAM控制器

基于FPGA的高速SDRAM控制器的视频应用

NiosII的奇幻漂流-Chap09-SDRAM-v1.0

SDRAM控制器的设计

FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文

如何使用FPGA设计SDRAM控制器

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)

SDRAM控制器的设计——Sdram_Control.v代码解析(异步FIFO读写模块、读写SDRAM过程)

评论