很多人可能觉得PCB信号速率越高,如25Gbps,56G/112G-PAM4信号等调试上发现的问题会越多,其实不然。我们收到最多的调试问题还是DDR3、DDR4等,不是跑不到额度速率,就是识别不到

2026-01-05 15:46:16

添加Zynq Processing System IP核,配置DDR控制器和时钟。7000系列的Zynq可以参考正点原子DMA回环测试设置。

2025-11-24 09:25:50 2881

2881

本章的实验任务是在 PL 端自定义一个 AXI4 接口的 IP 核,通过 AXI_HP 接口对 PS 端 DDR3 进行读写测试,读写的内存大小是 4K 字节。

2025-11-24 09:19:42 3467

3467

vivado中,怎么将e203内核源代码封装成ip核,并添加总线?

2025-11-10 07:22:49

下面是HummingBird EV Kit给的版图,其中DDR3_D0对应的应该是板子上的FPGA的C2引脚:

不过我在配置MIG的时候,通过读入ucf文件的方式配置DDR3 SDRAM的引脚

2025-11-06 07:57:09

电子发烧友网站提供《DDR3 SDRAM参考设计手册.pdf》资料免费下载

2025-11-05 17:04:01 4

4 前文介绍了DDR3扩展,然而,对于大块数据而言,使用CPU进行搬运速度较慢,因此可以使用DMA进行数据搬运。这里会使用到前文提到的中断与DDR3。

本例中使用了Vivado提供的AXI-DMA

2025-10-29 08:21:10

由于FPGA内部存储资源有限,很多时候不能满足需求,因此可以利用DDR对系统进行存储扩展。由于DDR3内部控制十分复杂,因此可以基于AXI总线,利用Vivado提供的MIG IP对DDR3进行控制

2025-10-29 07:16:34

文件夹内,打开文件夹。阅读readme说明文档,我们能够知道,原作者采用了vivado MIG IP来控制开发板上的DDR3,由于芯来科技的E203平台系统片内总线是icb总线,所以我们需要做跨时钟域

2025-10-28 07:25:32

DDR使用

在我们的项目中,我们使用的是芯来科技的DDR200T开发板,我们通过调用板上的DDR3 IP核完成如下表的配置,配置完成后例化该DDR3,然后利用DMA和VDMA作为数据的缓冲模块,将

2025-10-28 07:24:01

VDMA端口信号

S_AXI_LITE:PS端可以通过AXI_LITE协议对IP核进行控制;

S_AXIS_S2MM:视频流(AXI STREAM)输入到IP核的FIFO中

2025-10-28 06:14:54

蜂鸟E203软核工作的主频为16MHz高频时钟和3.2768KHz低频时钟,并且不同开发板提供的晶振频率不同,因此需要例化mmcm IP核和reset IP核将外部晶振时钟转换为两个不同频率

2025-10-27 07:35:23

:使用DDR200T上板载的DDR3对内存进行扩展

扩展方案结构图:

该方案中DDR3使用vivado提供的axi接口mig的IP核来进行控制,蜂鸟e203源代码中提供了icb2axi模块,可以使发出

2025-10-24 08:12:53

综合时不需要,直接注释掉),并在design source中添加ddr3_model.sv和ddr3_model_parameters.vh文件。

在IP Source中右键点击mig的ip核,然后

2025-10-24 07:25:00

接口,以便我们后面使用axi接口的DDR3。

(2)axi_interconnect模块

(3)mig模块

mig 的模块配置具体可参考:https://blog.csdn.net

2025-10-24 07:08:09

是1bit1bit进来的,则需要tlast,发完最后一个bit时拉高,tuser可以用来配置表示一些用户需要的信息)。

需要注意的是,本以为只有当数据数据的valid拉高后,IP核才能接受数据,但仿真的波形

2025-10-24 07:01:36

Vivado浮点数IP核的一些设置注意点

我们在vivado2018.3中使用了Floating-point(7.1)IP核,可以自定义其计算种类及多模式选择。有时多种计算可以用同一个IP核实

2025-10-24 06:25:22

决定的。 ram 主要用来存放程序及程序执行过程中产生的中间数据、 运算结果等。

rom为只读存储器,只能读取数据而不能向里面写入数据。

本次讲解的ram ip核ram指的是bram,即block

2025-10-23 07:33:21

准备工作:

1.蜂鸟e203的RTL源码;

2.一段分频代码;

3.顶层设计文件(system.v)

4.开发板文件;

5.Nexys4DDR电路图;

6.Nexys4DDR管脚约束模板

2025-10-23 07:22:22

soc_top层的ddr3的接口引出到最顶层system,mig的ddr3管脚约束在配置mig核的时候已经完成,不用再考虑。

(2)综合时需要把ui_clk和clk_16M间的时序路径设成

2025-10-23 06:16:44

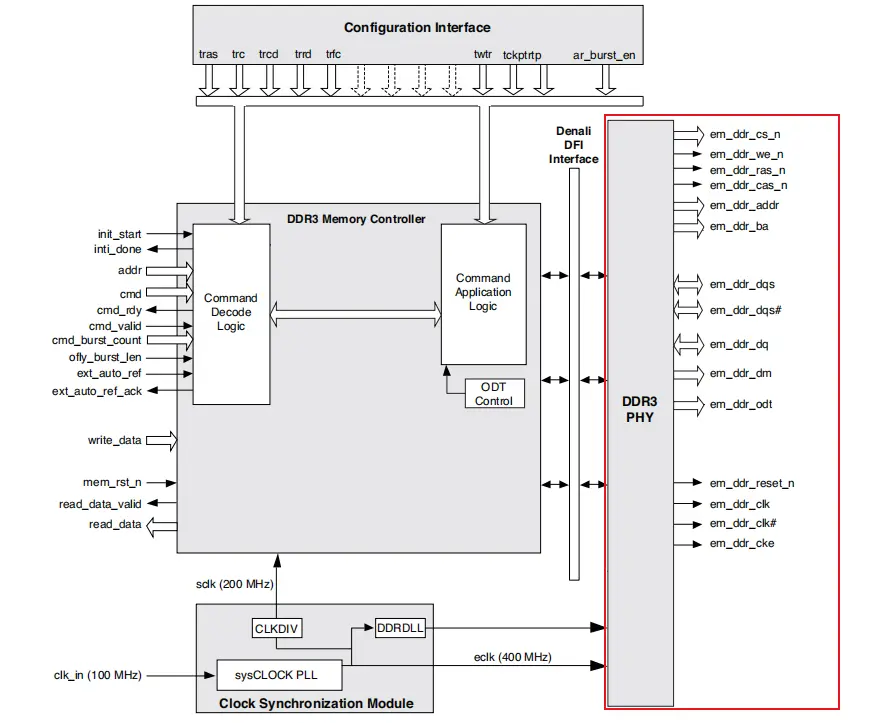

DDR读写操作的控制流程。下图所示是7系列的MIG IP核结构图。MIG IP核对外分出了两组接口,左侧是用户接口,右侧是DDR物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。

DDR3的读写

2025-10-21 14:30:16

IP DDR3控制器 RISC-V

基于DDR200T开发板原理图,找到所需要使用的DDR引脚,制成DDR.ucf文件方便在添加管脚约束时使用。在使用MIG IP核时,为了方便使用DDR产生的时钟

2025-10-21 12:43:40

蜂鸟DDR200T中DDR3的ip配置案列,提供DDR3引脚配置。具体参数可更具项目实际更改。

这里选用的axi接口

在赛灵思的IP配置中没有MT41K28M6JT-125K内存的信息,因此选用

2025-10-21 11:19:08

流程。下图所示是7系列的MIG IP核结构图。MIG IP核对外分出了两组接口,左侧是用户接口,右侧是DDR物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。

DDR3的读写都包含写命令操作

2025-10-21 10:40:28

的控制流程。下图所示是7系列的MIG IP核结构图。MIG IP核对外分出了两组接口,左侧是用户接口,右侧是DDR物理芯片接口,负责产生具体的操作时序,并直接操作芯片管脚。

DDR3的读写都包含写

2025-10-21 08:43:39

回收DDR2,回收DDR3,收购DDR2,收购DDR3 DDR4 DDR5长期现金高价回收DDR,回收三星DDR,回收海力士DDR,回收南亚DDR,回收尔必达DDR,回收美光DDR,回收DDR

2025-10-09 14:15:34

在第二期的特性阻抗讲解中,我们提到了传输线路。虽然将传输线比作水路,但它究竟是通过什么原理传输信号和电力的呢?

2025-10-09 13:49:14 1917

1917

我们常听到的“特性阻抗”究竟是什么?它与通常所说的“阻抗”或“直流电阻”有何区别?虽然“特性阻抗”和“阻抗”都使用[Ω]单位,但它们之间存在什么差异?

2025-09-17 15:07:29 1174

1174

) == RT_Object_Class_Memory) assertion failed at function:rt_smem_alloc, line number:290 ;

然后内核改成V4.1.1就没任何问题。

因为v5.0.2下引入backtrace也始终有编译问题,所以不好跟踪究竟是为何。

2025-09-15 07:46:09

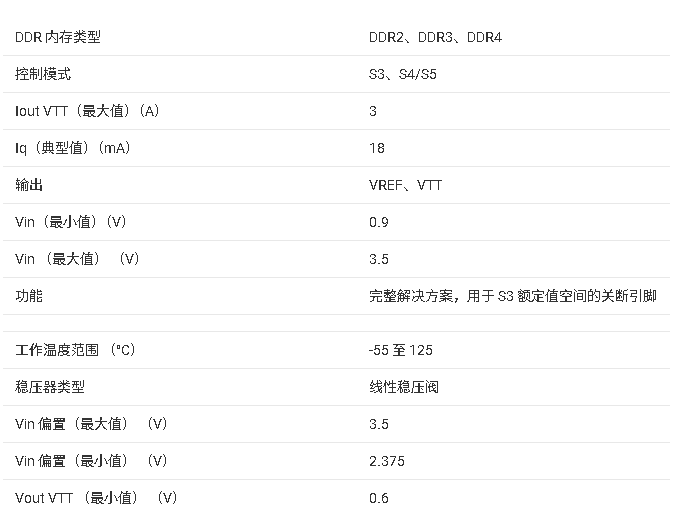

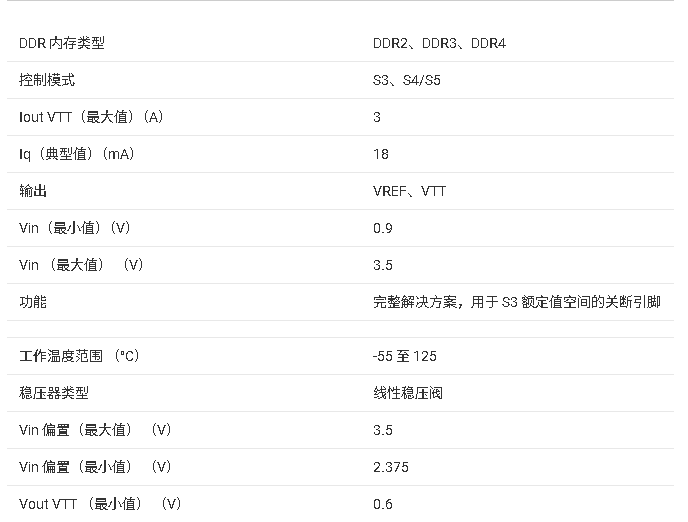

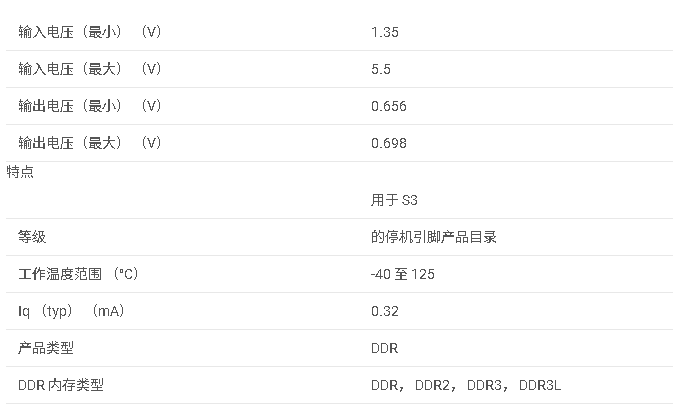

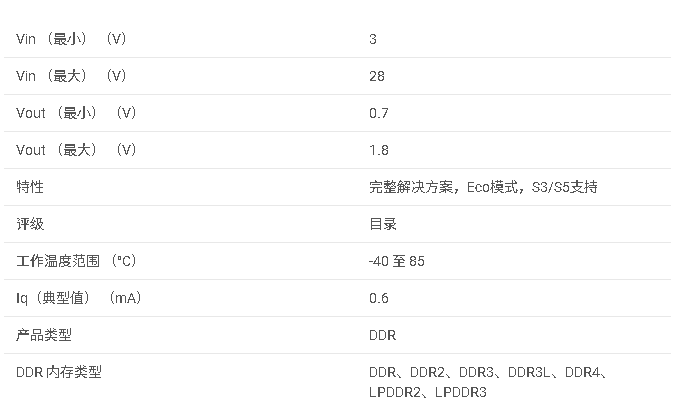

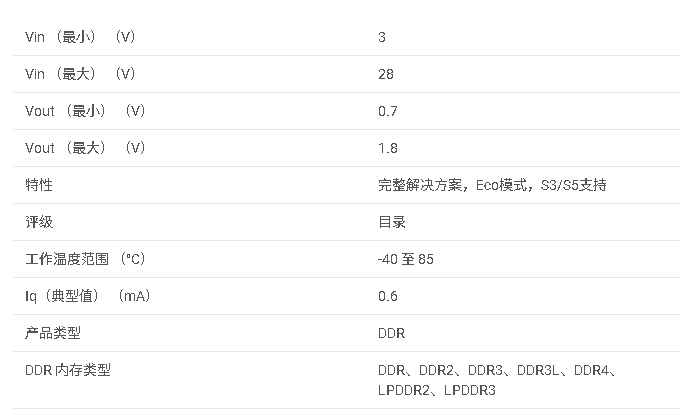

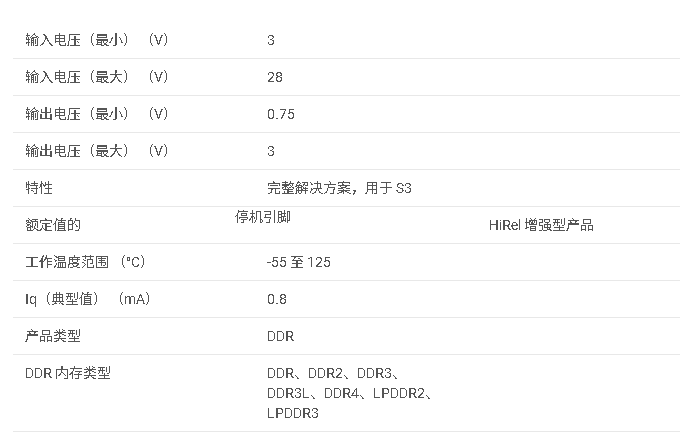

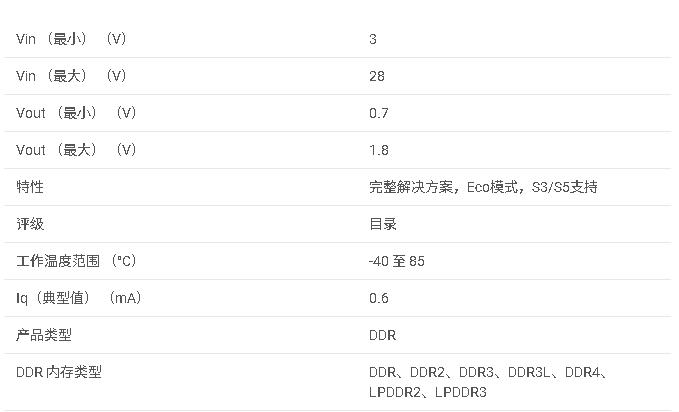

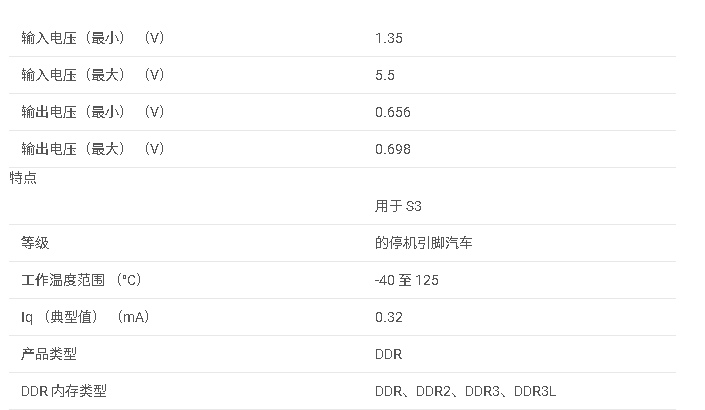

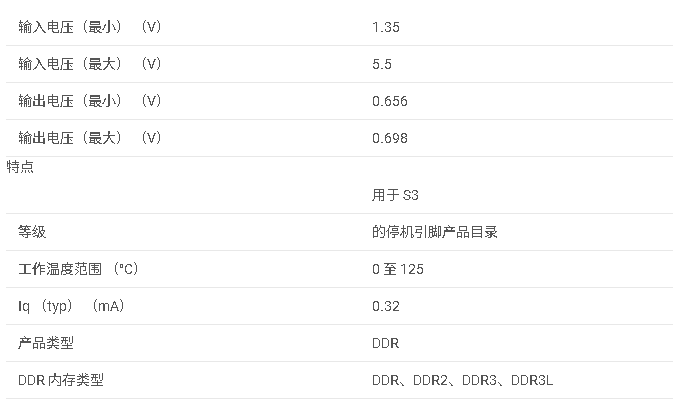

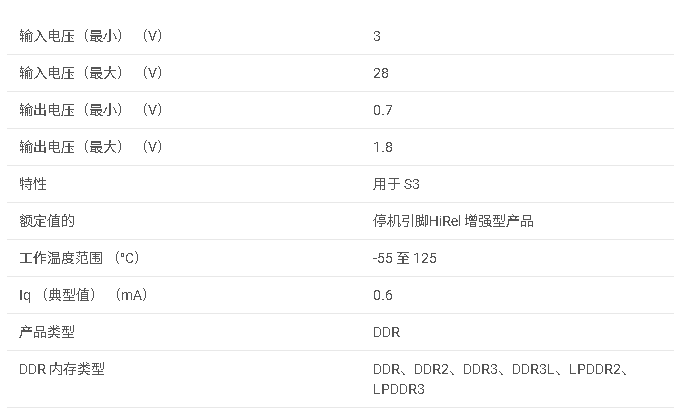

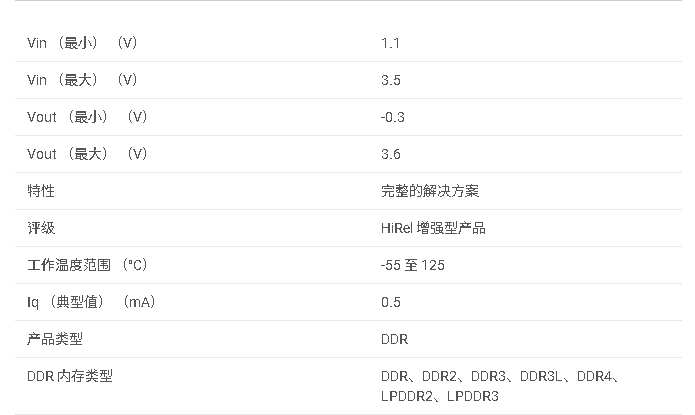

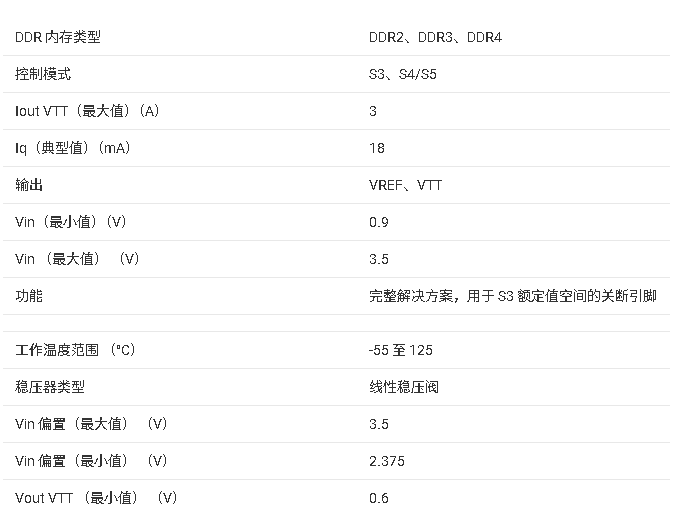

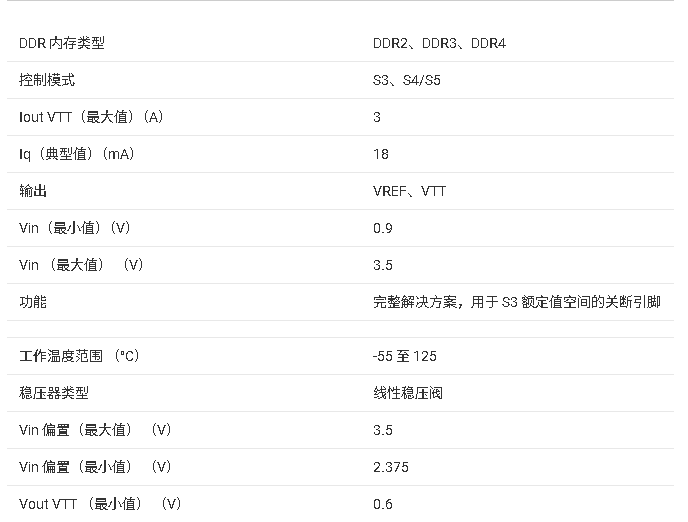

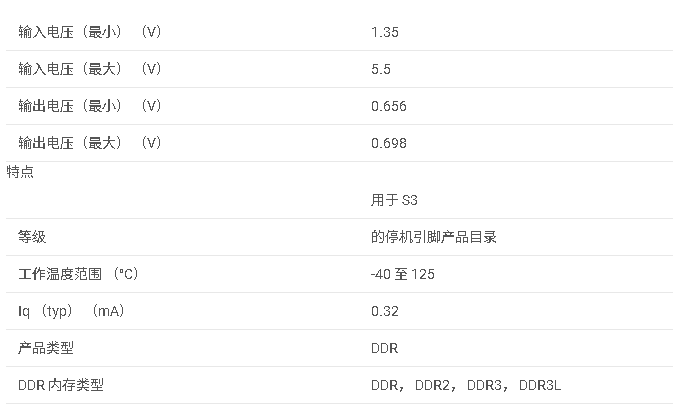

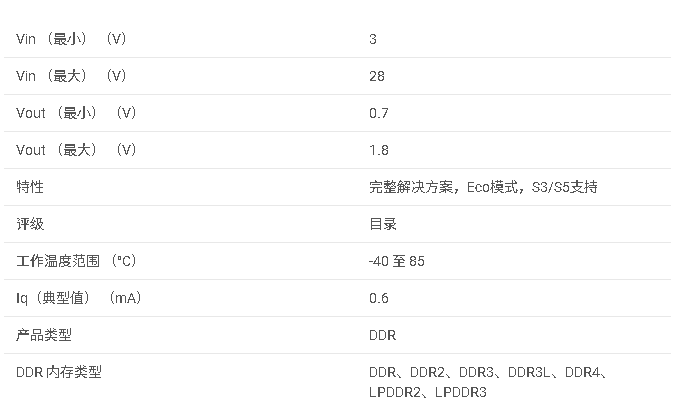

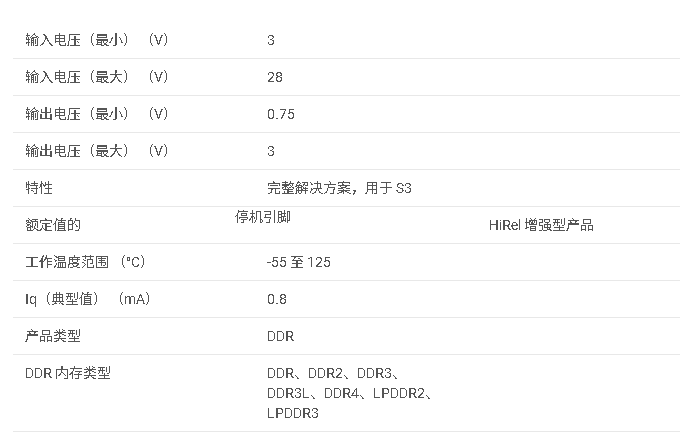

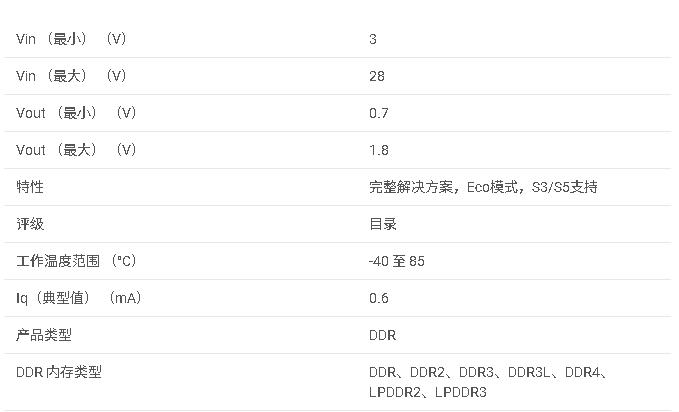

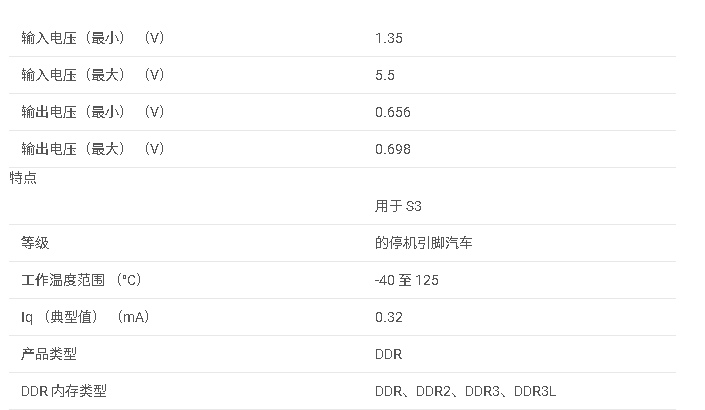

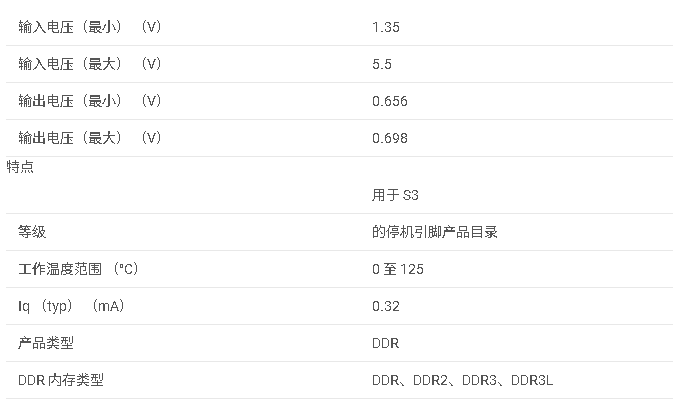

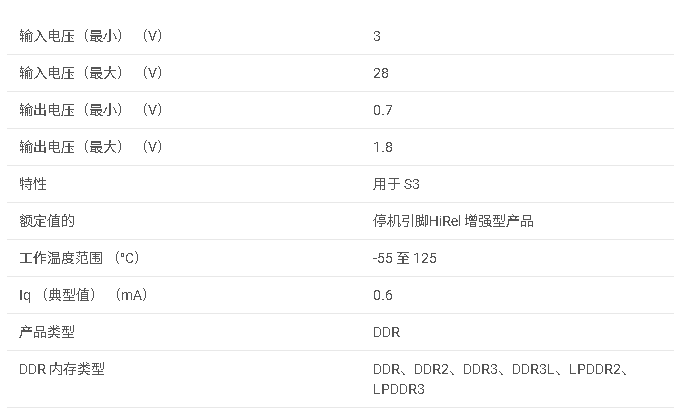

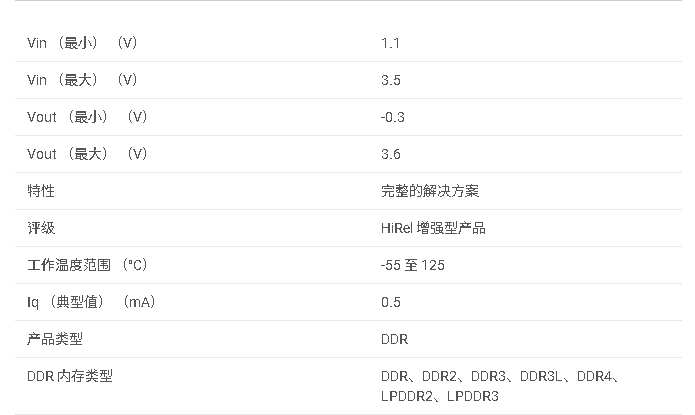

TPS7H3301-SP 支持使用 DDR、DDR2、DDR3、DDR4 的 DDR VTT 端接应用。TPS7H3301-SP VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源。在

2025-09-09 14:45:15 719

719

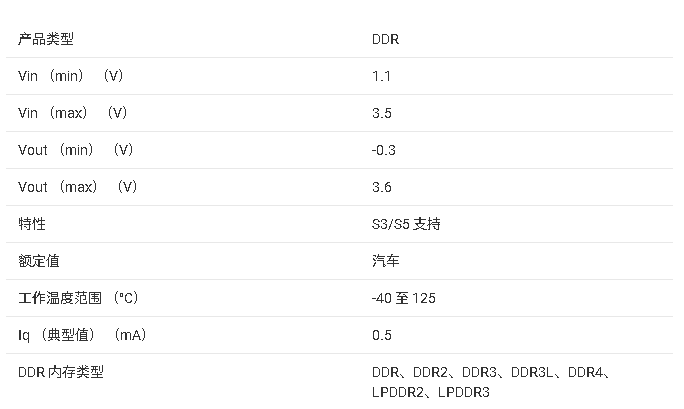

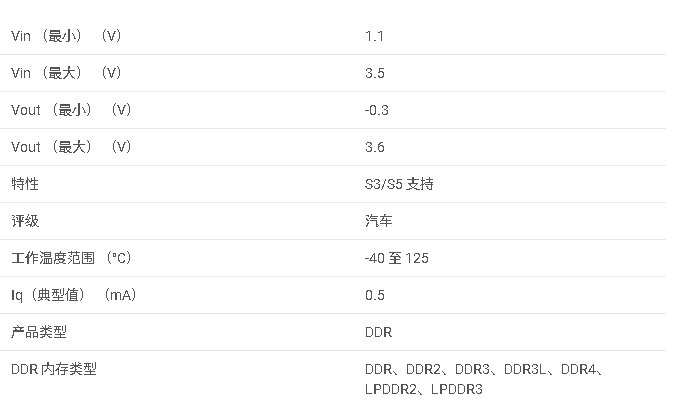

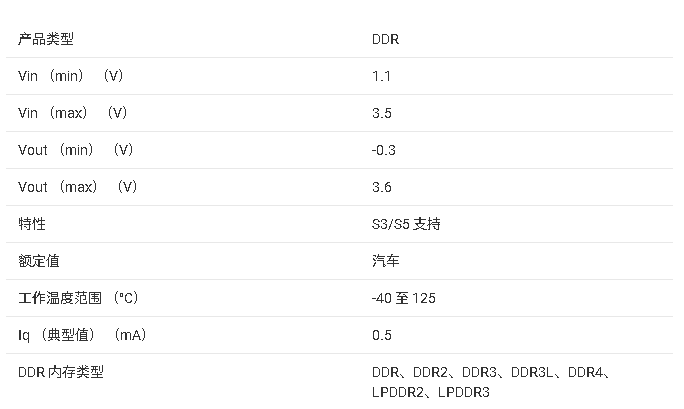

20 μF。该器件支持遥感功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 总线端接的所有电源要求。

2025-09-09 14:28:07 713

713

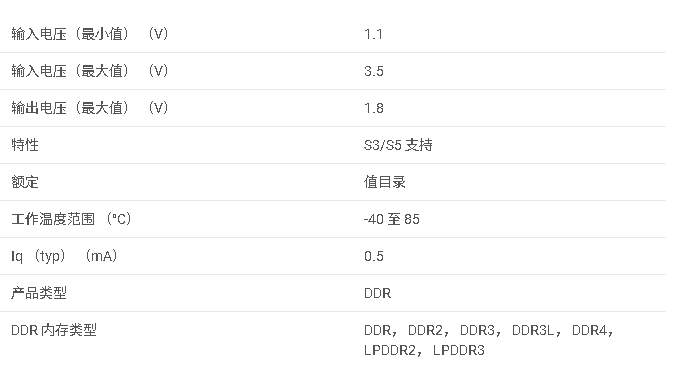

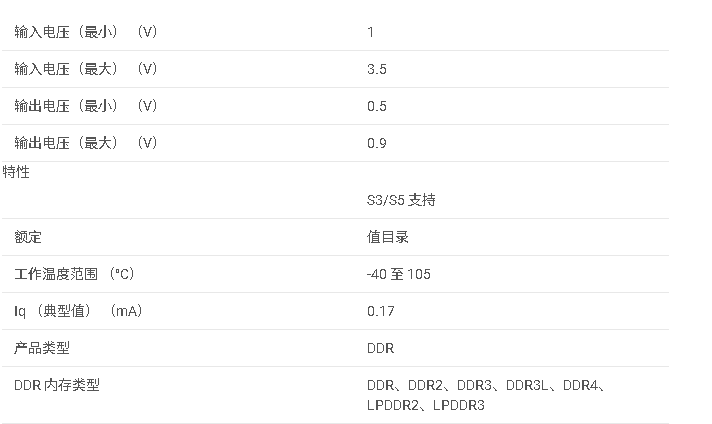

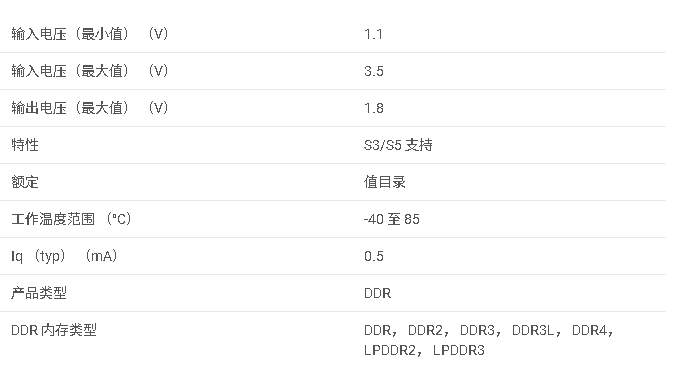

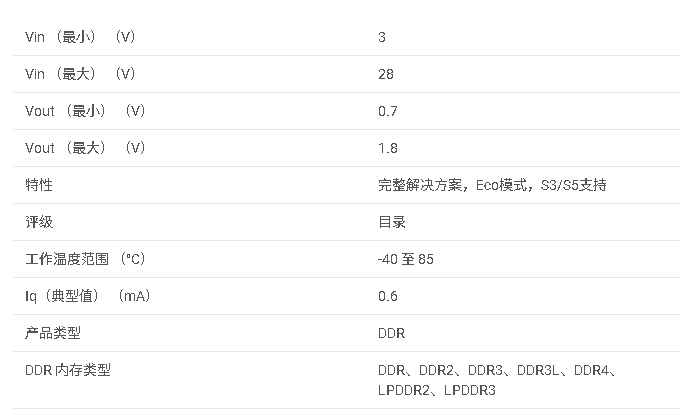

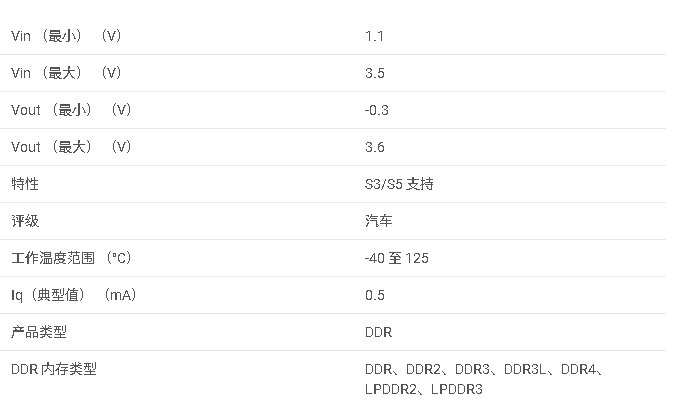

该TPS7H3302支持使用 DDR、DDR2、DDR3、DDR3L 和 DDR4 的 DDR VTT 端接应用。TPS7H3302 VTT 稳压器的快速瞬态响应允许在读/写条件下提供非常稳定的电源

2025-09-09 13:48:37 756

756

很多现在都在建设标准化考场,标准化考场究竟是什么呢?

2025-09-05 16:45:58 1228

1228

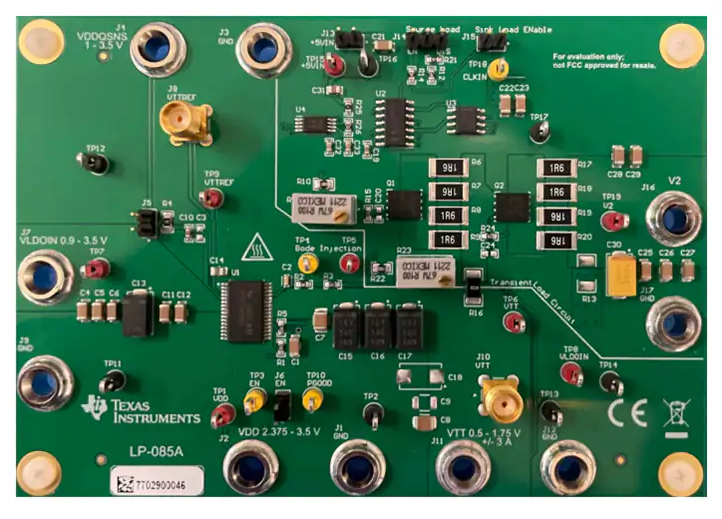

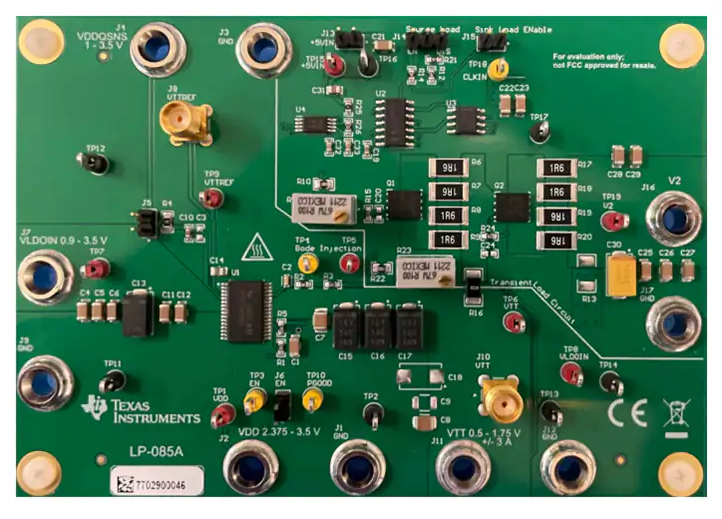

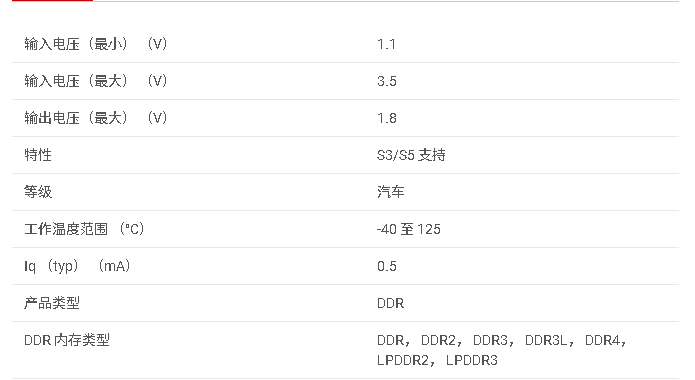

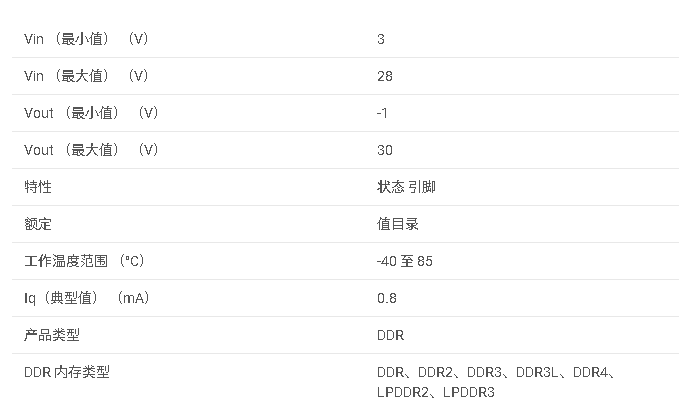

3A,支持测试DDR、DDR2、 DDR3、DDR3L和DDR4。该评估模块配有方便的测试点和跳线,用于评估TPS7H3302-SEP DDR端子。TPS7H3302EVM评估模块非常适合用于抗辐射DDR电源应用以及用于DDR、DDR2、DDR3和DDR4的存储器终端稳压器。

2025-08-27 16:14:21 833

833

凭借与紫光国芯的紧密合作,贞光科技能够为客户提供DDR3、LPDDR4及LPDDR4X全系列车规级存储产品。在产品覆盖、技术支持和供应保障等方面的综合优势,使贞光科技成为车载电子领域可靠且高效

2025-08-26 16:12:15 1430

1430

无人机在天空中自由穿梭、稳稳悬停,背后究竟是什么在发挥关键作用呢?这就不得不提到一个重要部件 ——IMU。

2025-08-12 14:27:24 1264

1264 在现代制造业中,数控机床的应用极为广泛,其加工精度直接影响着产品的质量和性能。而多摩川高分辨率编码器的出现,为数控机床的超精密运动控制带来了新的突破。那么,它究竟是如何实现这一赋能的呢?让我们一探究竟。

2025-08-04 17:59:29 887

887 本文紧接着前一个文档《AD设计DDR3时等长设计技巧-数据线等长 》。本文着重讲解DDR地址线、控制信号线等长设计,因为地址线、控制信号线有分支,SOC有可能带有2片DDR或者更多,我们叫做T型分支

2025-07-29 16:14:51 2

2 的讲解数据线等长设计。 在另一个文件《AD设计DDR3时等长设计技巧-地址线T型等长》中着重讲解使用AD设计DDR地址线走线T型走线等长处理的方法和技巧。

2025-07-28 16:33:12 4

4 技术手册,适用于使用LogiCORE IP核(如DDR3/DDR2 SDRAM、RLDRAM II、QDRII+)进行存储器接口设计26。核心功能:IP核配置与时序:详细说明Xilinx MIG(Memory Interface Generator)IP核的使用方法,包括信号定义、时序约束、物理层(PHY

2025-07-28 16:17:45 3

3 ASIC设计服务暨IP研发领导厂商智原科技(Faraday Technology Corporation)宣布推出可支持第三至第五代DDR/LPDDR的通用物理层IP,适用于联电(UMC)22ULP

2025-07-25 16:41:25 939

939 Training

DDR3 最快速率达 1066 Mbps

3.工程说明

PDS 安装后,需手动添加 DDR3 IP,请按以下步骤完成:

DDR3 IP 文件:PG2L_IP\\\\PG2L_IP

2025-07-10 10:46:48

站在战略升级的关键节点,闻泰科技正在全力聚焦半导体业务,开启全新发展阶段。值此之际,公司特别推出 《探秘“芯”世界》系列专题,邀您一同探索半导体的奥秘,见证闻泰科技以创新引领行业的 "芯" 力量。

2025-07-09 11:42:19 1137

1137 。

src\\\\DDR3\\\\DDR3ControllerGWTopLite.v: DDR3内存控制器IP核。它将AXI总线协议转换为DDR3芯片能理解的底层读写命令。

src\\\\DDR3

2025-07-06 15:18:53

实现将SC130GS采集的黑白图像数据缓存进DDR3,并以1024600@60的视频时序输出到LVDS

屏幕显示。其中,DDR3工作频率为600MHz,SC130GS输入的图像数据大小为

2025-07-02 10:26:48

DDR内存占据主导地位。全球DDR内存市场正经历一场前所未有的价格风暴。由于原厂加速退出DDR3/DDR4市场,转向DDR5和HBM(高带宽内存)生产,DDR3和DDR4市场呈现供不应求、供需失衡、涨势延续的局面。未来,DDR5渗透率将呈现快速提升,市场份额增长的趋势。

2025-06-25 11:21:15 2013

2013

turbo译码器IP核,控制接口配置了flush、standard、size,输入接口送的是编码后量化的数据,因为编码输出的是1bit(0或1),量化为5位有符号数,小数部分配0,对应fix8_3

2025-06-23 17:39:24

随着汽车产业向智能化、网联化加速转型,高级驾驶辅助系统(ADAS)和智能驾驶技术已成为现代汽车不可或缺的核心组件。紫光国芯作为国内领先的存储器芯片制造商,其车规级DDR3存储产品在智能驾驶和ADAS

2025-06-05 16:50:17 1225

1225

物理层的位置,一种是物理层在JESD204 IP里;另外一种是物理层在JESD204 IP外部,需要再配置JESD204 phy IP核进行使用。

2025-05-24 15:05:00 1827

1827

ADC 江湖风云变幻,局势不断升级,紧张刺激!究竟是内置 ADC 更胜一筹还是外置 ADC 棋高一着?

2025-05-14 15:24:42 1309

1309 楷登电子(美国 Cadence 公司,NASDAQ:CDNS)近日宣布率先推出基于台积公司 N3 工艺的 DDR5 12.8Gbps MRDIMM Gen2 内存 IP 解决方案。该新解决方案可满足

2025-05-09 16:37:44 905

905 学习FOC电机控制究竟是学哪些内容?

电机知识

软件知识

纯分享贴,有需要可以直接下载附件获取完整资料!

(如果内容有帮助可以关注、点赞、评论支持一下哦~)

2025-05-09 14:09:43

继电保护是电力系统中的“安全卫士”,其核心任务是快速检测故障并隔离故障区域,确保电力设备免遭损坏、防止停电范围扩大,同时维护电网的稳定运行。在现代电力系统中,继电保护装置如同人体的免疫系统,能够在毫秒级时间内识别异常并采取行动,是保障供电安全的核心技术之一。

一、继电保护的四大核心功能

故障检测

实时监测电流、电压、频率等电气参数,精准识别短路、过载、接地故障等异常状态。例如:

短路故障:电流骤增至正常值的数倍至数十倍。

接地故障:中性点电压偏移或零序电流异常。

故障隔离

通过控制断路器在20-100毫秒内切断故障线路,避免故障蔓延。例如:

输电线路发生短路时,距离保护装置可迅速定位故障点并跳闸。

告警与记录

触发声光报警,并记录故障波形、动作时间等数据,为后续故障分析提供依据。

系统自愈支持

配合自动化设备(如重合闸装置),在故障清除后尝试恢复供电,减少停电时间。

二、继电保护的组成与工作原理

系统架构

组件

功能

测量元件

采集电流互感器(CT)、电压互感器(PT)信号

逻辑判断单元

分析参数是否符合故障特征(如过流、差动)

执行元件

驱动断路器或发信装置动作

典型保护原理

过电流保护:检测电流超过设定阈值(如1.2倍额定电流),适用于配电网线路。

差动保护:比较设备两端电流差值,若差值超限则判定内部故障(常用于变压器、发电机)。

距离保护:通过阻抗计算定位故障点位置,适用于长距离输电线路。

三、继电保护的应用场景

发电环节

发电机保护:定子接地保护、转子过负荷保护、失磁保护等。

案例:某水电站因差动保护动作,0.1秒内隔离发电机内部短路,避免机组烧毁。

输电与变电环节

输电线路:纵联保护、光纤差动保护,保障跨区域电网安全。

变压器:瓦斯保护(非电量)、比率制动差动保护,防止绝缘油分解或绕组故障。

配电环节

配网馈线:过流保护配合自动重合闸,减少用户停电时间。

数据:90%的配电故障可在300毫秒内隔离并恢复供电。

四、继电保护的技术演进

从电磁式到数字化

早期电磁继电器:依靠机械触点动作,响应速度慢(>100ms),维护频繁。

微机保护装置:集成DSP芯片,支持多判据融合计算,动作时间缩短至20ms以内。

智能化升级

广域保护系统:基于5G通信实时共享电网状态,实现跨区域协同控制。

AI故障预测:利用机器学习分析历史数据,提前预警绝缘老化风险。

挑战与突破

新能源并网:光伏、风电的波动性要求保护装置具备自适应能力。

解决方案:引入“方向性过流保护”应对分布式电源双向电流冲击。

五、总结

继电保护是电力系统安全运行的基石,其价值体现在三个方面:

经济性:减少设备损坏带来的巨额维修成本(如一台500kV变压器损坏损失超千万元)。

可靠性:保障99.99%以上的供电可用性,支撑现代社会稳定运转。

智能化:随着数字孪生、边缘计算等技术的融合,继电保护正从“被动响应”迈向“主动防御”。

未来,继电保护将与能源互联网深度结合,成为构建新型电力系统的核心防线。

2025-05-06 10:32:41

下面是调用的DDR3模块的,模块的倒数第二行是,模块的时钟输入,时钟源来自PLL产生的系统时钟的倍频。

2025-05-03 10:21:00 1339

1339

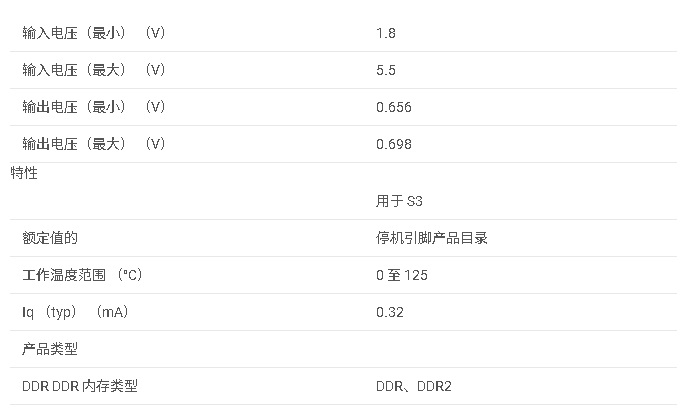

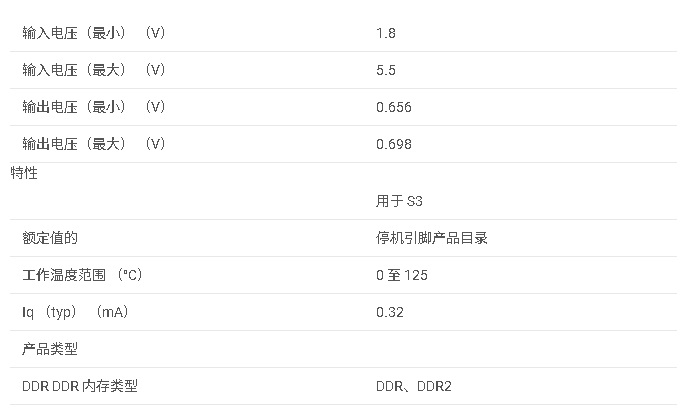

LP2996-N 和 LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 标准 DDR-SDRAM 终止规范。该器件还支持 DDR2,而 LP2996A 支持 DDR3 和 DDR3

2025-04-29 18:11:05 834

834

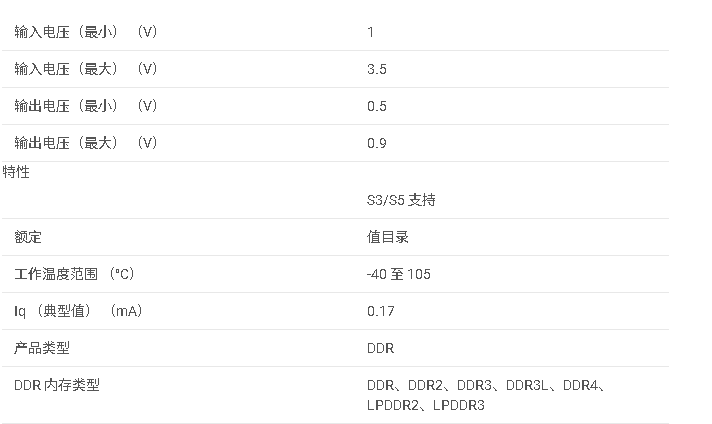

终端供电。这 该器件还支持 DDR3 VTT 端接,VDDQ 电压为 1.5 V(典型值)。此外,TPS51100 包括集成的睡眠状态控制、在 S3 中将 VTT 置于 Hi-Z(暂停到 RAM)和软

2025-04-29 17:15:20 774

774

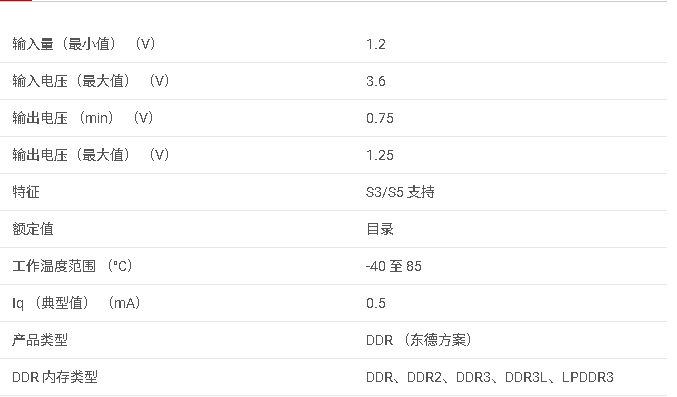

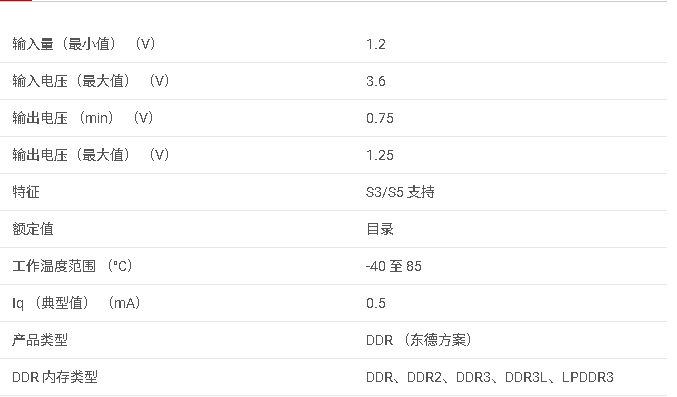

TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 内存系统提供完整的电源。它将同步降压控制器与 3A 灌电流/拉

2025-04-29 16:38:02 1031

1031

在高速PCB设计中,DDR模块是绝对绕不过去的一关。无论你用的是DDR、DDR2还是DDR3,只要设计不规范,后果就是——信号反射、时序混乱、系统频繁死机。

2025-04-29 13:51:03 2491

2491

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-29 11:34:59 810

810

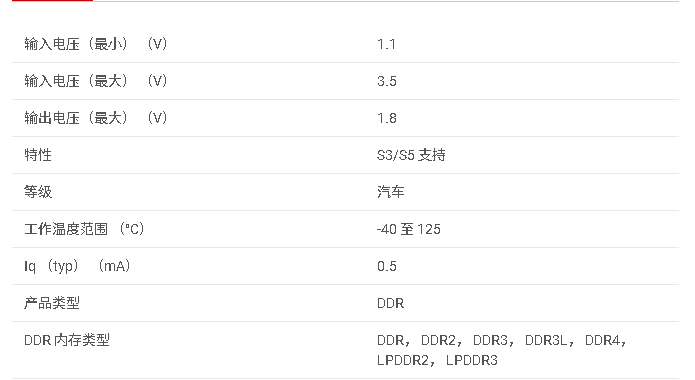

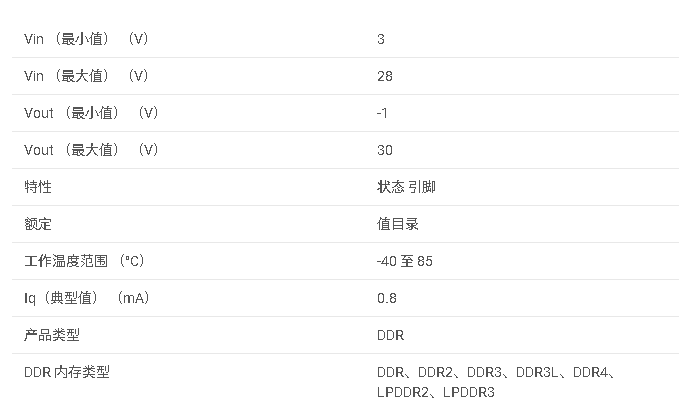

仅为 20 μF。该TPS51200支持远程感应功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

2025-04-29 09:59:25 1345

1345

只需要 20 μF 的最小输出电容。TPS51200-Q1 器件支持远程感应功能以及 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

2025-04-28 16:21:07 852

852

TPS59116 为 DDR/SSTL-2、DDR2/SSTL-18 和 DDR3 内存提供完整的电源 系统。它将同步降压控制器与 3A 灌电流/拉电流跟踪线性稳压器和缓冲低噪声基准集成在一起

2025-04-28 13:54:45 814

814

TPS51216 以最低的总成本和最小的空间为 DDR2、DDR3 和 DDR3L 内存系统提供完整的电源。它将同步降压稳压控制器 (VDDQ) 与 2A 灌/拉跟踪 LDO (VTT) 和缓

2025-04-28 11:09:05 663

663

TPS51916 器件以最低的总成本和最小的空间为 DDR2、DDR3、DDR3L 和 DDR4 内存系统提供完整的电源。它集成了同步降压稳压控制器 (VDDQ),具有 2A 灌电流和 2A 源跟踪 LDO (VTT) 和缓冲低噪声基准 (VTTREF)。

2025-04-28 10:58:44 657

657

快速瞬态响应,并且只需要 1 × 10μF 的陶瓷输出电容。该器件支持远程感应功能以及 DDR2、DDR3 和低功耗 DDR3 (DDR3L) 以及 DDR4 VTT 总线的所有电源要求。VTT 电流

2025-04-28 10:04:48 685

685

TPS51116为 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、 和 LPDDR3 内存系统。它将同步降压控制器与 1A 灌电流/拉电流集成在一起 跟踪线性稳压器和缓

2025-04-27 13:35:32 741

741

TPS51716为 DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 提供完整的电源 以最低的总成本和最小空间实现内存系统。它集成了一个同步降压 具有 2A 灌电流/拉电流跟踪 LDO

2025-04-27 11:36:05 763

763

LP2998 线性稳压器旨在满足 JEDEC SSTL-2 和 JEDEC SSTL-18 标准 DDR-SDRAM 和 DDR2 内存终止的规范。该器件还支持 DDR3 和 DDR3L VTT

2025-04-27 09:40:04 874

874

LP2996A 线性稳压器旨在满足 JEDEC SSTL-2 规范 DDR-SDRAM 终止。该器件还支持 DDR2、DDR3 和 DDR3L VTT 总线端接,带 V~DDQ~最小为 1.35V

2025-04-26 15:02:50 746

746

TPS51216-EP 以最低的总成本和最小的空间为 DDR2、DDR3 和 DDR3L 内存系统提供完整的电源。它将同步降压稳压控制器 (VDDQ) 与 2A 灌/拉跟踪 LDO (VTT) 和缓

2025-04-26 11:12:30 681

681

只需要最小输出 电容为 20 μF。TPS51200-EP 支持遥感功能和所有功率要求 用于 DDR、DDR2、DDR3、低功耗 DDR3 和 DDR4 VTT 总线终端。

2025-04-26 10:26:35 1335

1335

的最小输出电容。该器件支持远程感应功能以及 DDR、DDR2、DDR3 以及低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

2025-04-25 10:07:15 1054

1054

在全球科技竞争加剧、国产替代加速推进的背景下,紫光国芯凭借其在DDR3与RDIMM等高端内存芯片领域的技术积累,不断实现突破,推动国产存储芯片向高端市场迈进。作为其核心代理商,贞光科技在市场推广

2025-04-16 16:39:30 1343

1343

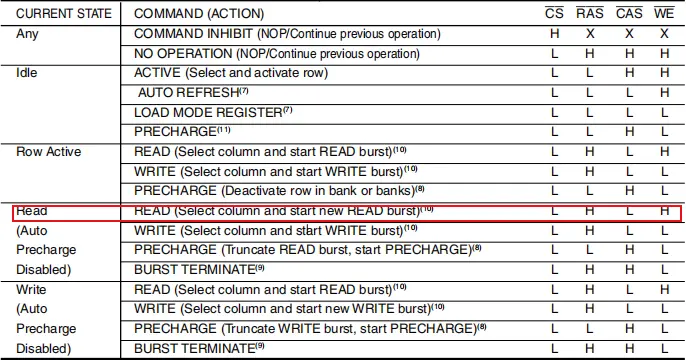

DDR3 SDRAM(Double-Data-Rate ThreeSynchronous Dynamic Random Access Memory)是DDR SDRAM的第三代产品,相较于DDR2,DDR3有更高的运行性能与更低的电压。

2025-04-10 09:42:53 3930

3930

Video In to AXI4-Stream IP核用于将视频源(带有同步信号的时钟并行视频数据,即同步sync或消隐blank信号或者而后者皆有)转换成AXI4-Stream接口形式,实现了接口转换。该IP还可使用VTC核,VTC在视频输入和视频处理之间起桥梁作用。

2025-04-03 09:28:14 2418

2418

我们目前正在使用 iMX6UL DDR 寄存器编程辅助工具为 U-Boot 生成 DCD 表。我们的设备使用的是 MT41K128M16JT-107,即 DDR3-1866,这意味着它的时钟周期频率

2025-03-27 07:16:35

灿芯半导体(上海)股份有限公司(灿芯股份,688691)宣布推出基于28HKD 0.9V/2.5V 平台的DDR3/4, LPDDR3/4 Combo IP。该IP具备广泛的协议兼容性,支持DDR3

2025-03-21 16:20:03 984

984 初次使用XC7A35T-FGG484做设计,用的是25MHZ有源晶振,有源晶振3.3V供电,DDR3的供电1.35V,现在接上晶振后,DDR3的供电变成1.8V

求助怎么解决。

2025-03-21 14:25:05

很多工程师在产品选型的时候会疑惑,究竟是选CAN接口卡还是CANFD接口卡呢?两者之间有什么区别呢?影响选择的关键因素又是什么?我们今天一个一个来拆解。1.波特率传统的CAN接口卡仅有一个波特率,即

2025-03-21 11:37:40 790

790

在日常生活中,我们可能很少直接接触到气密性检测仪,但在工业生产、汽车制造、医疗器械等领域,它却是不可或缺的"神器"。那么,这个看似神秘的设备究竟是如何工作的?它又是如何精准

2025-03-15 16:13:23 1047

1047

那么,究竟是什么促使创作者们选择了Dell PowerScale?而它所具备的特性又能为影视行业带来怎样的价值呢?

2025-03-07 14:57:22 1029

1029 如下图所示,这个二极管是做什么的呢?欢迎大家交流。

2025-03-06 07:00:47

,如图电路;

结果发现在3.3V这一侧,也就是RXD位置还是测到毛刺;

有谁知道这究竟是为什么吗?

2025-03-06 06:24:41

DDR内存控制器是一个高度集成的组件,支持多种DDR内存类型(DDR2、DDR3、DDR3L、LPDDR2),并通过精心设计的架构来优化内存访问效率。

2025-03-05 13:47:40 3573

3573

Xilinx的FIR IP核属于收费IP,但是不需要像 Quartus那样通过修改license文件来破解。如果是个人学习,现在网络上流传的license破解文件在破解Vivado的同时也破解

2025-03-01 14:44:19 2709

2709

世界移动通信大会展示了最前沿的无线产品和技术,汇聚了有史以来最先进的一些通信设备。但究竟是什么保证了这些设备在现实环境中每次都能无缝运行呢?

2025-02-25 16:43:39 884

884 生效,IO不会有高电平输出

如果步骤3、4 之间增加一点点延时,sleep(10),Trigger Out 1才可以生效。

该问题在我们以前的板子上不存在,最近生产的板子才出现,所以想查出究竟是哪里的问题? 配置 Write Operating Mode Select 后,一般需要delay多长时间?

2025-02-21 07:23:59

据报道,业内人士透露,全球三大DRAM内存制造商——三星电子、SK海力士和美光,有望在2025年内正式停产已有多年历史的DDR3和DDR4两代内存。 随着技术的不断进步和消费级平台的更新换代

2025-02-19 11:11:51 3465

3465 作为物联网智能硬件的引领者,云里物里当然不是来聊电影的,而是想借此机会,和大家探讨一下:室内导航究竟是如何实现的?它背后的技术原理是什么?接下来,让我们一起揭开室内导航的神秘面纱。

2025-02-12 13:50:31 961

961

PACE_OUT1和PACE_OUT2这两条引腿究竟是输入还是输出?有什么用?怎样使用?

2025-02-12 07:56:43

;MTA9ASF1G72AZ-3G2R1是一款高性能的DDR3 SDRAM内存模块,专为满足现代计算需求而设计。该产品以其高带宽和低功耗的特性,广泛应用于个人电脑、服务器和嵌入式系统中,成为市场上备

2025-02-10 20:10:39

板子上正负10V电压已加,USBStyx driver 已经安装,通过母板供电,但最后 软件界面上的Acquire 按键呈现灰白色,无法按下,如下图红圈区域所示:

有哪位能告诉我究竟是哪里出了问题?该不会是硬件坏了吧?

2025-01-22 07:54:30

) ADC 和片上传感器。其中12位指的是ADC转换的精度,1MSPS说的是采样速率。如图所示,是XADC在FPGA内部电路的逻辑示意,注意区别于IP核形成的电路。 1.图中1部分是温度传感器和电压传感器,可监测如图所示的多组电压。 2.图中2部分是FPGA bank上的引脚。可以用来接模拟源,总共有

2025-01-15 16:53:59 2235

2235

ALINX近日宣布,基于AMD 100G以太网MAC IP,成功开发出全新的100G以太网UDP/IP协议栈IP核。该IP核在数据传输方面表现出色,MTU支持高达9000Bytes,采用标准

2025-01-07 11:25:25 1254

1254 AI工作流自动化是指利用人工智能技术,对工作流程中的重复性、规则明确的任务进行自动化处理的过程。那么,AI工作流自动化是做什么的呢?接下来,AI部落小编为您分享。

2025-01-06 17:57:59 1581

1581

电子发烧友App

电子发烧友App

评论