在高速PCB设计中,DDR模块是绝对绕不过去的一关。无论你用的是DDR、DDR2还是DDR3,只要设计不规范,后果就是——信号反射、时序混乱、系统频繁死机。

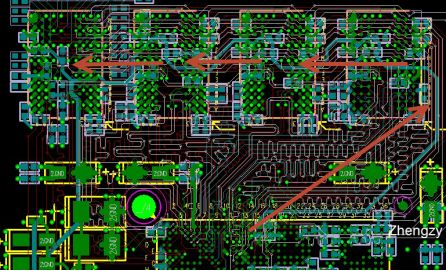

今天这篇文章,我们就围绕DDR的PCB设计要点,从定义、阻抗、布局拓扑、走线控制等核心问题,结合实际工程图示,为你一次讲透!

01 什么是DDR?

DDR(Double Data Rate)即双倍速率同步动态随机存储器。

常见规格包括:DDR、DDR2、DDR3、DDR4 等。

其核心特性是在时钟信号的上升沿和下降沿均可传输数据,因此在相同时钟频率下传输速度翻倍。

02 阻抗控制要求

DDR布线时必须严格控制阻抗,典型值如下:

单端信号线:50Ω

差分对信号:100Ω

阻抗不匹配 = 反射、失真、时序异常,不可忽视!

03 DDR布局拓扑结构设计要点

DDR布局方式随颗粒数量的不同而有所变化,合理选择拓扑结构,是PCB设计的关键之一。

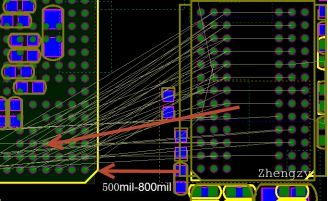

A. 单颗DDR芯片布局

采用点对点(Point-to-Point)连接方式:

芯片靠近主控器;

数据线 Bank 做到尽量对称;

间距推荐控制在 500–800mil。

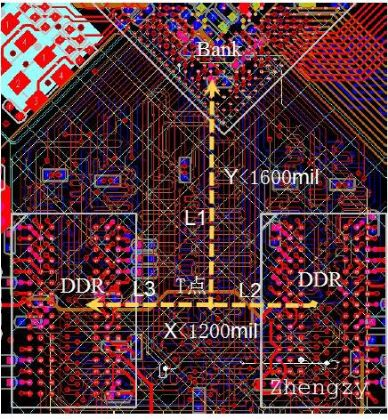

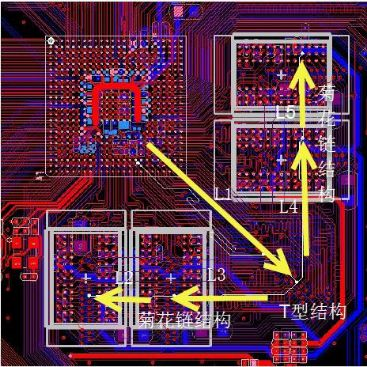

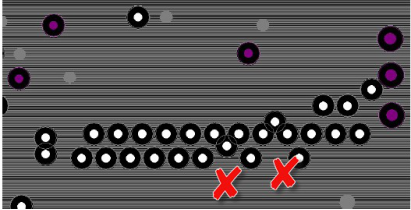

B. 双颗DDR芯片布局(图2)

推荐使用T型拓扑结构:

两颗DDR对主控飞线对称分布;

主干线段L1统一,两分支线L2、L3等长;

满足公式:L1 + L2 = L1 + L3

图中标注了飞线分布示意。

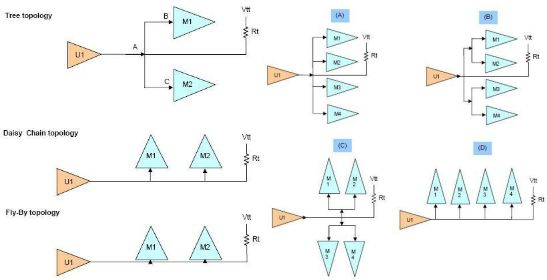

C. 四颗DDR芯片布局

常见拓扑方式有:

对称T型拓扑

分支T型拓扑

菊花链拓扑(Fly-by Structure)

其中,对于DDR3及更高频应用(如1600Mbps),推荐使用菊花链拓扑(Fly-by Topology),信号完整性更好。

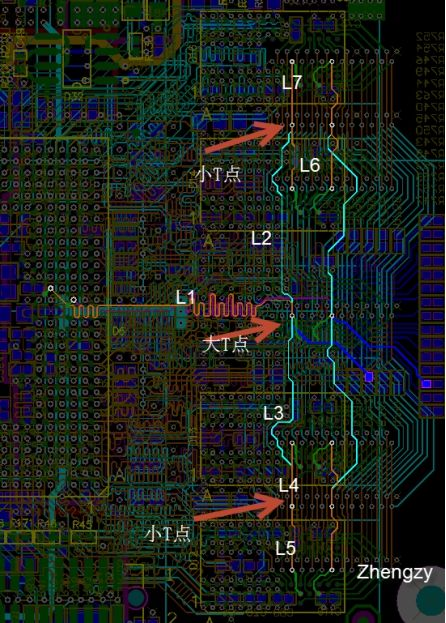

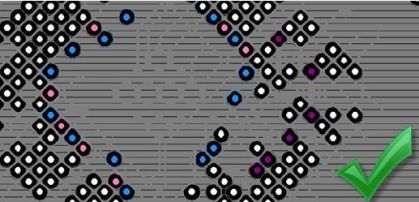

D. 混合拓扑结构

适用于PCB空间有限的情况:

将T型拓扑与Fly-by拓扑结合;

注意分支线等长控制:

等长控制公式:

L1 + L3 + L2 = L1 + L4 + L5

下图中展示了典型的混合拓扑图例。

04 信号分组与布线规范

下面我们以四片DDR3为例,讲讲信号布线中的具体控制细节。

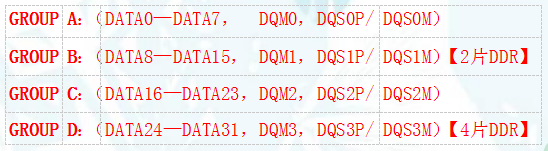

A. 信号分组划分

32条数据线(DATA0-DATA31)、4条DATA MASKS(DQM0-DQM3),4对DATA STROBES差分线(DQS0P/ DQS0M—DQS3P/DQS3M)

这36条线和4对差分线分为四组:

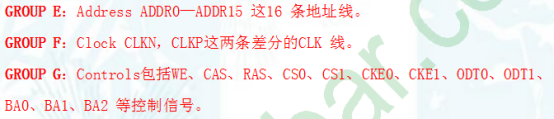

再将剩下的信号线分为三类:

Address/Command、Control与CLK归为一组,因为它们都是以CLK的下降沿由DDR控制器输出,DDR颗粒由CLK 的上升沿锁存Address/Command、Control 总线上的状态,所以需要严格控制CLK 与Address/Command、Control 之间的时序关系,确保DDR颗粒能够获得足够的、最佳的建立/保持时间。

B、误差控制

差分对对内误差尽量控制在5mil以内;数据线组内误差尽量控制在+-25mil以内,组间误差尽量控制在+-50mil以内。

Address/Command 、Control全部参照时钟进行等长,误差尽量控制在+-100mil 以内。

C、间距控制建议

数据线之间间距要满足3W原则,控制线、地址线必要时可稍微放宽到2W~3W,其他走线离时钟线20mil或至少3W以上的间距,以减小信号传输的串扰问题。

D、VERF设计要求

VERF电容需靠近管脚放置,VREF走线尽量短,且与任何数据线分开,保证其不受干扰(特别注意相邻上下层的串扰),推荐走线宽度>=15mil。

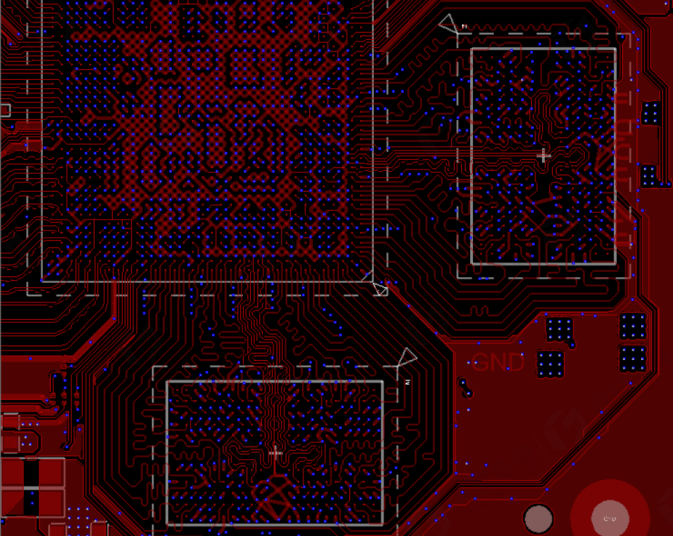

E、DDR区域参考平面规划

DDR设计区域,这个区域请保障完整的参考平面,如下方图片所示:

总结:牢记这几点,DDR设计再不翻车!

| 单端阻抗 | 50Ω |

| 差分阻抗 | 100Ω |

| 差分误差 | ≤ 5mil |

| 数据组内误差 | ±25mil |

| 数据组间误差 | ±50mil |

| Addr/Control对CLK | ±100mil |

| 间距要求 | 遵循3W原则 |

| VREF线宽 | ≥15mil |

| 区域参考层 | 保证连续完整 |

| 项目 | 推荐值或控制要求 |

|---|

本文凡亿教育原创文章,转载请注明来源!

-

存储器

+关注

关注

39文章

7756浏览量

172187 -

DDR

+关注

关注

11文章

761浏览量

69552 -

PCB设计

+关注

关注

396文章

4938浏览量

95757 -

布线

+关注

关注

9文章

835浏览量

86254

原文标题:【硬核干货】DDR模块PCB设计全解析:拓扑结构、布线规则、误差控制一个都不能少!

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【PCB设计干货】DDR电路的PCB布局布线要求

触摸按键PCB设计要点相关资料推荐

PCB设计:DDR的调试案例

【华秋干货铺】DDR电路的PCB布局布线要求

DDR模块的PCB设计要点

DDR模块的PCB设计要点

评论